UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 479 of 841

NXP Semiconductors

UM10360

Chapter 20: LPC176x/5x I2S

20.5.5 Status Feedback register (I2SSTATE - 0x400A 8010)

The I2SSTATE register provides status information about the I

2

S interface. The meaning

of bits in I2SSTATE are shown in Table 409

.

20.5.6 DMA Configuration Register 1 (I2SDMA1 - 0x400A 8014)

The I2SDMA1 register controls the operation of DMA request 1. The function of bits in

I2SDMA1 are shown in Table 410

. Refer to the General Purpose DMA Controller chapter

for details of DMA operation.

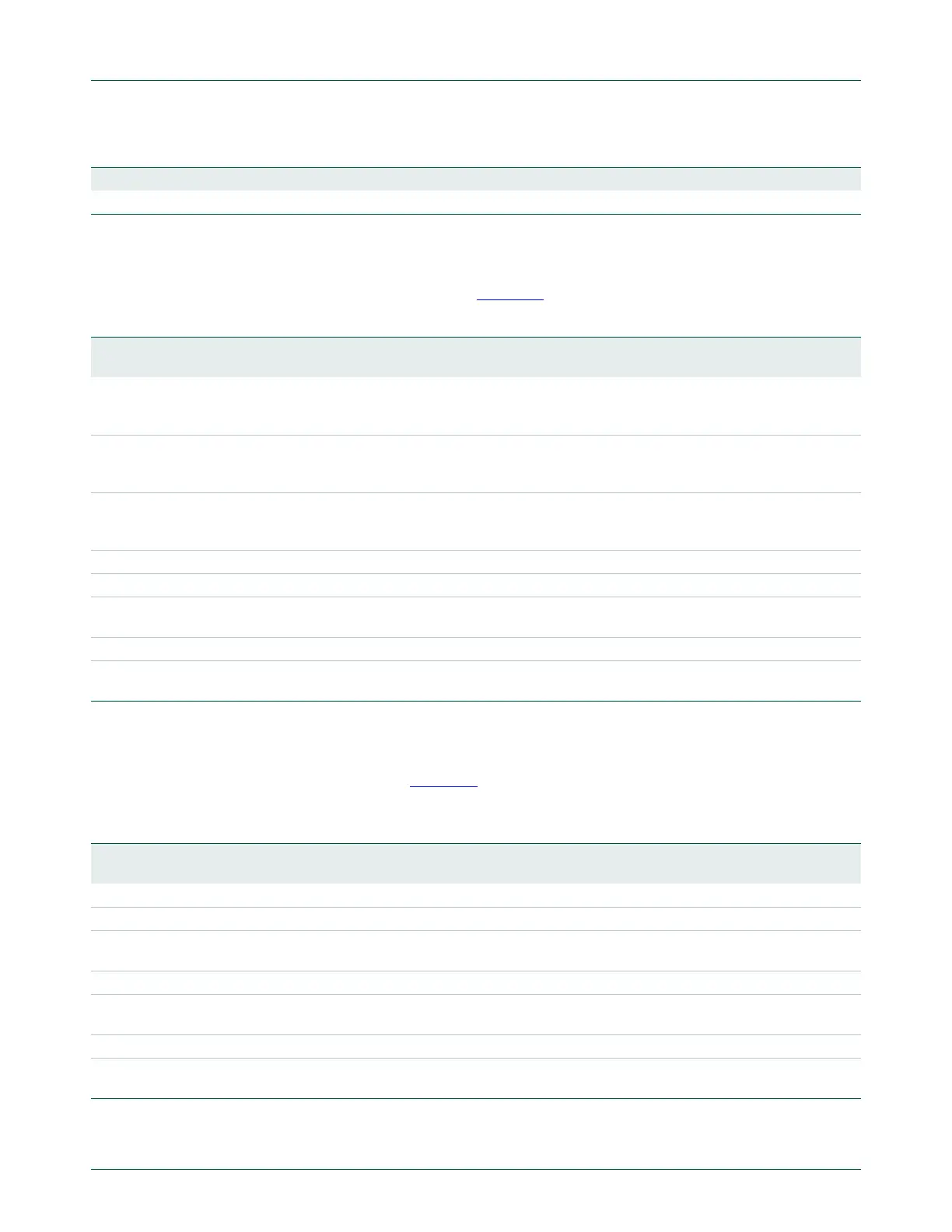

Table 408: Receive FIFO register (I2RXFIFO - address 0x400A 800C) bit description

Bit Symbol Description Reset Value

31:0 I2SRXFIFO 8 32-bit transmit FIFO. level = 0

Table 409: Status Feedback register (I2SSTATE - address 0x400A 8010) bit description

Bit Symbol Description Reset

Value

0 irq This bit reflects the presence of Receive Interrupt or Transmit Interrupt. This is determined by

comparing the current FIFO levels to the rx_depth_irq and tx_depth_irq fields in the I2SIRQ

register.

1

1 dmareq1 This bit reflects the presence of Receive or Transmit DMA Request 1. This is determined by

comparing the current FIFO levels to the rx_depth_dma1 and tx_depth_dma1 fields in the

I2SDMA1 register.

1

2 dmareq2 This bit reflects the presence of Receive or Transmit DMA Request 2. This is determined by

comparing the current FIFO levels to the rx_depth_dma2 and tx_depth_dma2 fields in the

I2SDMA2 register.

1

7:3 Unused Unused. 0

11:8 rx_level Reflects the current level of the Receive FIFO. 0

15:12 - Reserved, user software should not write ones to reserved bits. The value read from a reserved

bit is not defined.

NA

19:16 tx_level Reflects the current level of the Transmit FIFO. 0

31:20 - Reserved, user software should not write ones to reserved bits. The value read from a reserved

bit is not defined.

NA

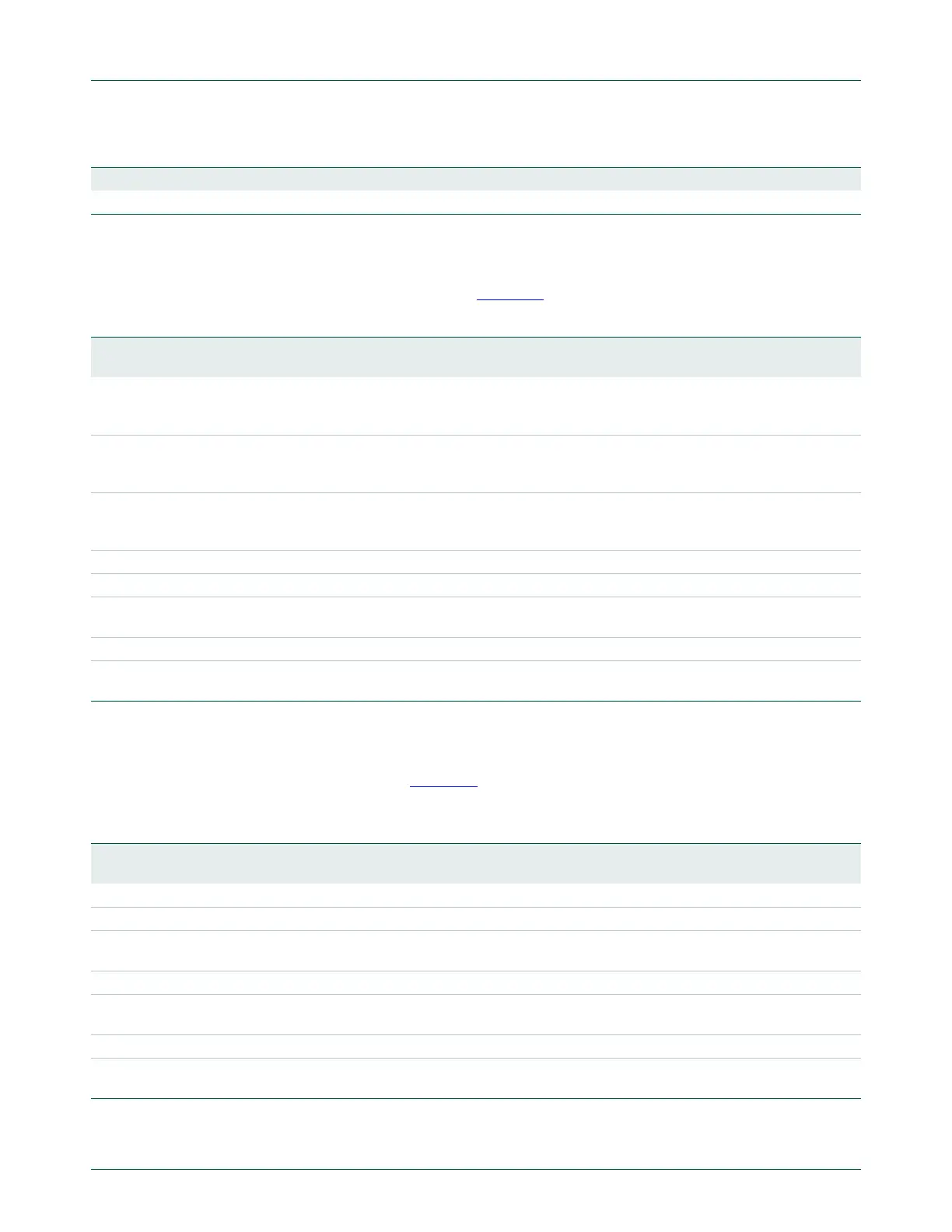

Table 410: DMA Configuration register 1 (I2SDMA1 - address 0x400A 8014) bit description

Bit Symbol Description Reset

Value

0 rx_dma1_enable When 1, enables DMA1 for I

2

S receive. 0

1 tx_dma1_enable When 1, enables DMA1 for I

2

S transmit. 0

7:2 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

0

11:8 rx_depth_dma1 Set the FIFO level that triggers a receive DMA request on DMA1. 0

15:12 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

19:16 tx_depth_dma1 Set the FIFO level that triggers a transmit DMA request on DMA1. 0

31:20 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...