UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 605 of 841

NXP Semiconductors

UM10360

Chapter 31: LPC176x/5x General Purpose DMA (GPDMA)

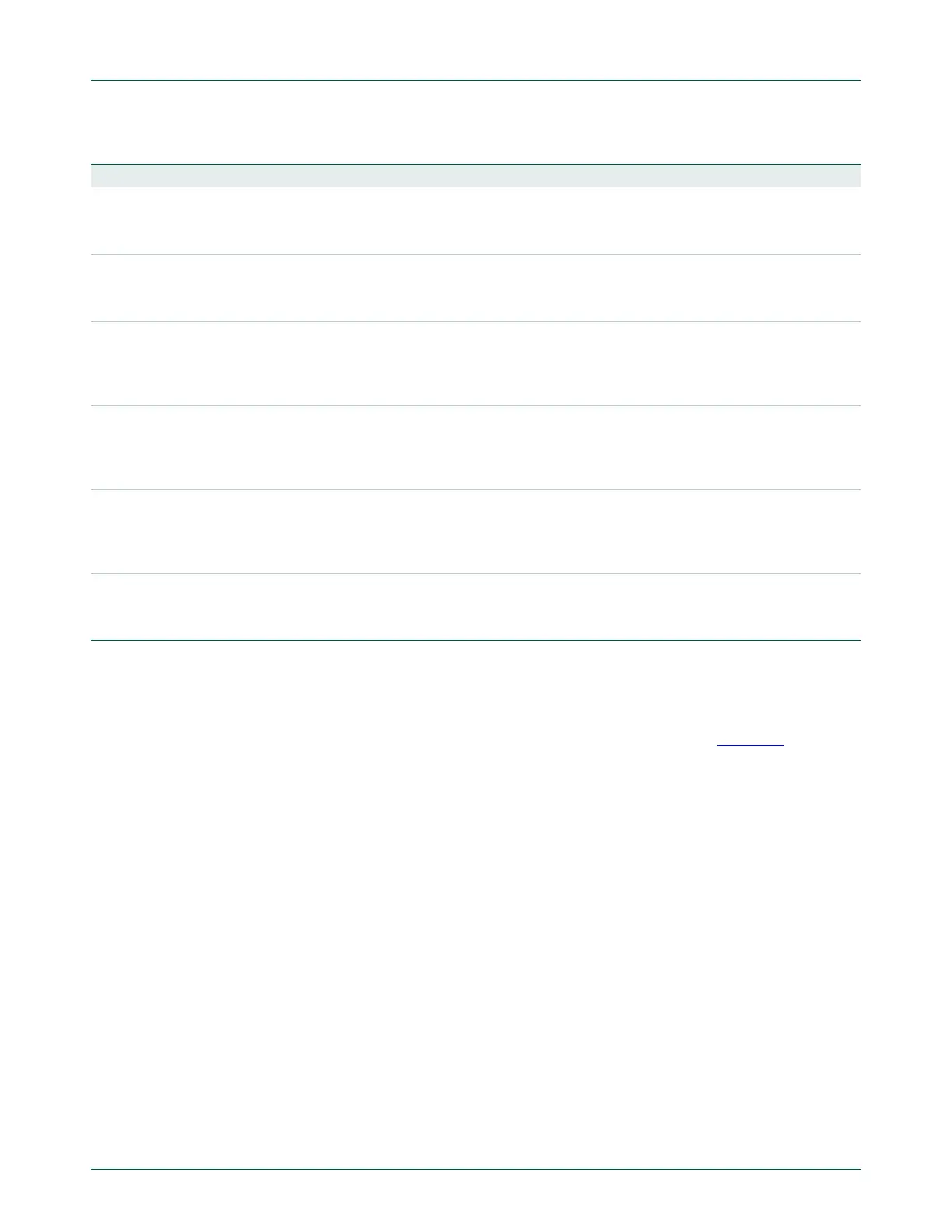

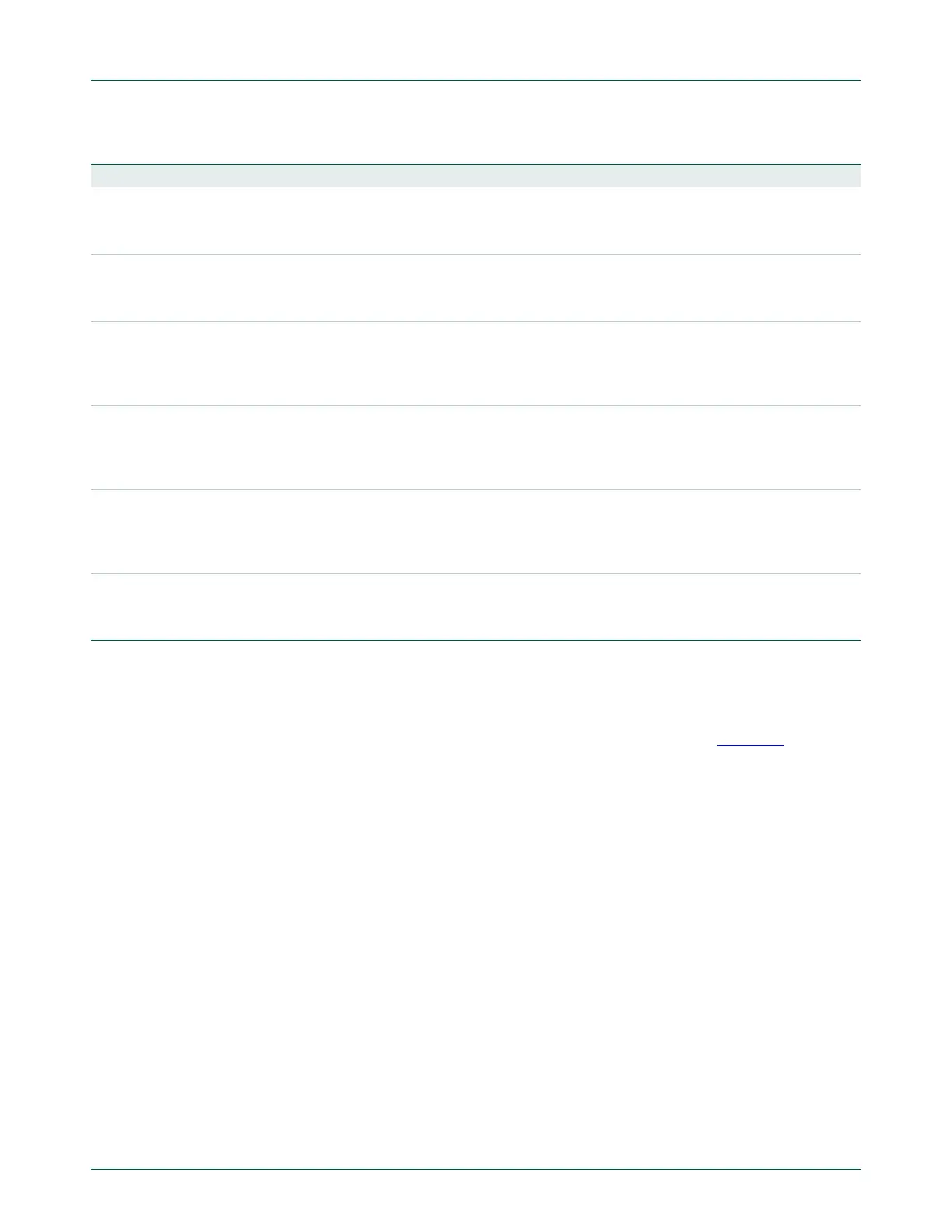

31.5.21 DMA Channel Configuration registers (DMACCxConfig - 0x5000 41x0)

The eight DMACCxConfig Registers (DMACC0Config to DMACC7Config) are read/write

with the exception of bit[17] which is read-only. These registers configure each DMA

channel. The registers are not updated when a new LLI is requested. Table 564

shows the

bit assignments of the DMACCxConfig Register.

26 SI Source increment:

0 - the source address is not incremented after each transfer.

1 - the source address is incremented after each transfer.

27 DI Destination increment:

0 - the destination address is not incremented after each transfer.

1 - the destination address is incremented after each transfer.

28 Prot1 This is provided to the peripheral during a DMA bus access and indicates that the access is in user

mode or privileged mode. This information is not used in the LPC176x/5x.

0 - access is in user mode.

1 - access is in privileged mode.

29 Prot2 This is provided to the peripheral during a DMA bus access and indicates to the peripheral that the

access is bufferable or not bufferable. This information is not used in the LPC176x/5x.

0 - access is not bufferable.

1 - access is bufferable.

30 Prot3 This is provided to the peripheral during a DMA bus access and indicates to the peripheral that the

access is cacheable or not cacheable. This information is not used in the LPC176x/5x.

0 - access is not cacheable.

1 - access is cacheable.

31 I Terminal count interrupt enable bit.

0 - the terminal count interrupt is disabled.

1 - the terminal count interrupt is enabled.

Table 563. DMA channel control registers (DMACCxControl - 0x5000 41xC)

…continued

Bit Name Function

Loading...

Loading...