UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 729 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

[1] See Table 634.

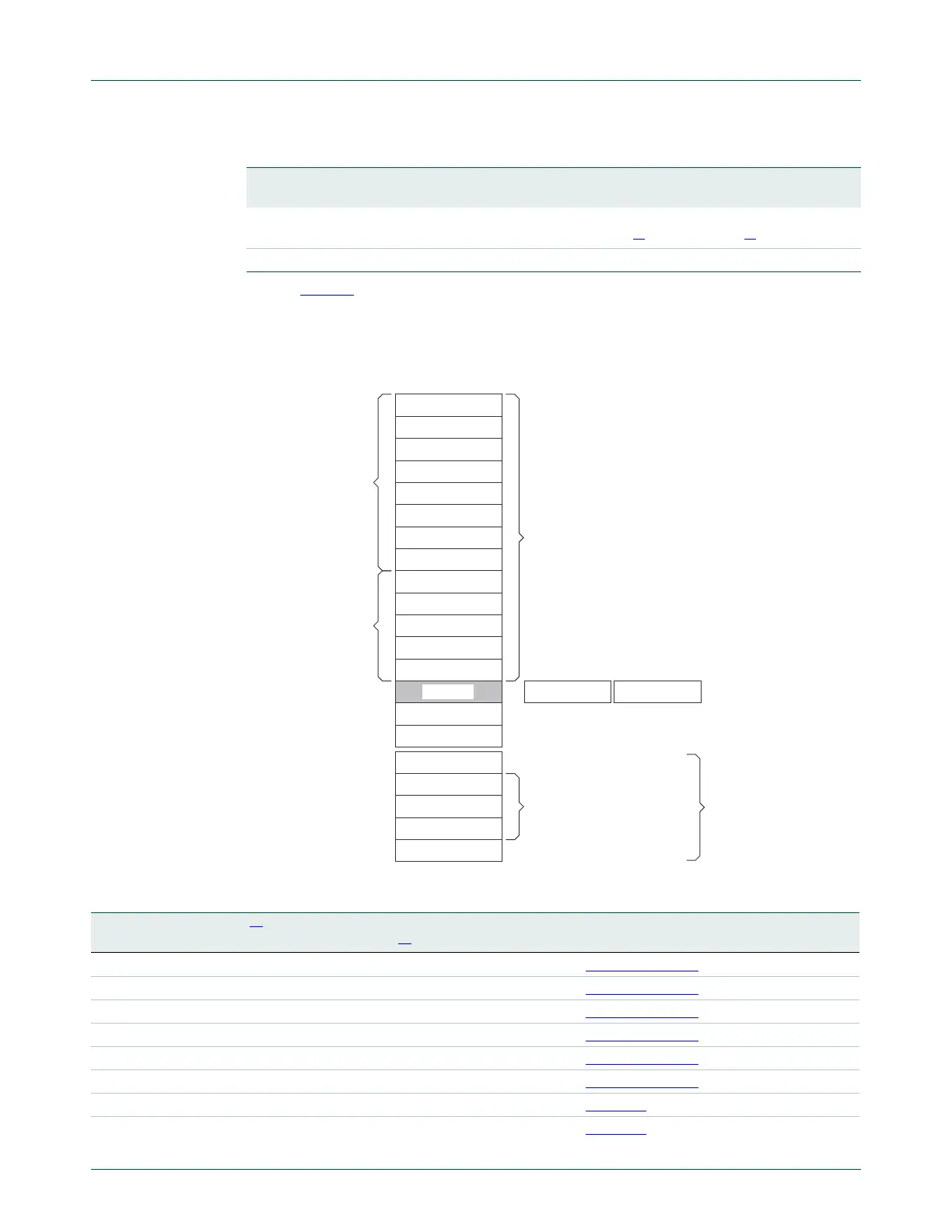

34.3.1.3 Core registers

The processor core registers are:

Table 625. Summary of processor mode, execution privilege level, and stack use options

Processor

mode

Used to

execute

Privilege level for

software execution

Stack used

Thread Applications Privileged or

unprivileged

[1]

Main stack or process

stack

[1]

Handler Exception handlers Always privileged Main stack

635

/55

3&5

5

5

5

5

5

5

5

5

5

5

5

5

5

/RZUHJLVWHUV

+LJKUHJLVWHUV

063

Á

363

Á

365

35,0$6.

)$8/70$6.

%$6(35,

&21752/

*HQHUDOSXUSRVHUHJLVWHUV

6WDFN3RLQWHU

/LQN5HJLVWHU

3URJUDP&RXQWHU

3URJUDPVWDWXVUHJLVWHU

([FHSWLRQPDVNUHJLVWHUV

&21752/UHJLVWHU

6SHFLDOUHJLVWHUV

Á

%DQNHGYHUVLRQRI63

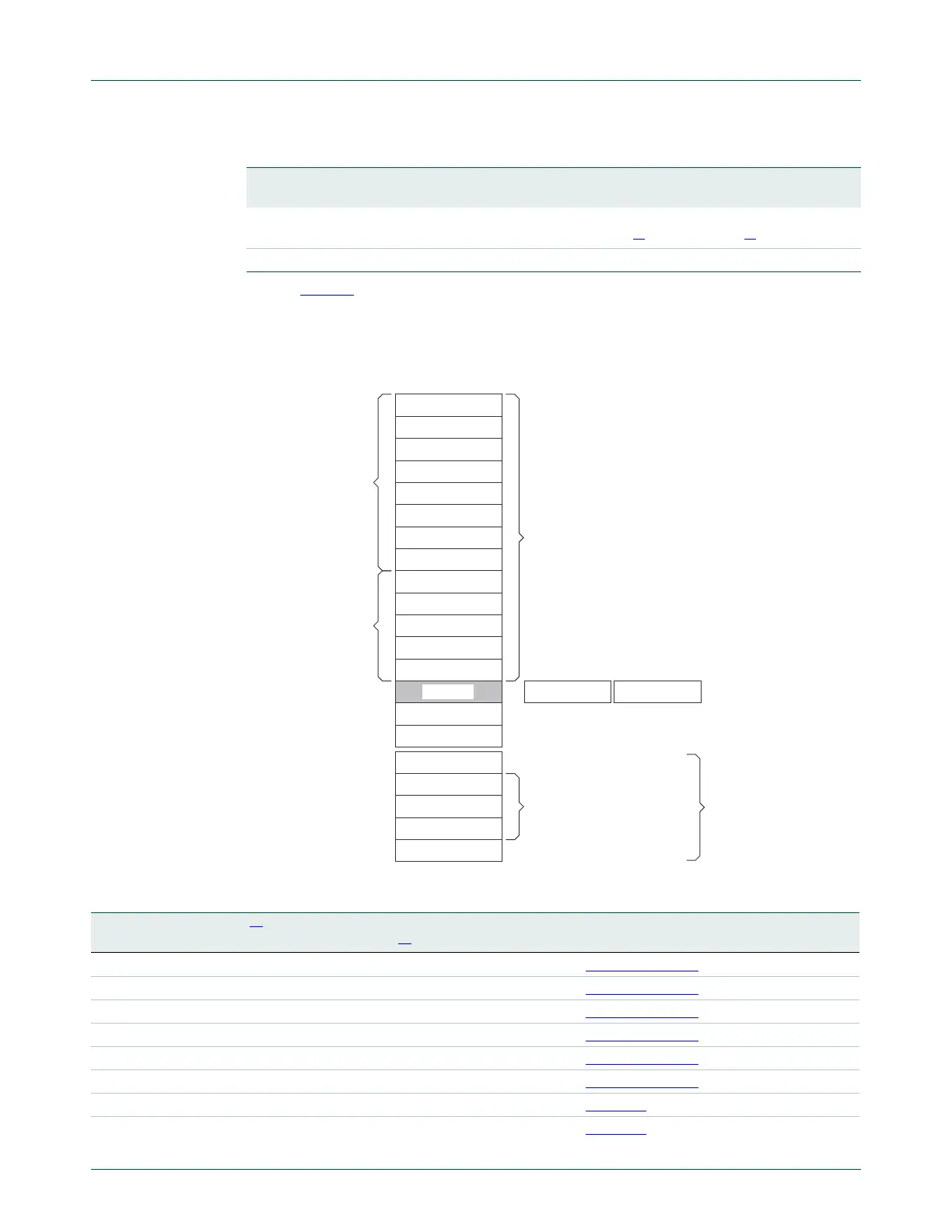

Table 626. Core register set summary

Name Type

[1]

Required

privilege

[2]

Reset

value

Description

R0-R12 RW Either Undefined Section 34.3.1.3.1

MSP RW Privileged See description Section 34.3.1.3.2

PSP RW Either Undefined Section 34.3.1.3.2

LR RW Either

0xFFFFFFFF

Section 34.3.1.3.3

PC RW Either See description Section 34.3.1.3.4

PSR RW Privileged

0x01000000

Section 34.3.1.3.5

ASPR RW Either

0x00000000

Table 628

IPSR RO Privileged

0x00000000

Table 629

Loading...

Loading...