UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 555 of 841

NXP Semiconductors

UM10360

Chapter 26: LPC176x/5x Quadrature Encoder Interface (QEI)

26.6.4 Interrupt registers

26.6.4.1 QEI Interrupt Status register (QEIINTSTAT)

This register provides the status of the encoder interface and the current set of interrupt

sources that are asserted to the controller. Bits set to 1 indicate the latched events that

have occurred; a zero bit indicates that the event in question has not occurred. Writing a 0

to a bit position clears the corresponding interrupt.

26.6.4.2 QEI Interrupt Set register (QEISET - 0x400B CFEC)

Writing a one to a bit in this register sets the corresponding bit in the QEI Interrupt Status

register (QEISTAT).

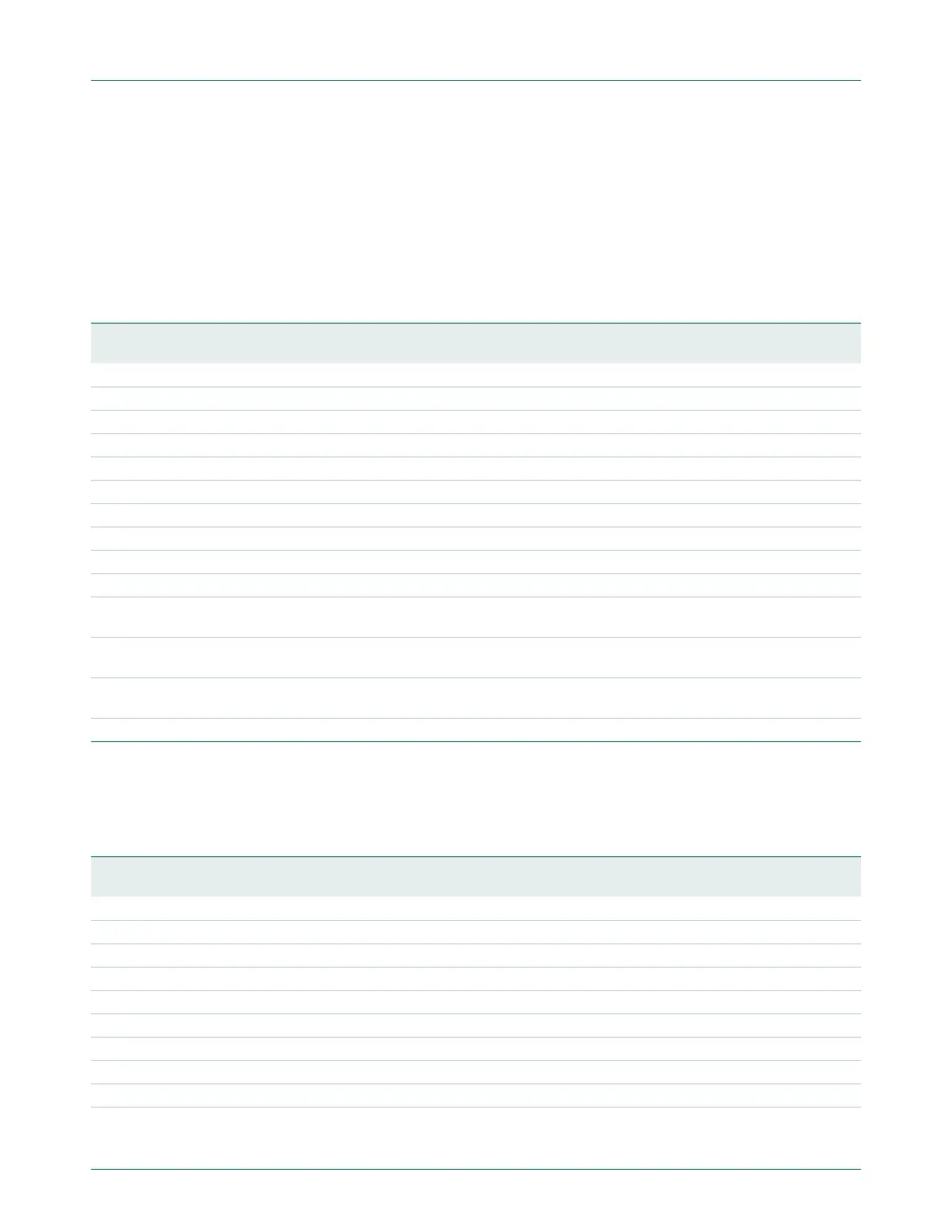

Table 500: QEI Interrupt Status register (QEIINTSTAT - address 0x400B CFE0) bit description

Bit Symbol Description Reset

value

0 INX_Int Indicates that an index pulse was detected. 0

1 TIM_Int Indicates that a velocity timer overflow occurred 0

2 VELC_Int Indicates that captured velocity is less than compare velocity. 0

3 DIR_Int Indicates that a change of direction was detected. 0

4 ERR_Int Indicates that an encoder phase error was detected. 0

5 ENCLK_Int Indicates that and encoder clock pulse was detected.

6 POS0_Int Indicates that the position 0 compare value is equal to the current position. 0

7 POS1_Int Indicates that the position 1compare value is equal to the current position. 0

8 POS2_Int Indicates that the position 2 compare value is equal to the current position. 0

9 REV_Int Indicates that the index compare value is equal to the current index count. 0

10 POS0REV_Int Combined position 0 and revolution count interrupt. Set when both the POS0_Int bit is set

and the REV_Int is set.

0

11 POS1REV_Int Combined position 1 and revolution count interrupt. Set when both the POS1_Int bit is set

and the REV_Int is set.

0

12 POS2REV_Int Combined position 2 and revolution count interrupt. Set when both the POS2_Int bit is set

and the REV_Int is set.

0

31:13 - reserved 0

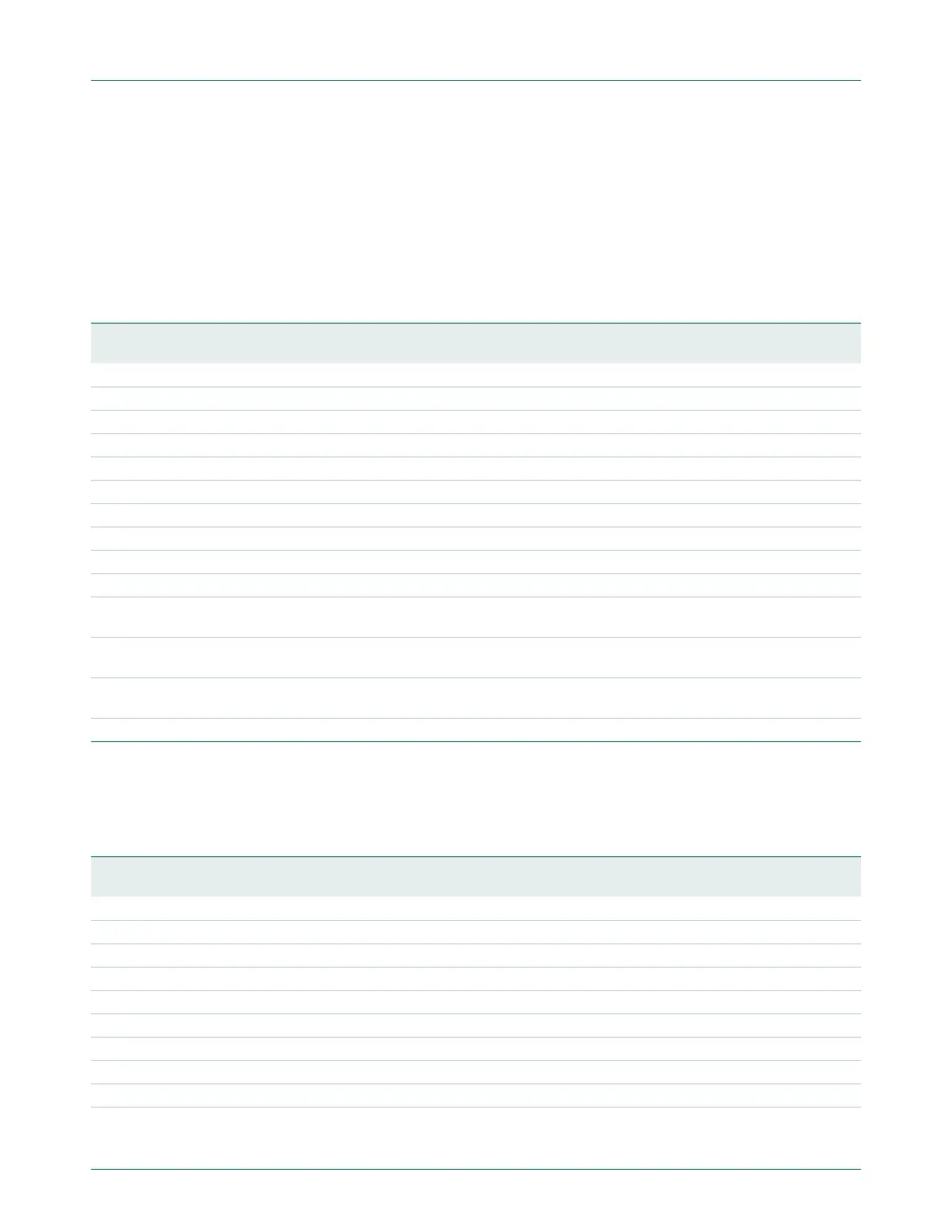

Table 501: QEI Interrupt Set register (QEISET - address 0x400B CFEC) bit description

Bit Symbol Description Reset

value

0 INX_Int Indicates that an index pulse was detected. 0

1 TIM_Int Indicates that a velocity timer overflow occurred 0

2 VELC_Int Indicates that captured velocity is less than compare velocity. 0

3 DIR_Int Indicates that a change of direction was detected. 0

4 ERR_Int Indicates that an encoder phase error was detected. 0

5 ENCLK_Int Indicates that and encoder clock pulse was detected.

6 POS0_Int Indicates that the position 0 compare value is equal to the current position. 0

7 POS1_Int Indicates that the position 1compare value is equal to the current position. 0

8 POS2_Int Indicates that the position 2 compare value is equal to the current position. 0

9 REV_Int Indicates that the index compare value is equal to the current index count. 0

Loading...

Loading...