UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 774 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

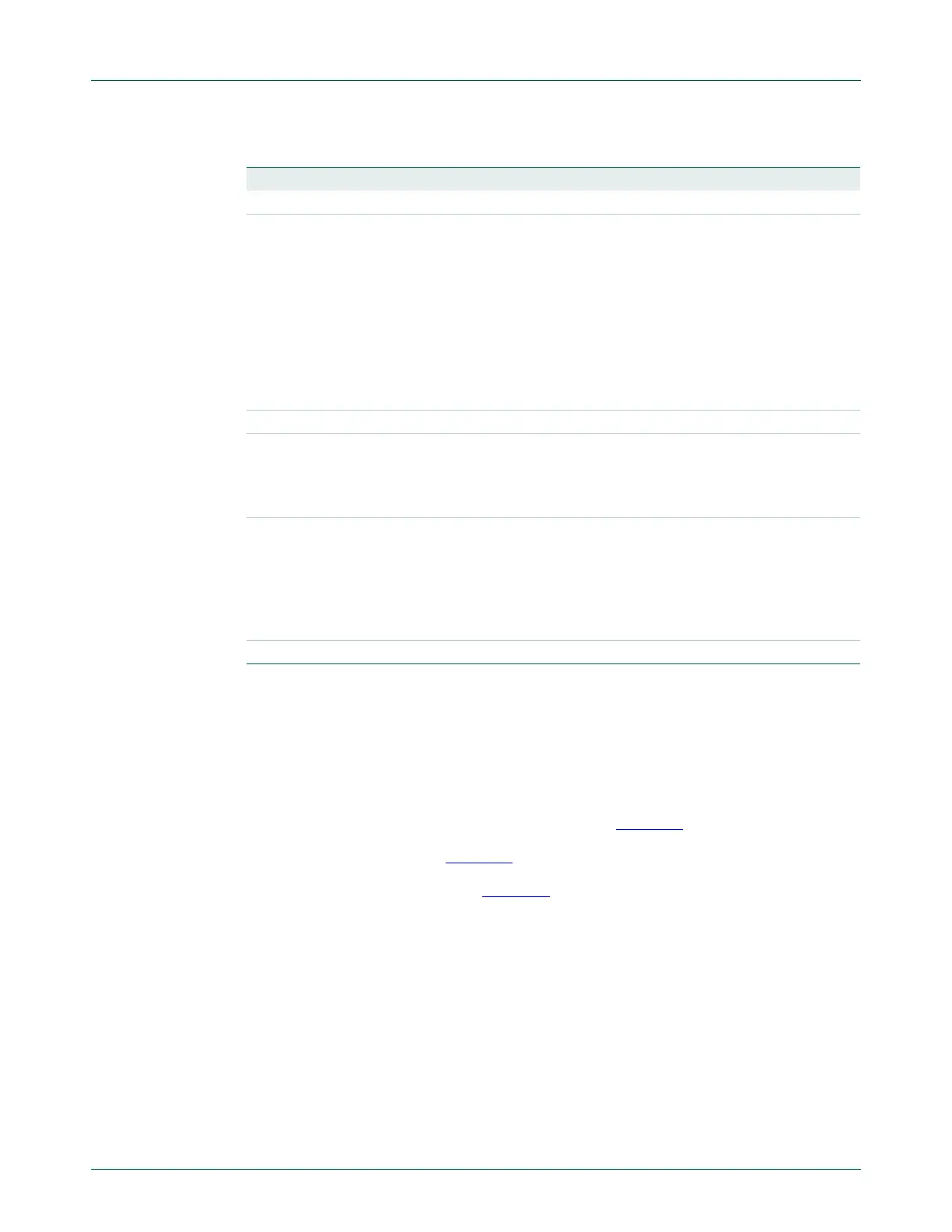

34.4.3.8 Configuration and Control Register

The CCR controls entry to Thread mode and enables:

• the handlers for NMI, hard fault and faults escalated by FAULTMASK to ignore bus

faults

• trapping of divide by zero and unaligned accesses

• access to the STIR by unprivileged software, see Table 652.

See the register summary in Table 654

for the CCR attributes.

The bit assignments are shown in Table 662

.

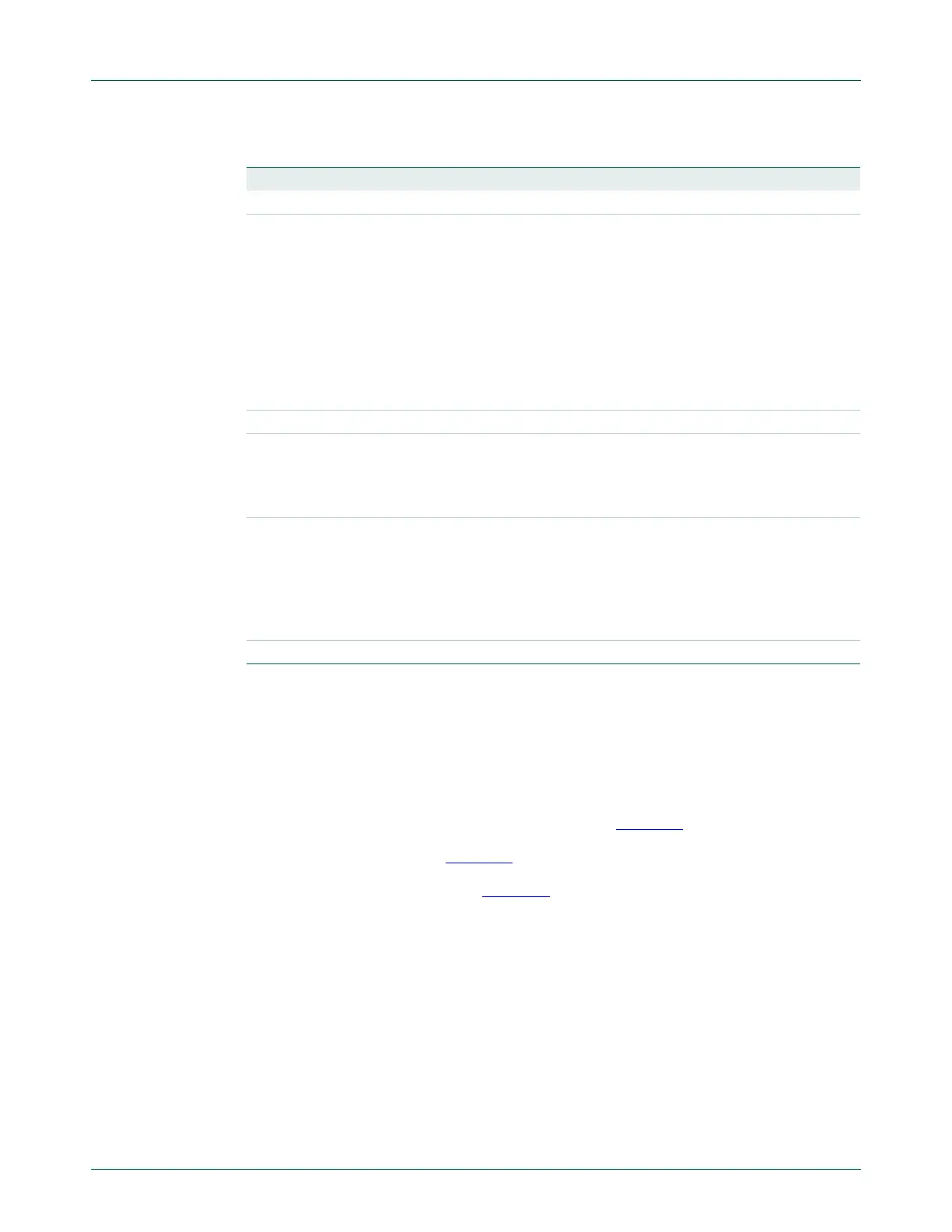

Table 661. SCR bit assignments

Bits Name Function

[31:5] - Reserved.

[4] SEVONPEND Send Event on Pending bit:

0 = only enabled interrupts or events can wakeup the processor,

disabled interrupts are excluded

1 = enabled events and all interrupts, including disabled interrupts,

can wakeup the processor.

When an event or interrupt enters pending state, the event signal

wakes up the processor from WFE. If the processor is not waiting

for an event, the event is registered and affects the next WFE.

The processor also wakes up on execution of an

SEV

instruction or

an external event.

[3] - Reserved.

[2] SLEEPDEEP Controls whether the processor uses sleep or deep sleep as its low

power mode:

0 = sleep

1 = deep sleep.

[1] SLEEPONEXIT Indicates sleep-on-exit when returning from Handler mode to

Thread mode:

0 = do not sleep when returning to Thread mode.

1 = enter sleep, or deep sleep, on return from an ISR.

Setting this bit to 1 enables an interrupt driven application to avoid

returning to an empty main application.

[0] - Reserved.

Loading...

Loading...