UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 237 of 841

NXP Semiconductors

UM10360

Chapter 11: LPC176x/5x USB device controller

flag for the DMA engine to start the data transfer if the DMA is enabled for the

corresponding endpoint in the USBEpDMASt register. The DMA cannot be enabled for

control endpoints (EP0 and EP1). USBDMARSt is a read-only register.

[1] DMA can not be enabled for this endpoint and the corresponding bit in the USBDMARSt must be 0.

11.10.7.2 USB DMA Request Clear register (USBDMARClr - 0x5000 C254)

Writing one to a bit in this register will clear the corresponding bit in the USBDMARSt

register. Writing zero has no effect.

This register is intended for initialization prior to enabling the DMA for an endpoint. When

the DMA is enabled for an endpoint, hardware clears the corresponding bit in

USBDMARSt on completion of a packet transfer. Therefore, software should not clear the

bit using this register while the endpoint is enabled for DMA operation.

USBDMARClr is a write-only register.

The USBDMARClr bit allocation is identical to the USBDMARSt register (Table 222

).

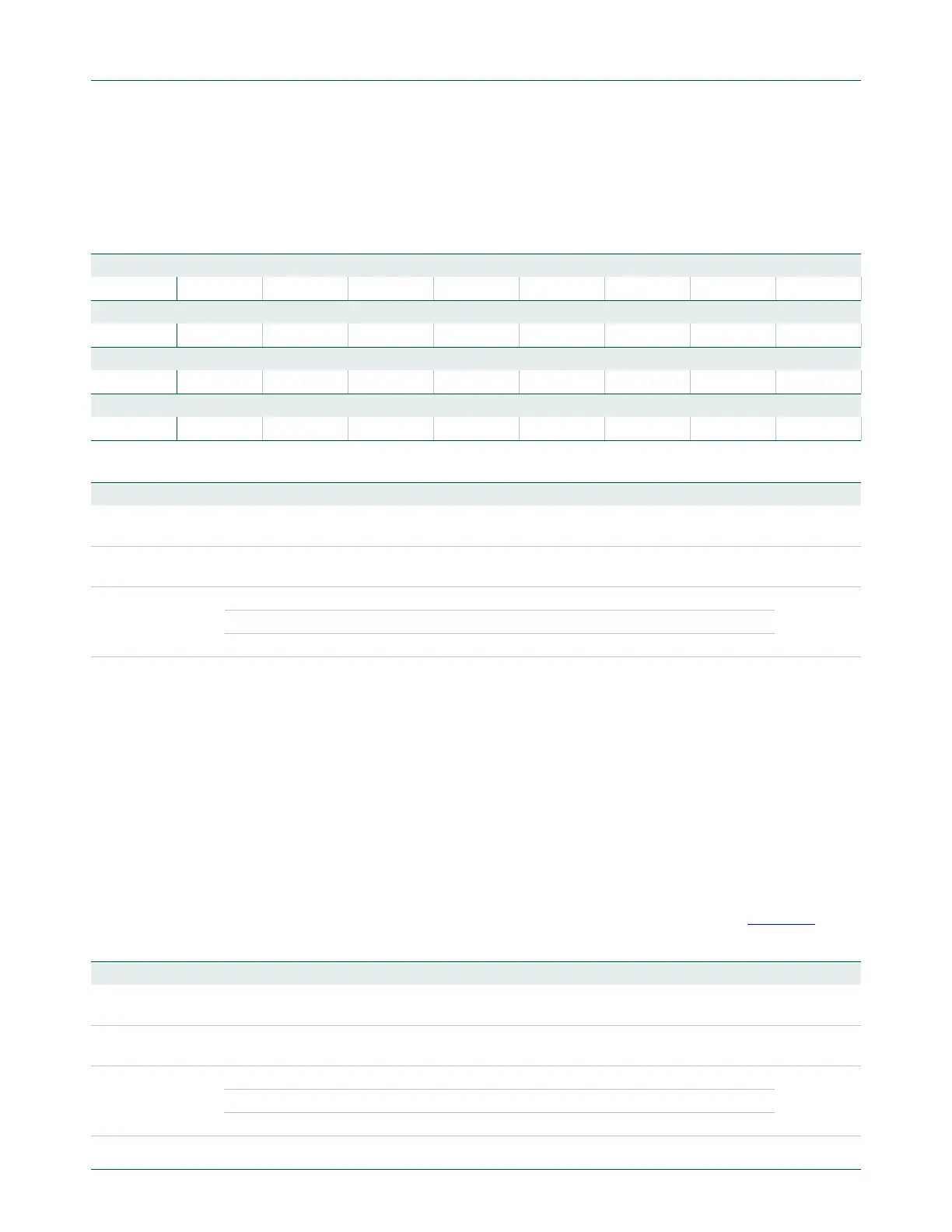

Table 222. USB DMA Request Status register (USBDMARSt - address 0x5000 C250) bit allocation

Reset value: 0x0000 0000

Bit 31 30 29 28 27 26 25 24

Symbol

EP31 EP30 EP29 EP28 EP27 EP26 EP25 EP24

Bit 23 22 21 20 19 18 17 16

Symbol

EP23 EP22 EP21 EP20 EP19 EP18 EP17 EP16

Bit 15 14 13 12 11 10 9 8

Symbol

EP15 EP14 EP13 EP12 EP11 EP10 EP9 EP8

Bit 7 6 5 4 3 2 1 0

Symbol

EP7 EP6 EP5 EP4 EP3 EP2 EP1 EP0

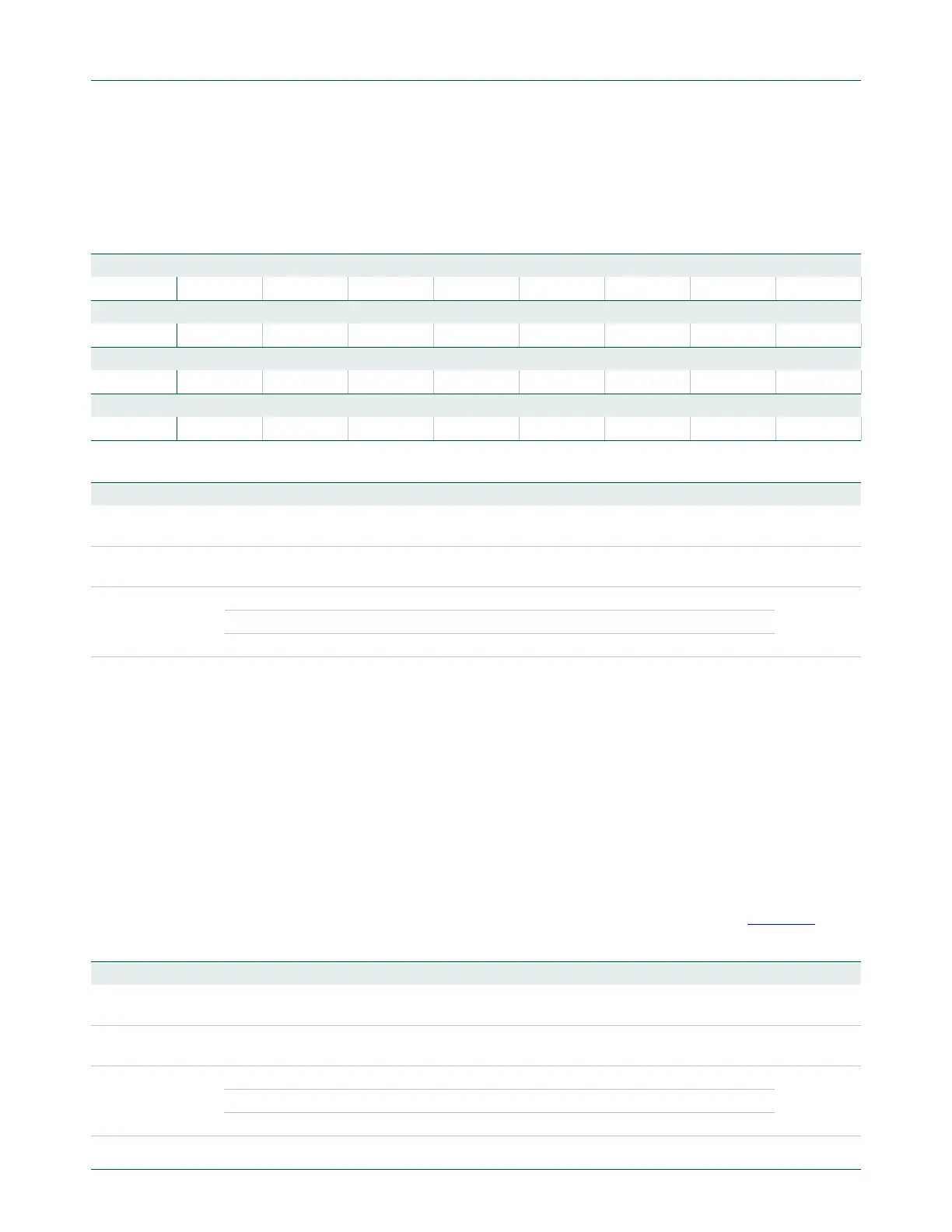

Table 223. USB DMA Request Status register (USBDMARSt - address 0x5000 C250) bit description

Bit Symbol Value Description Reset value

0 EP0 0 Control endpoint OUT (DMA cannot be enabled for this endpoint and EP0 bit

must be 0).

0

1 EP1 0 Control endpoint IN (DMA cannot be enabled for this endpoint and EP1 bit

must be 0).

0

31:2 EPxx Endpoint xx (2

xx 31) DMA request. 0

0 DMA not requested by endpoint xx.

1 DMA requested by endpoint xx.

Table 224. USB DMA Request Clear register (USBDMARClr - address 0x5000 C254) bit description

Bit Symbol Value Description Reset value

0 EP0 0 Control endpoint OUT (DMA cannot be enabled for this endpoint and the EP0

bit must be 0).

0

1 EP1 0 Control endpoint IN (DMA cannot be enabled for this endpoint and the EP1 bit

must be 0).

0

31:2 EPxx Clear the endpoint xx (2

xx 31) DMA request. 0

0 No effect.

1 Clear the corresponding bit in USBDMARSt.

Loading...

Loading...