UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 480 of 841

NXP Semiconductors

UM10360

Chapter 20: LPC176x/5x I2S

20.5.7 DMA Configuration Register 2 (I2SDMA2 - 0x400A 8018)

The I2SDMA2 register controls the operation of DMA request 2. The function of bits in

I2SDMA2 are shown in Table 405

.

20.5.8 Interrupt Request Control register (I2SIRQ - 0x400A 801C)

The I2SIRQ register controls the operation of the I

2

S interrupt request. The function of bits

in I2SIRQ are shown in Table 405

.

20.5.9 Transmit Clock Rate register (I2STXRATE - 0x400A 8020)

The MCLK rate for the I

2

S transmitter is determined by the values in the I2STXRATE

register. The required I2STXRATE setting depends on the desired audio sample rate

desired, the format (stereo/mono) used, and the data size.

The transmitter MCLK rate is generated using a fractional rate generator, dividing down

the frequency of PCLK_I2S. Values of the numerator (X) and the denominator (Y) must be

chosen to produce a frequency twice that desired for the transmitter MCLK, which must be

an integer multiple of the transmitter bit clock rate. Fractional rate generators have some

aspects that the user should be aware of when choosing settings. These are discussed in

Section 20.5.9.1

. The equation for the fractional rate generator is:

I2STXMCLK = PCLK_I2S * (X/Y) /2

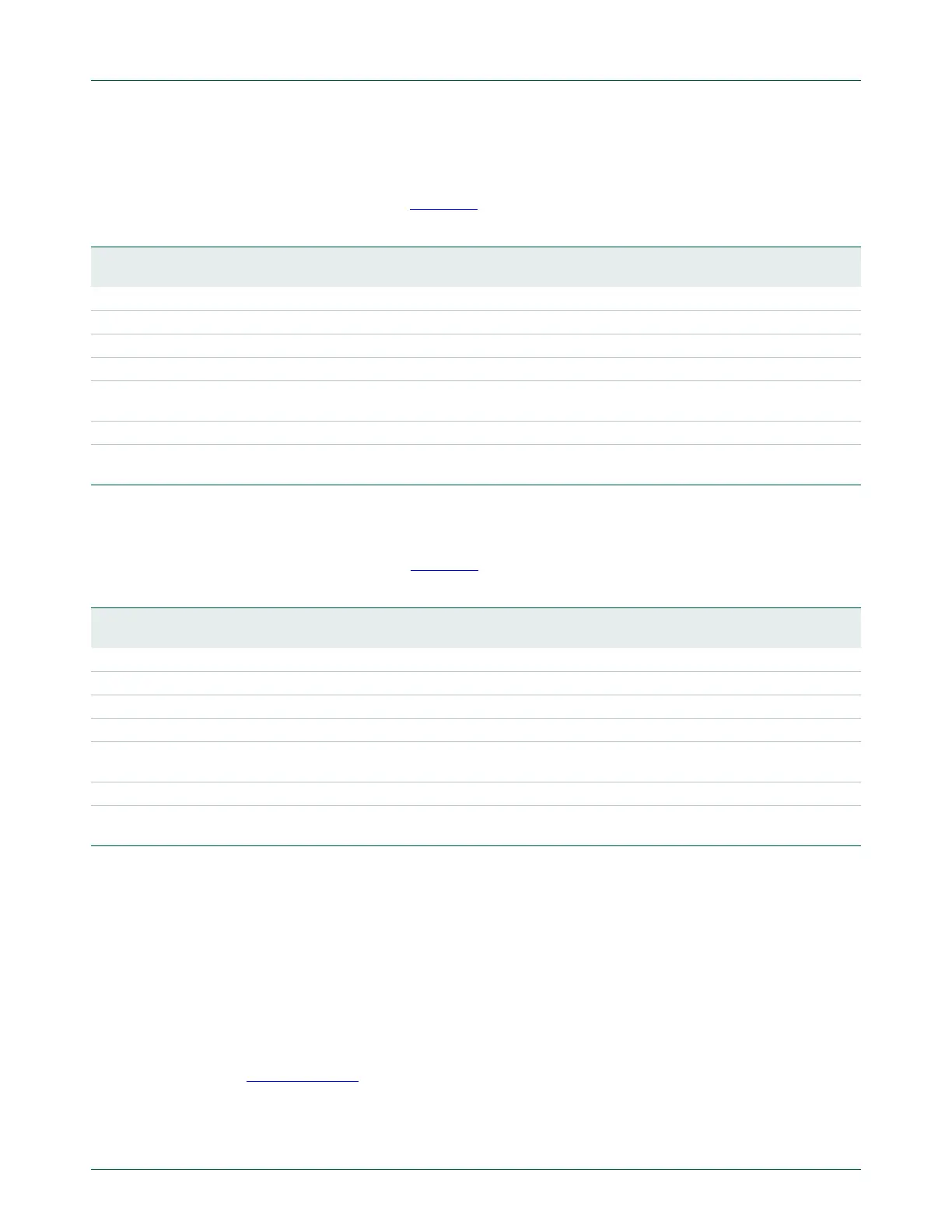

Table 411: DMA Configuration register 2 (I2SDMA2 - address 0x400A 8018) bit description

Bit Symbol Description Reset

Value

0 rx_dma2_enable When 1, enables DMA1 for I

2

S receive. 0

1 tx_dma2_enable When 1, enables DMA1 for I

2

S transmit. 0

7:2 Unused Unused. 0

11:8 rx_depth_dma2 Set the FIFO level that triggers a receive DMA request on DMA2. 0

15:12 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

19:16 tx_depth_dma2 Set the FIFO level that triggers a transmit DMA request on DMA2. 0

31:20 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

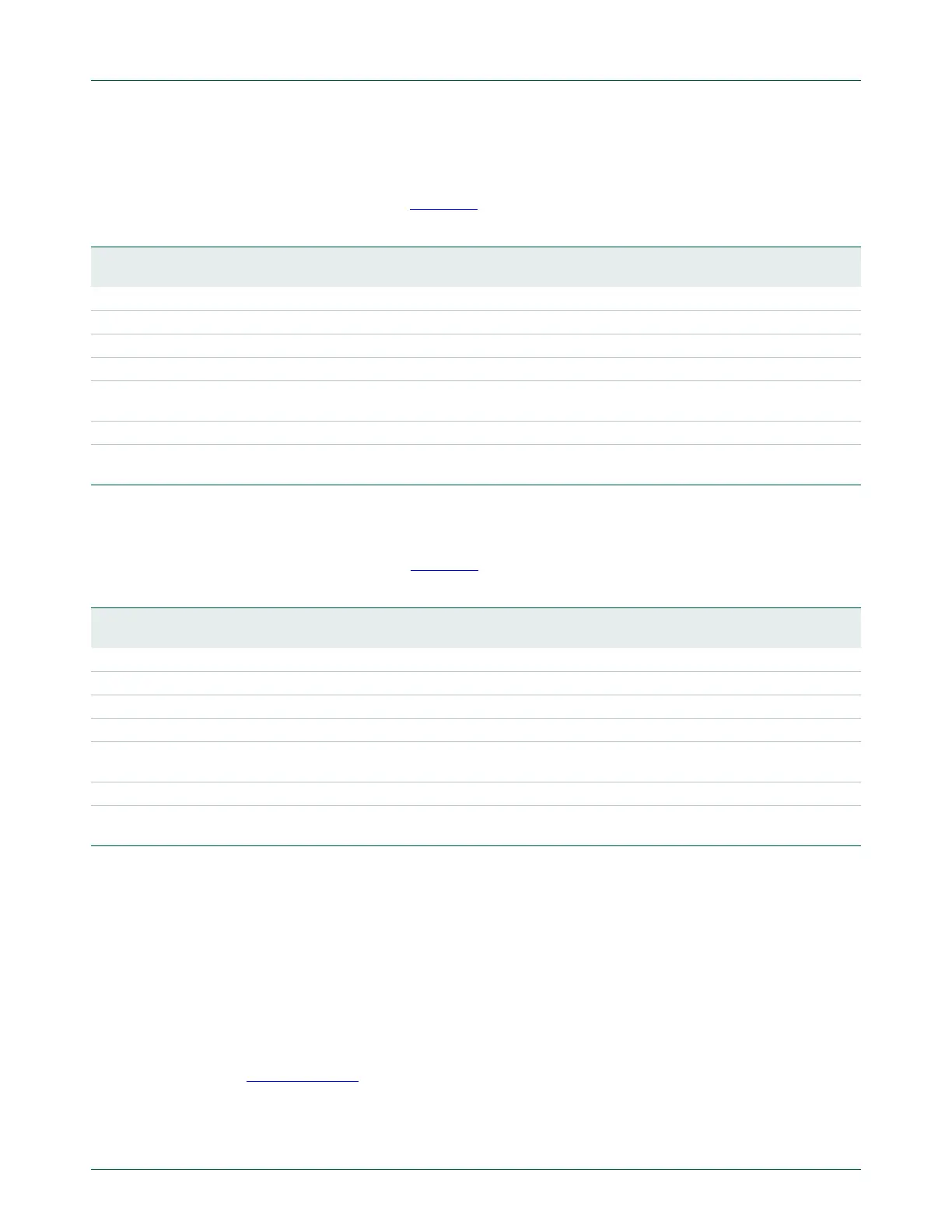

Table 412: Interrupt Request Control register (I2SIRQ - address 0x400A 801C) bit description

Bit Symbol Description Reset

Value

0 rx_Irq_enable When 1, enables I

2

S receive interrupt. 0

1 tx_Irq_enable When 1, enables

I

2

S transmit interrupt. 0

7:2 Unused Unused. 0

11:8 rx_depth_irq Set the FIFO level on which to create an irq request. 0

15:12 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

19:16 tx_depth_irq Set the FIFO level on which to create an irq request. 0

31:20 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...