UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 71 of 841

NXP Semiconductors

UM10360

Chapter 5: LPC176x/5x Flash accelerator

5.4 Flash Accelerator Configuration register (FLASHCFG - 0x400F C000)

Configuration bits select the flash access time, as shown in Table 49. The lower bits of

FLASHCFG control internal flash accelerator functions and should not be altered.

Following reset, flash accelerator functions are enabled and flash access timing is set to a

default value of 4 clocks.

Changing the FLASHCFG register value causes the flash accelerator to invalidate all of

the holding latches, resulting in new reads of flash information as required. This

guarantees synchronization of the flash accelerator to CPU operation.

5.5 Operation

Simply put, the flash accelerator attempts to have the next Cortex-M3 instruction that will

be needed in its latches in time to prevent CPU fetch stalls. The LPC176x/5x uses one

bank of flash memory. The flash accelerator includes an array of eight 128-bit buffers to

store both instructions and data in a configurable manner. Each 128-bit buffer in the array

can include four 32-bit instructions, eight 16-bit instructions or some combination of the

two. During sequential code execution, a buffer typically contains the current instruction

and the entire flash line that contains that instruction, or one flash line of data containing a

previously requested address. Buffers are marked according to how they are used (as

instruction or data buffers), and when they have been accessed. This information is used

to carry out the buffer replacement strategy.

The Cortex-M3 provides a separate bus for instruction access (I-code) and data access

(D-code) in the code memory space. These buses, plus the General Purpose DMA

Controllers’s master port, are arbitrated by the AHB multilayer matrix. Any access to the

flash memory’s address space is presented to the flash accelerator.

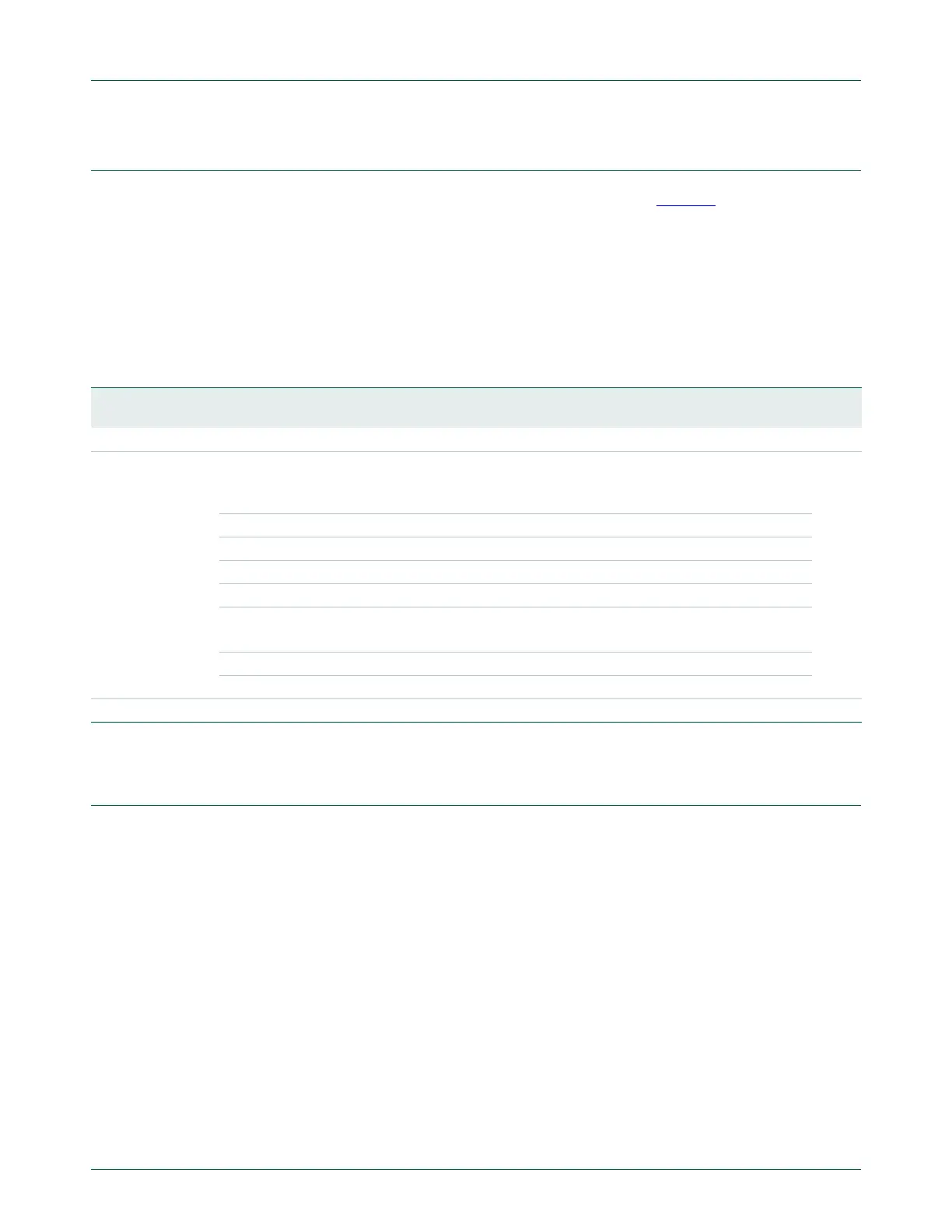

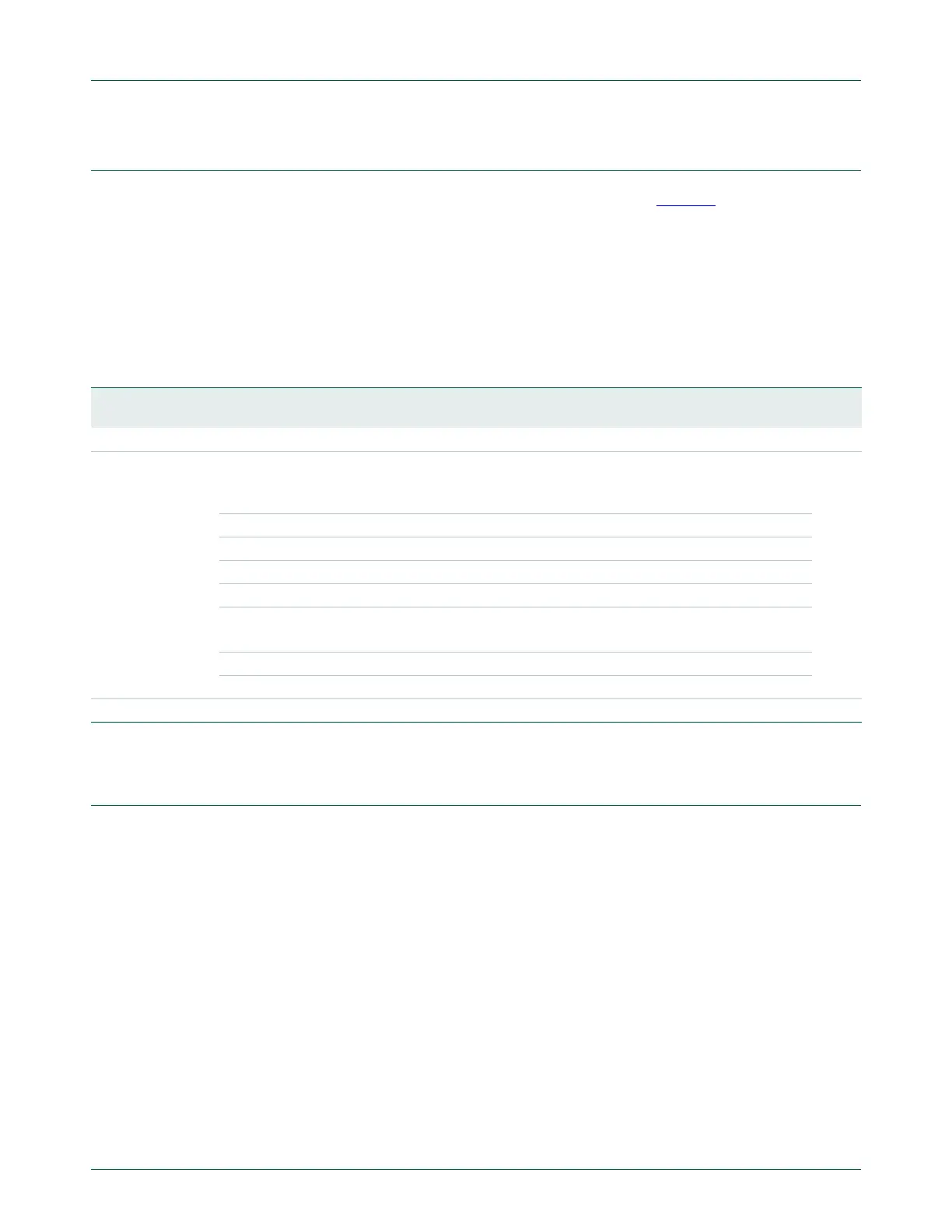

Table 49. Flash Accelerator Configuration register (FLASHCFG - address 0x400F C000) bit description

Bit Symbol Value Description Reset

value

11:0 - - Reserved, user software should not change these bits from the reset value. 0x03A

15:12 FLASHTIM Flash access time. The value of this field plus 1 gives the number of CPU clocks used

for a flash access.

Warning: improper setting of this value may result in incorrect operation of the device.

0x3

0000 Flash accesses use 1 CPU clock. Use for up to 20 MHz CPU clock.

0001 Flash accesses use 2 CPU clocks. Use for up to 40 MHz CPU clock.

0010 Flash accesses use 3 CPU clocks. Use for up to 60 MHz CPU clock.

0011 Flash accesses use 4 CPU clocks. Use for up to 80 MHz CPU clock.

0100 Flash accesses use 5 CPU clocks. Use for up to 100 MHz CPU clock.

Use for up to 120 Mhz for LPC1759 and LPC1769 only.

0101 Flash accesses use 6 CPU clocks. This “safe” setting will work under any conditions.

Other Intended for potential future higher speed devices.

31:16 - Reserved. The value read from a reserved bit is not defined. NA

Loading...

Loading...