UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 170 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

The interrupt status register is read-only. Setting can be done via the IntSet register. Reset

can be accomplished via the IntClear register.

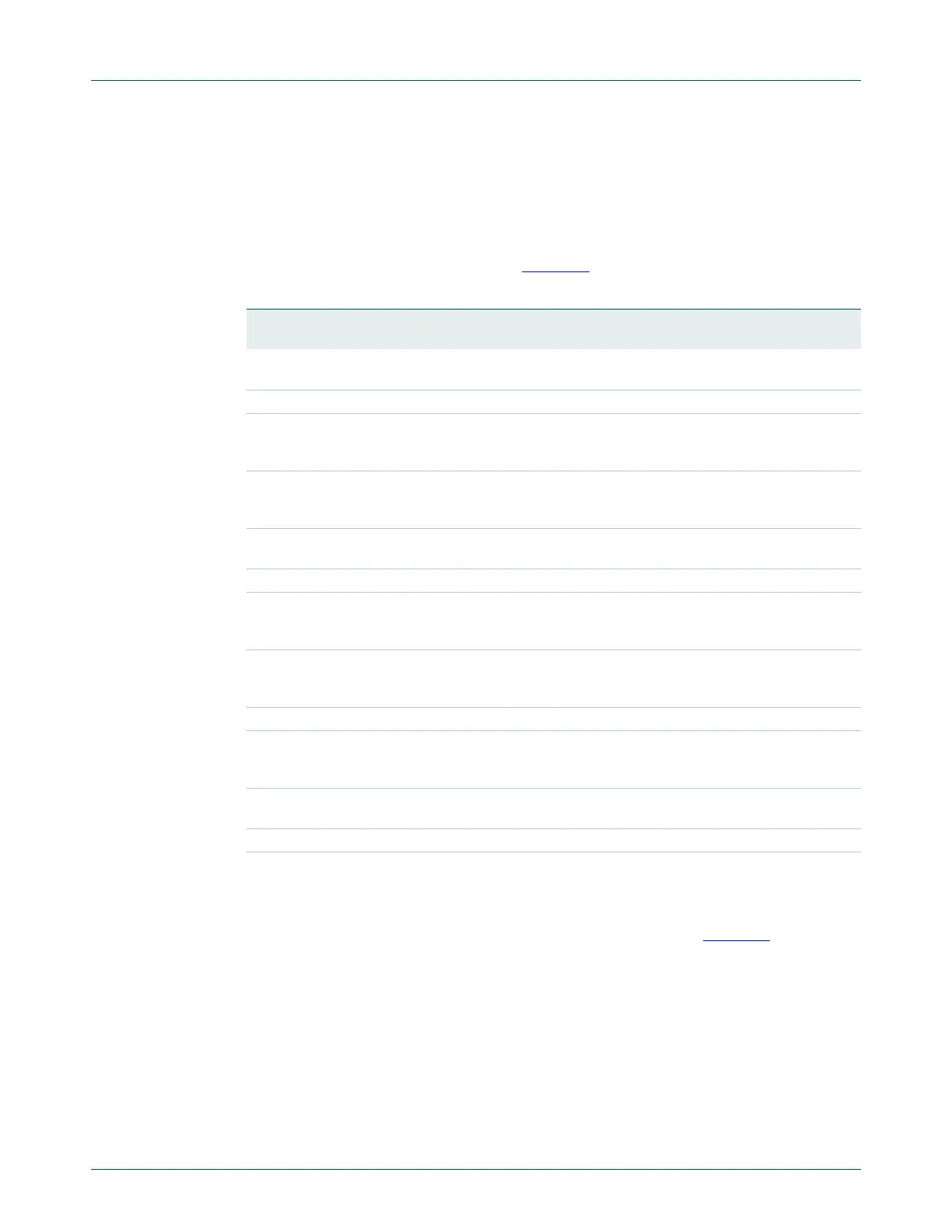

10.14.2 Interrupt Enable Register (IntEnable - 0x5000 0FE4)

The Interrupt Enable register (IntEnable) has an address of 0x5000 0FE4. The interrupt

enable register bit definition is shown in Table 171

.

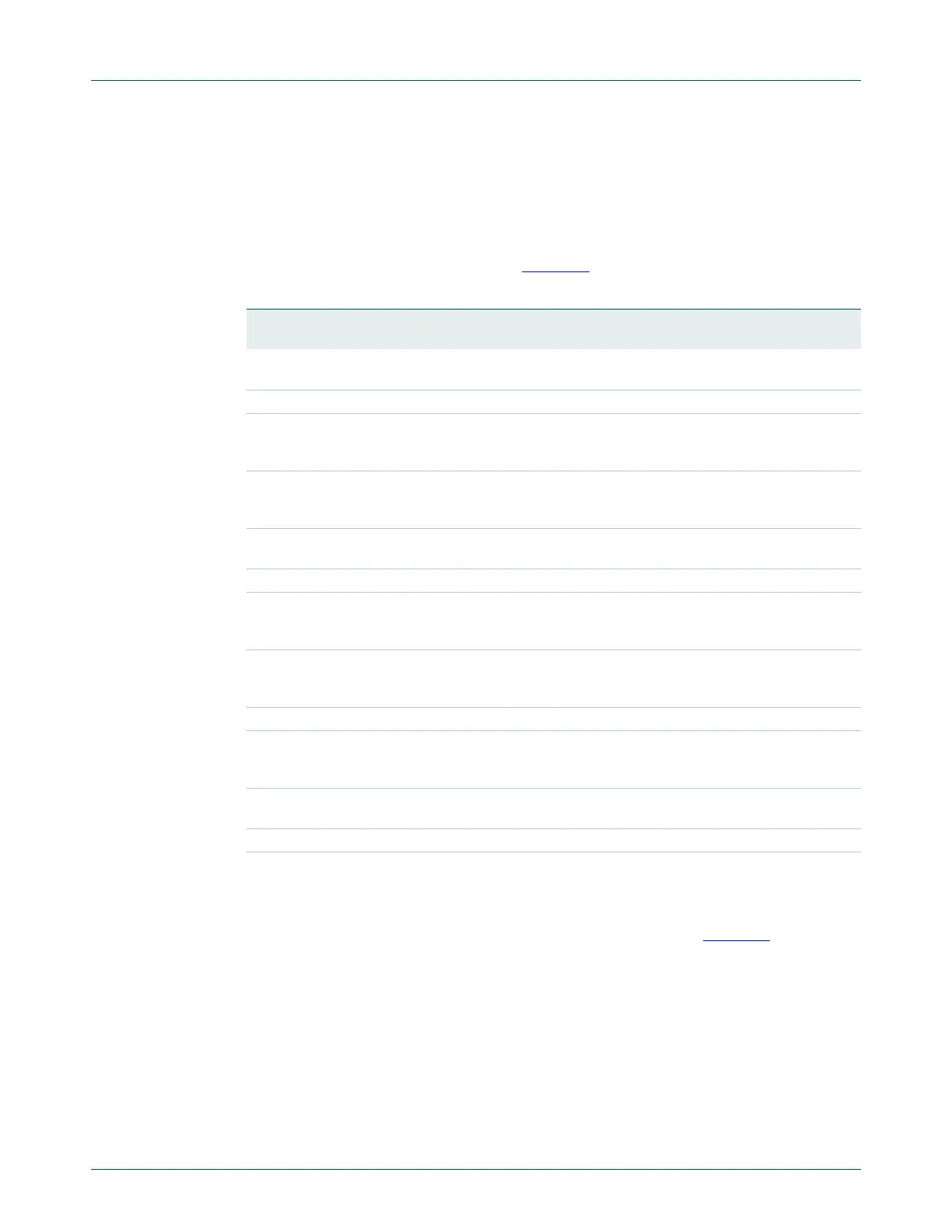

10.14.3 Interrupt Clear Register (IntClear - 0x5000 0FE8)

The Interrupt Clear register (IntClear) is a write-only register with an address of

0x5000 0FE8. The interrupt clear register bit definition is shown in Table 172

.

Table 171. Interrupt Enable register (intEnable - address 0x5000 0FE4) bit description

Bit Symbol Function Reset

value

0 RxOverrunIntEn Enable for interrupt trigger on receive buffer overrun or

descriptor underrun situations.

0

1 RxErrorIntEn Enable for interrupt trigger on receive errors. 0

2 RxFinishedIntEn Enable for interrupt triggered when all receive descriptors have

been processed i.e. on the transition to the situation where

ProduceIndex == ConsumeIndex.

0

3 RxDoneIntEn Enable for interrupt triggered when a receive descriptor has

been processed while the Interrupt bit in the Control field of the

descriptor was set.

0

4 TxUnderrunIntEn Enable for interrupt trigger on transmit buffer or descriptor

underrun situations.

0

5 TxErrorIntEn Enable for interrupt trigger on transmit errors. 0

6 TxFinishedIntEn Enable for interrupt triggered when all transmit descriptors

have been processed i.e. on the transition to the situation

where ProduceIndex == ConsumeIndex.

0

7 TxDoneIntEn Enable for interrupt triggered when a descriptor has been

transmitted while the Interrupt bit in the Control field of the

descriptor was set.

0

11:8 - Unused 0x0

12 SoftIntEn Enable for interrupt triggered by the SoftInt bit in the IntStatus

register, caused by software writing a 1 to the SoftIntSet bit in

the IntSet register.

0

13 WakeupIntEn Enable for interrupt triggered by a Wake-up event detected by

the receive filter.

0

31:14 - Unused 0x0

Loading...

Loading...