UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 124 of 841

NXP Semiconductors

UM10360

Chapter 9: LPC176x/5x General Purpose Input/Output (GPIO)

[1] Reset value reflects the data stored in used bits only. It does not include reserved bits content.

9.5.1 GPIO port Direction register FIOxDIR (FIO0DIR to FIO4DIR- 0x2009

C000 to 0x2009 C080)

This word accessible register is used to control the direction of the pins when they are

configured as GPIO port pins. Direction bit for any pin must be set according to the pin

functionality.

Note that GPIO pins P0.29 and P0.30 are shared with the USB_D+ and USB_D- pins and

must have the same direction. If either FIO0DIR bit 29 or 30 are configured as zero, both

P0.29 and P0.30 will be inputs. If both FIO0DIR bits 29 and 30 are ones, both P0.29 and

P0.30 will be outputs.

Aside from the 32-bit long and word only accessible FIODIR register, every fast GPIO port

can also be controlled via several byte and half-word accessible registers listed in

Table 104

, too. Next to providing the same functions as the FIODIR register, these

additional registers allow easier and faster access to the physical port pins.

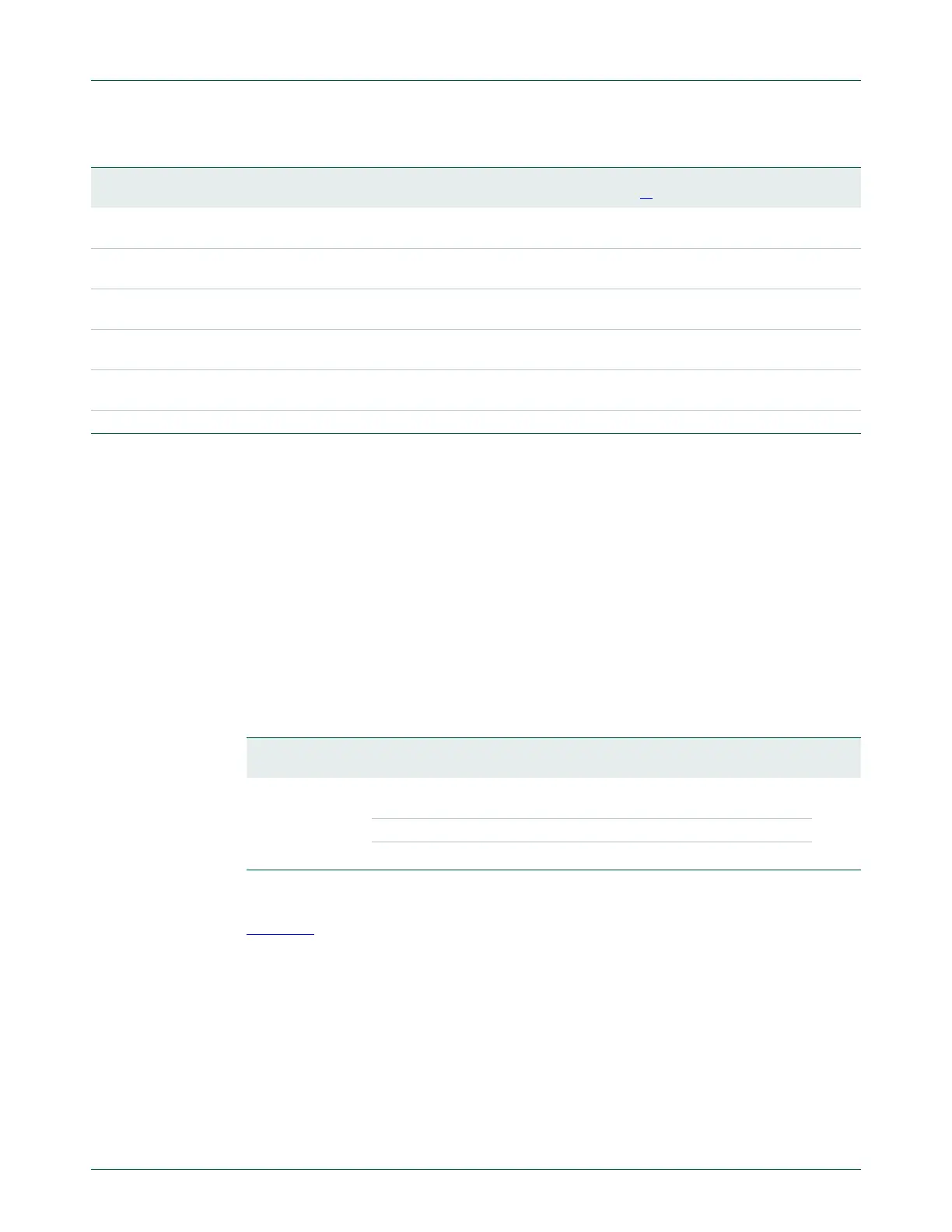

Table 102. GPIO interrupt register map

Generic

Name

Description Access Reset

value

[1]

PORTn Register

Name & Address

IntEnR GPIO Interrupt Enable for Rising edge. R/W 0 IO0IntEnR - 0x4002 8090

IO2IntEnR - 0x4002 80B0

IntEnF GPIO Interrupt Enable for Falling edge. R/W 0 IO0IntEnR - 0x4002 8094

IO2IntEnR - 0x4002 80B4

IntStatR GPIO Interrupt Status for Rising edge. RO 0 IO0IntStatR - 0x4002 8084

IO2IntStatR - 0x4002 80A4

IntStatF GPIO Interrupt Status for Falling edge. RO 0 IO0IntStatF - 0x4002 8088

IO2IntStatF - 0x4002 80A8

IntClr GPIO Interrupt Clear. WO 0 IO0IntClr - 0x4002 808C

IO2IntClr - 0x4002 80AC

IntStatus GPIO overall Interrupt Status. RO 0 IOIntStatus - 0x4002 8080

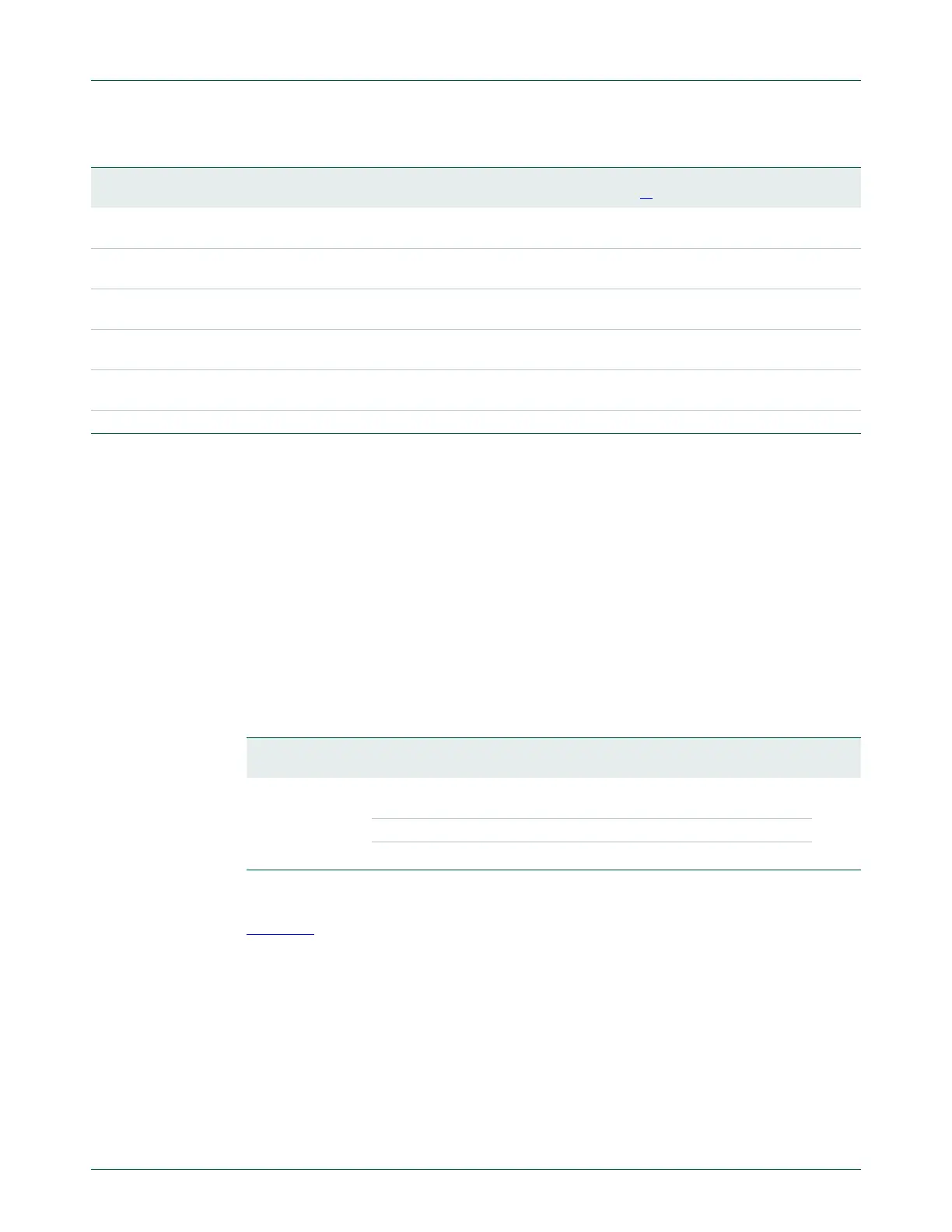

Table 103. Fast GPIO port Direction register FIO0DIR to FIO4DIR - addresses 0x2009 C000 to

0x2009 C080) bit description

Bit Symbol Value Description Reset

value

31:0 FIO0DIR

FIO1DIR

FIO2DIR

FIO3DIR

FIO4DIR

Fast GPIO Direction PORTx control bits. Bit 0 in FIOxDIR

controls pin Px.0, bit 31 in FIOxDIR controls pin Px.31.

0x0

0 Controlled pin is input.

1 Controlled pin is output.

Loading...

Loading...