UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 20 December 2013 773 of 841

NXP Semiconductors

UM10360

Chapter 34: Appendix: Cortex-M3 user guide

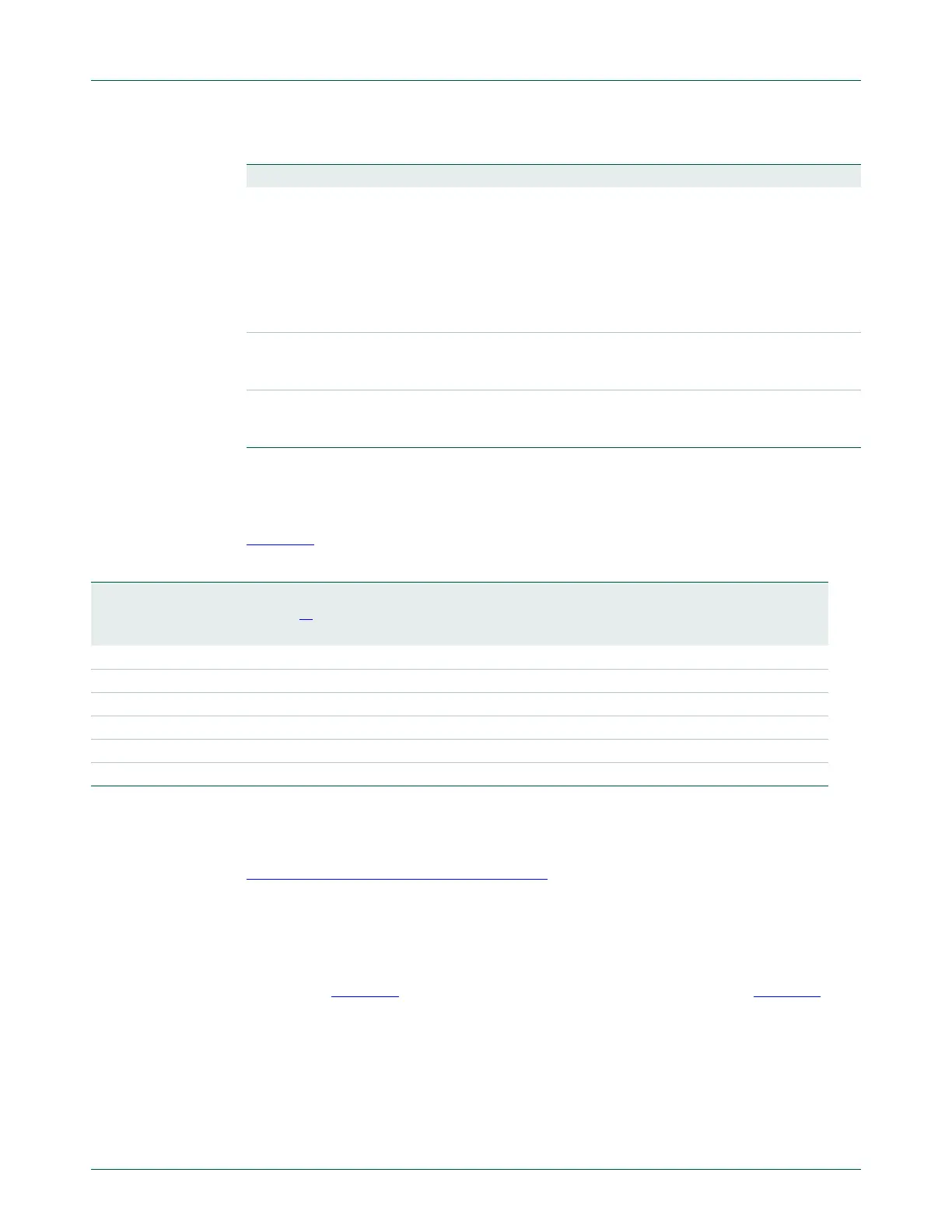

34.4.3.6.1 Binary point

The PRIGROUP field indicates the position of the binary point that splits the PRI_n fields

in the Interrupt Priority Registers into separate group priority and subpriority fields.

Table 660

shows how the PRIGROUP value controls this split.

[1] PRI_n[7:0] field showing the binary point. x denotes a group priority field bit, and y denotes a subpriority field bit. Bits [2:0] are not used

in LPC176x/5x devices.

Remark: Determining preemption of an exception uses only the group priority field, see

Section 34.3.3.6 “

Interrupt priority grouping”.

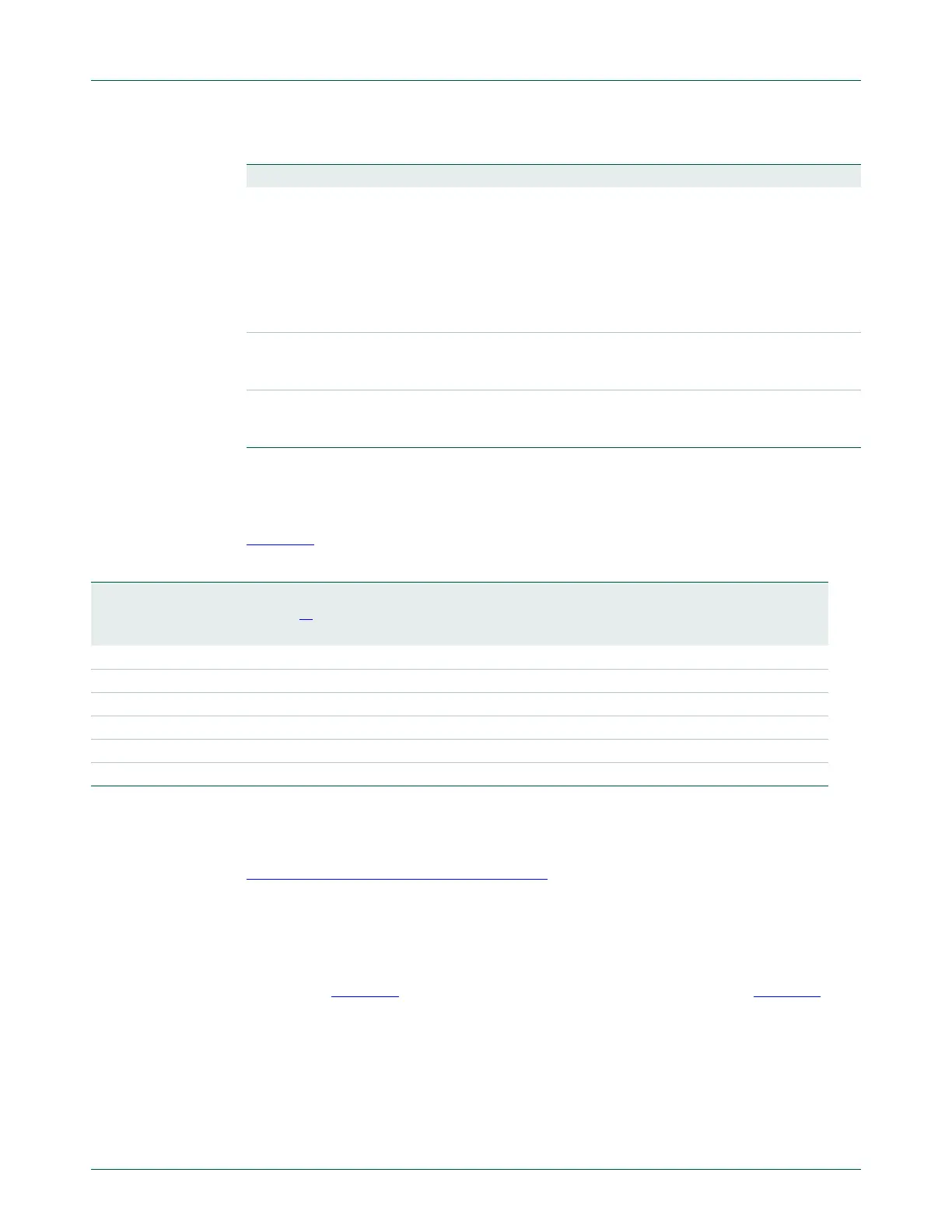

34.4.3.7 System Control Register

The SCR controls features of entry to and exit from low power state. See the register

summary in Table 654

for its attributes. The bit assignments are shown in Table 661.

[2] SYSRESETREQ WO System reset request:

0 = no system reset request

1 = asserts a signal to the outer system that requests a

reset.

This is intended to force a large system reset of all major

components except for debug.

This bit reads as 0.

[1] VECTCLRACTIVE WO Reserved for Debug use. This bit reads as 0. When writing

to the register you must write 0 to this bit, otherwise

behavior is Unpredictable.

[0] VECTRESET WO Reserved for Debug use. This bit reads as 0. When writing

to the register you must write 0 to this bit, otherwise

behavior is Unpredictable.

Table 659. AIRCR bit assignments …continued

Bits Name Type Function

Table 660. Priority grouping

Interrupt priority level value, PRI_N[7:0] Number of

PRIGROUP Binary point

[1]

Group priority

bits

Subpriority bits Group priorities Subpriorities

b010 bxxxxx.000 [7:3] none 32 1

b011 bxxxx.y000 [7:4] [3] 16 2

b100 bxxx.yy000 [7:5] [4:3] 8 4

b101 bxx.yyy000 [7:6] [5:3] 4 8

b110 bx.yyyy000 [7] [6:3] 2 16

b111 b.yyyyy000 None [7:3] 1 32

Loading...

Loading...