UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 380 of 841

NXP Semiconductors

UM10360

Chapter 16: LPC176x/5x CAN1/2

[1] Write access to the look-up table section configuration registers are possible only during the Acceptance filter bypass mode or the

Acceptance filter off mode.

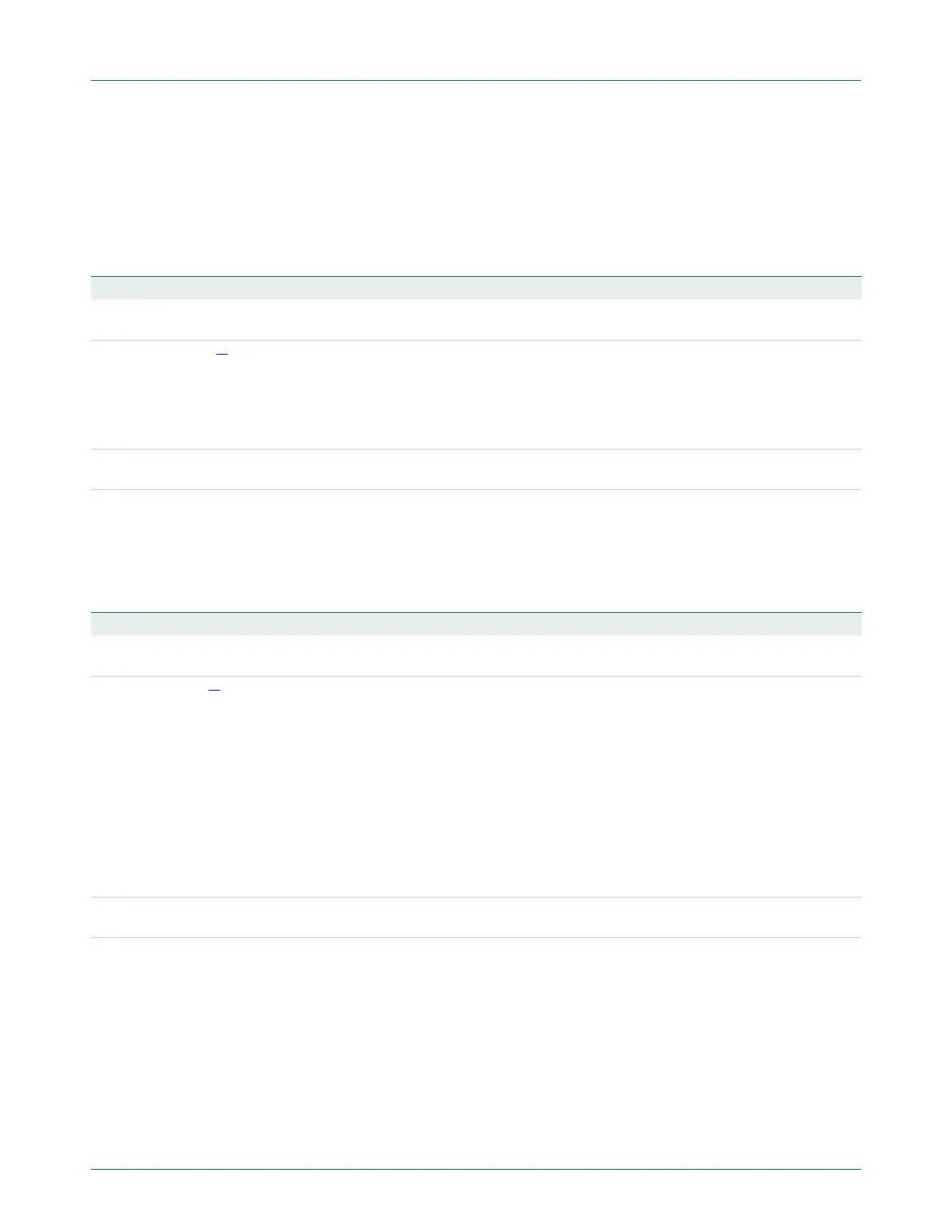

16.14.6 Extended Frame Group Start Address register (EFF_GRP_sa -

0x4003 C010)

[1] Write access to the look-up table section configuration registers are possible only during the Acceptance filter bypass mode or the

Acceptance filter off mode.

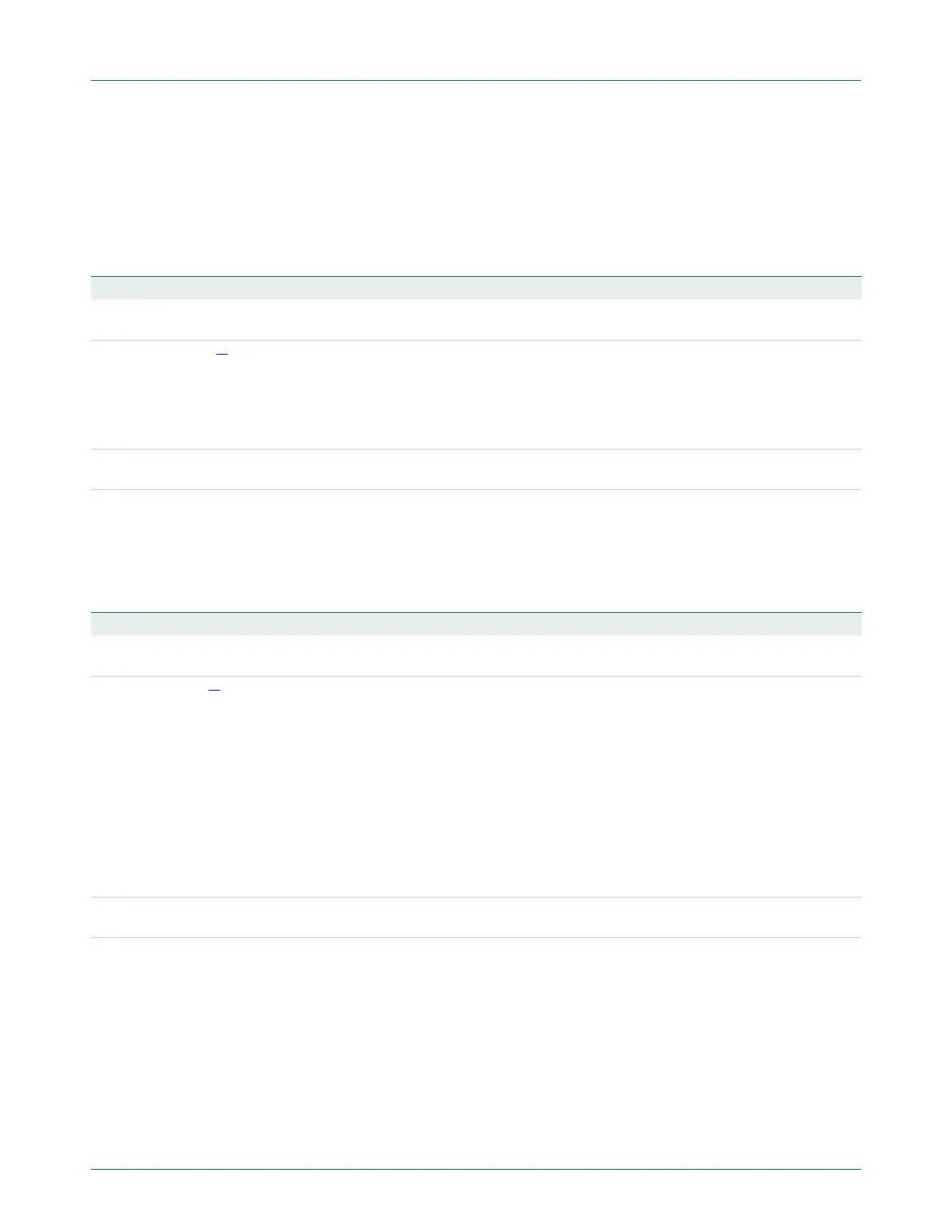

16.14.7 End of AF Tables register (ENDofTable - 0x4003 C014)

[1] Write access to the look-up table section configuration registers are possible only during the Acceptance filter bypass mode or the

Acceptance filter off mode.

16.14.8 Status registers

The look-up table error status registers, the error addresses, and the flag register provide

information if a programming error in the look-up table RAM during the ID screening was

encountered. The look-up table error address and flag register have only read access. If

an error is detected, the LUTerror flag is set, and the LUTerrorAddr register provides the

Table 346. Extended Frame Group Start Address register (EFF_GRP_sa - address 0x4003 C010) bit description

Bit Symbol Description Reset Value

1:0 - Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

11:2 Eff_GRP_sa

[1]

The start address of the table of grouped Extended Identifiers in AF Lookup RAM. If

the table is empty, write the same value in this register and the ENDofTable register

described below. The largest value that should be written to this register is 0x800,

when this table is empty and the last word (address 0x7FC) in AF Lookup Table RAM

is used. For compatibility with possible future devices, please write zeroes in bits

31:12 and 1:0 of this register.

0

31:12 - Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

Table 347. End of AF Tables register (ENDofTable - address 0x4003 C014) bit description

Bit Symbol Description Reset Value

1:0 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

11:2 EndofTable

[1]

The address above the last active address in the last active AF table. For compatibility

with possible future devices, please write zeroes in bits 31:12 and 1:0 of this register.

If the eFCAN bit in the AFMR is 0, the largest value that should be written to this

register is 0x800, which allows the last word (address 0x7FC) in AF Lookup Table RAM

to be used.

If the eFCAN bit in the AFMR is 1, this value marks the start of the area of Acceptance

Filter RAM, into which the Acceptance Filter will automatically receive messages for

selected IDs on selected CAN buses. In this case, the maximum value that should be

written to this register is 0x800 minus 6 times the value in SFF_sa. This allows 12 bytes

of message storage between this address and the end of Acceptance Filter RAM, for

each Standard ID that is specified between the start of Acceptance Filter RAM, and the

next active AF table.

0

31:12 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Loading...

Loading...