UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 427 of 841

NXP Semiconductors

UM10360

Chapter 18: LPC176x/5x SSP0/1

18.6.9 SSPn Interrupt Clear Register (SSP0ICR - 0x4008 8020, SSP1ICR -

0x4003 0020)

Software can write one or more one(s) to this write-only register, to clear the

corresponding interrupt condition(s) in the SSP controller. Note that the other two interrupt

conditions can be cleared by writing or reading the appropriate FIFO, or disabled by

clearing the corresponding bit in SSPnIMSC.

18.6.10 SSPn DMA Control Register (SSP0DMACR - 0x4008 8024,

SSP1DMACR - 0x4003 0024)

The SSPnDMACR register is the DMA control register. It is a read/write register.

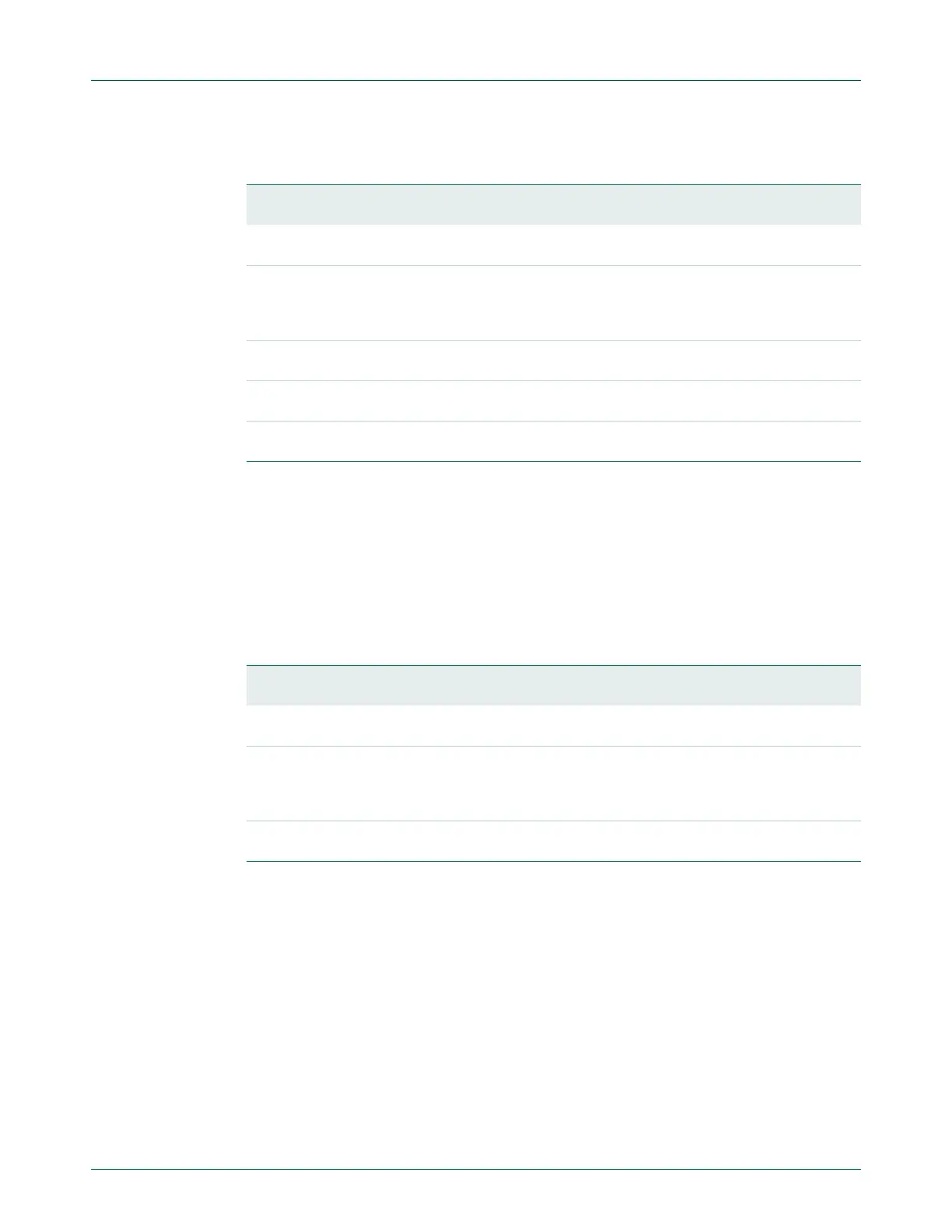

Table 377: SSPn Masked Interrupt Status register (SSPnMIS -address 0x4008 801C, SSP1MIS

- 0x4003 001C) bit description

Bit Symbol Description Reset

Value

0 RORMIS This bit is 1 if another frame was completely received while the RxFIFO

was full, and this interrupt is enabled.

0

1 RTMIS This bit is 1 if the Rx FIFO is not empty, has not been read for a

"time-out period", and this interrupt is enabled. The time-out period is

the same for master and slave modes and is determined by the SSP bit

rate: 32 bits at PCLK / (CPSDVSR

[SCR+1]).

0

2 RXMIS This bit is 1 if the Rx FIFO is at least half full, and this interrupt is

enabled.

0

3 TXMIS This bit is 1 if the Tx FIFO is at least half empty, and this interrupt is

enabled.

0

31:4 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

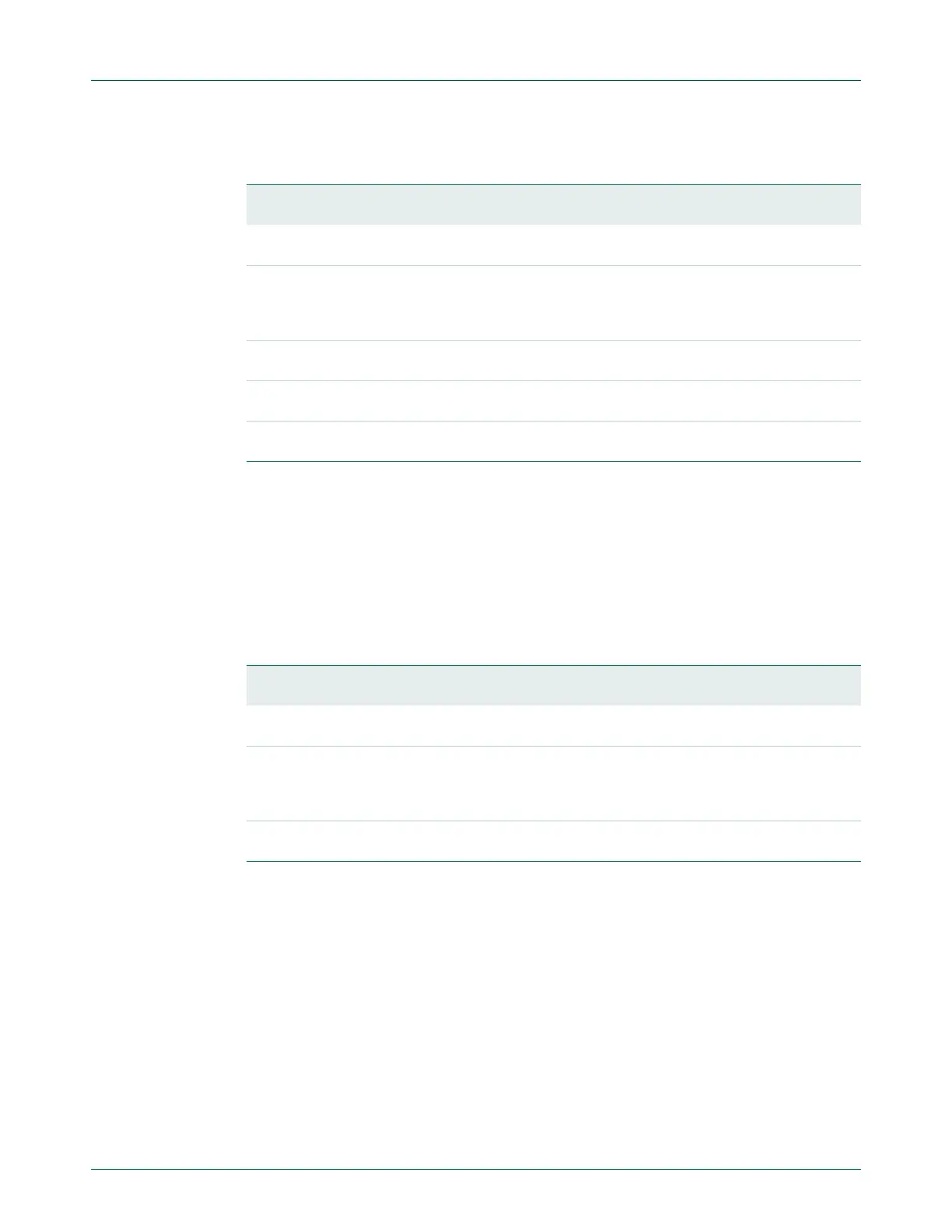

Table 378: SSPn interrupt Clear Register (SSP0ICR - address 0x4008 8020, SSP1ICR -

0x4003 0020) bit description

Bit Symbol Description Reset

Value

0 RORIC Writing a 1 to this bit clears the “frame was received when RxFIFO was

full” interrupt.

NA

1 RTIC Writing a 1 to this bit clears the "Rx FIFO was not empty and has not

been read for a time-out period" interrupt. The time-out period is the

same for master and slave modes and is determined by the SSP bit rate:

32 bits at PCLK / (CPSDVSR

[SCR+1]).

NA

31:2 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Loading...

Loading...