UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 499 of 841

NXP Semiconductors

UM10360

Chapter 21: LPC176x/5x Timer 0/1/2/3

Match events for Match 0 and Match 1 in each timer can cause a DMA request, see

Section 21.6.12

.

21.6.12 DMA operation

DMA requests are generated by a match of the Timer Counter (TC) register value to either

Match Register 0 (MR0) or Match Register 1 (MR1). This is not connected to the operation

of the Match outputs controlled by the EMR register. Each match sets a DMA request flag,

which is connected to the DMA controller. In order to have an effect, the GPDMA must be

configured and the relevant timer DMA request selected as a DMA source via the

DMAREQSEL register, see Section 31.5.15

.

When a timer is initially set up to generate a DMA request, the request may already be

asserted before a match condition occurs. An initial DMA request may be avoided by

having software write a one to the interrupt flag location, as if clearing a timer interrupt.

See Section 21.6.1

. A DMA request will be cleared automatically when it is acted upon by

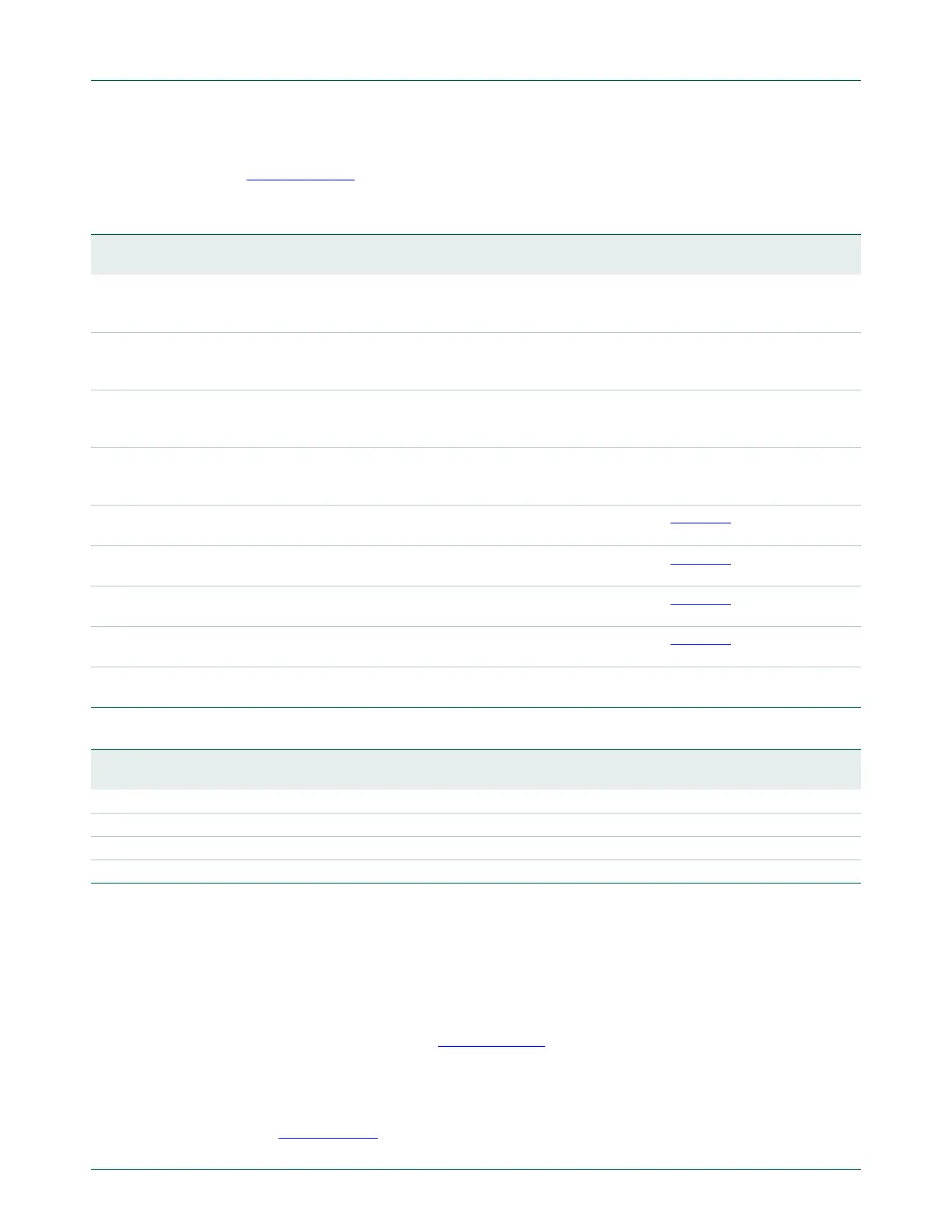

Table 431. External Match Register (T[0/1/2/3]EMR - addresses 0x4000 403C, 0x4000 803C, 0x4009 003C,

0x4009 403C) bit description

Bit Symbol Description Reset

Value

0 EM0 External Match 0. When a match occurs between the TC and MR0, this bit can either toggle, go

low, go high, or do nothing, depending on bits 5:4 of this register. This bit can be driven onto a

MATn.0 pin, in a positive-logic manner (0 = low, 1 = high).

0

1 EM1 External Match 1. When a match occurs between the TC and MR1, this bit can either toggle, go

low, go high, or do nothing, depending on bits 7:6 of this register. This bit can be driven onto a

MATn.1 pin, in a positive-logic manner (0 = low, 1 = high).

0

2 EM2 External Match 2. When a match occurs between the TC and MR2, this bit can either toggle, go

low, go high, or do nothing, depending on bits 9:8 of this register. This bit can be driven onto a

MATn.2 pin, in a positive-logic manner (0 = low, 1 = high).

0

3 EM3 External Match 3. When a match occurs between the TC and MR3, this bit can either toggle, go

low, go high, or do nothing, depending on bits 11:10 of this register. This bit can be driven onto a

MATn.3 pin, in a positive-logic manner (0 = low, 1 = high).

0

5:4 EMC0 External Match Control 0. Determines the functionality of External Match 0. Table 432

shows the

encoding of these bits.

00

7:6 EMC1 External Match Control 1. Determines the functionality of External Match 1. Table 432

shows the

encoding of these bits.

00

9:8 EMC2 External Match Control 2. Determines the functionality of External Match 2. Table 432

shows the

encoding of these bits.

00

11:10 EMC3 External Match Control 3. Determines the functionality of External Match 3. Table 432

shows the

encoding of these bits.

00

15:12 - Reserved, user software should not write ones to reserved bits. The value read from a reserved

bit is not defined.

NA

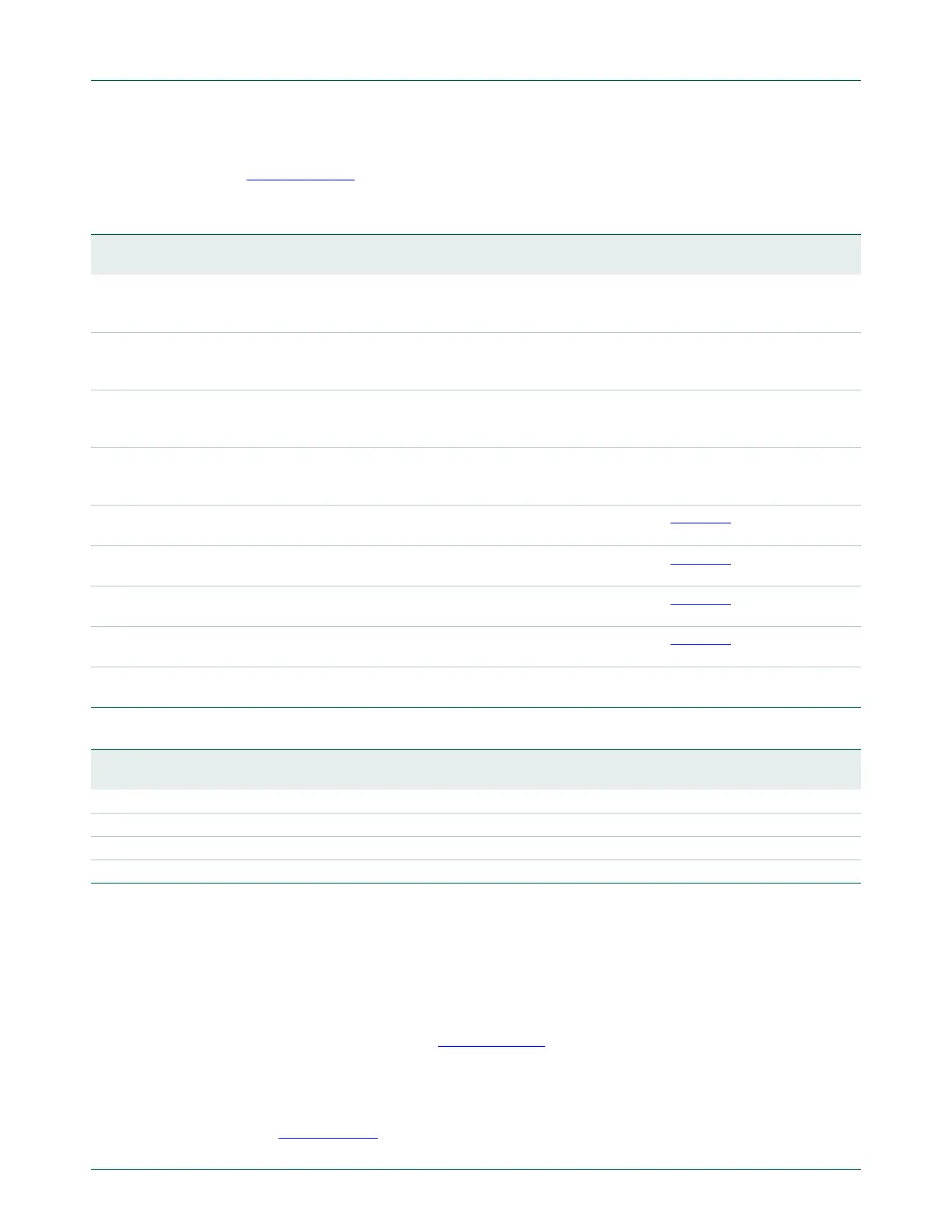

Table 432. External Match Control

EMR[11:10], EMR[9:8],

EMR[7:6], or EMR[5:4]

Function

00 Do Nothing.

01 Clear the corresponding External Match bit/output to 0 (MATn.m pin is LOW if pinned out).

10 Set the corresponding External Match bit/output to 1 (MATn.m pin is HIGH if pinned out).

11 Toggle the corresponding External Match bit/output.

Loading...

Loading...