UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 239 of 841

NXP Semiconductors

UM10360

Chapter 11: LPC176x/5x USB device controller

11.10.7.6 USB EP DMA Enable register (USBEpDMAEn - 0x5000 C288)

Writing one to a bit to this register will enable the DMA operation for the corresponding

endpoint. Writing zero has no effect.The DMA cannot be enabled for control endpoints

EP0 and EP1. USBEpDMAEn is a write-only register.

11.10.7.7 USB EP DMA Disable register (USBEpDMADis - 0x5000 C28C)

Writing a one to a bit in this register clears the corresponding bit in USBEpDMASt. Writing

zero has no effect on the corresponding bit of USBEpDMASt. Any write to this register

clears the internal DMA_PROCEED flag. Refer to Section 11.15.5.4 “

Optimizing

descriptor fetch” for more information on the DMA_PROCEED flag. If a DMA transfer is in

progress for an endpoint when its corresponding bit is cleared, the transfer is completed

before the DMA is disabled. When an error condition is detected during a DMA transfer,

the corresponding bit is cleared by hardware. USBEpDMADis is a write-only register.

11.10.7.8 USB DMA Interrupt Status register (USBDMAIntSt - 0x5000 C290)

Each bit of this register reflects whether any of the 32 bits in the corresponding interrupt

status register are set. USBDMAIntSt is a read-only register.

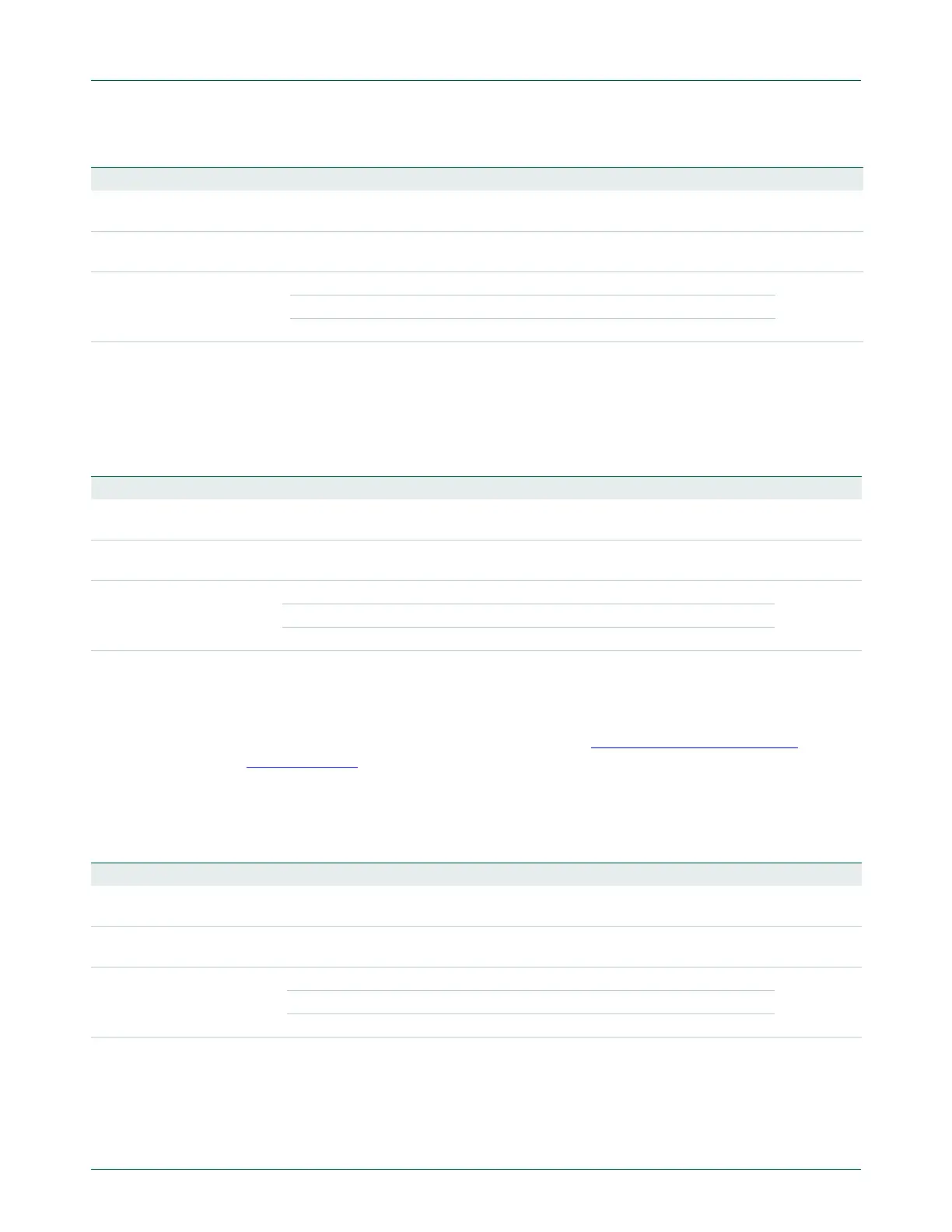

Table 227. USB EP DMA Status register (USBEpDMASt - address 0x5000 C284) bit description

Bit Symbol Value Description Reset value

0 EP0_DMA_ENABLE 0 Control endpoint OUT (DMA cannot be enabled for this endpoint and

the EP0_DMA_ENABLE bit must be 0).

0

1 EP1_DMA_ENABLE 0 Control endpoint IN (DMA cannot be enabled for this endpoint and

the EP1_DMA_ENABLE bit must be 0).

0

31:2 EPxx_DMA_ENABLE endpoint xx (2

xx 31) DMA enabled bit. 0

0 The DMA for endpoint EPxx is disabled.

1 The DMA for endpoint EPxx is enabled.

Table 228. USB EP DMA Enable register (USBEpDMAEn - address 0x5000 C288) bit description

Bit Symbol Value Description Reset value

0 EP0_DMA_ENABLE 0 Control endpoint OUT (DMA cannot be enabled for this endpoint and

the EP0_DMA_ENABLE bit value must be 0).

0

1 EP1_DMA_ENABLE 0 Control endpoint IN (DMA cannot be enabled for this endpoint and the

EP1_DMA_ENABLE bit must be 0).

0

31:2 EPxx_DMA_ENABLE Endpoint xx(2

xx 31) DMA enable control bit. 0

0No effect.

1 Enable the DMA operation for endpoint EPxx.

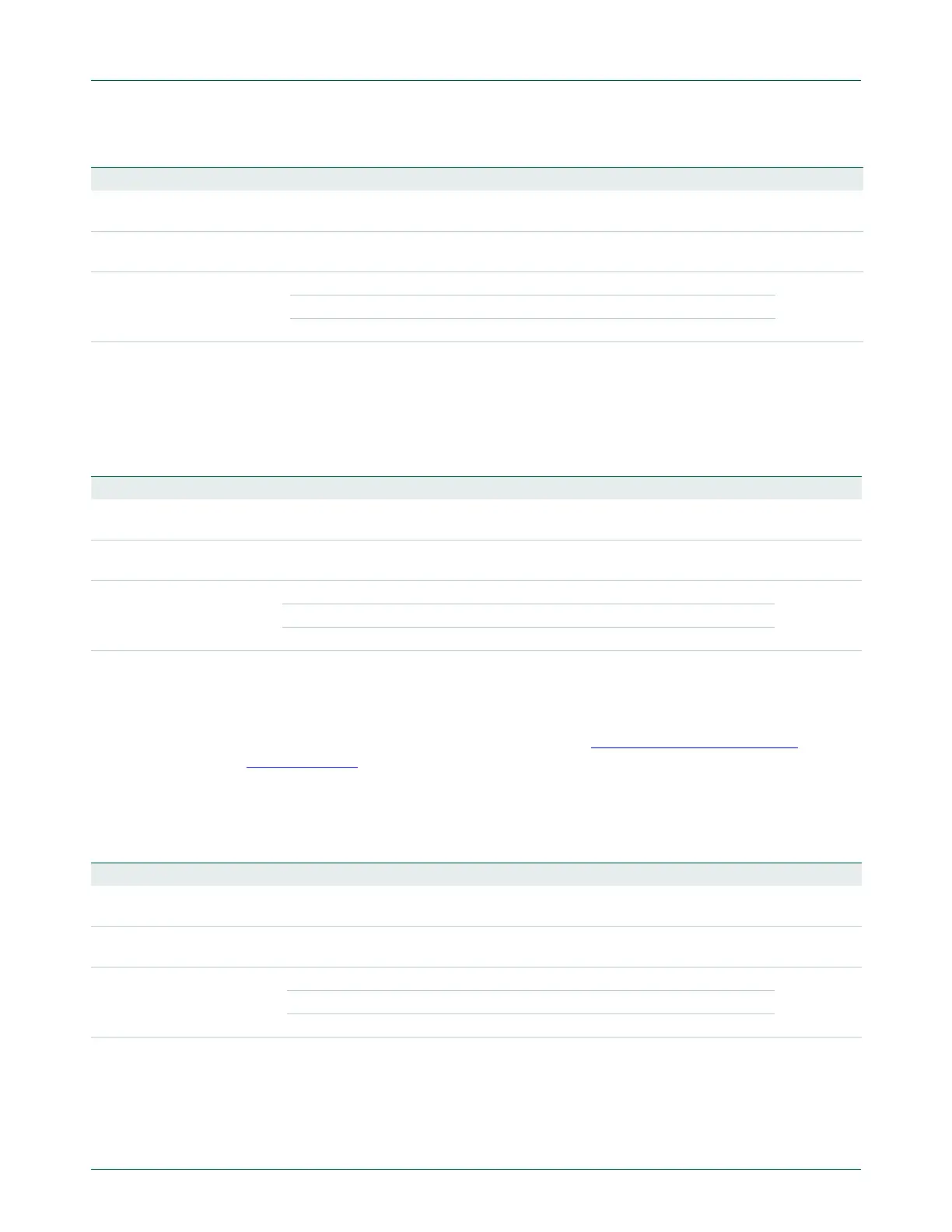

Table 229. USB EP DMA Disable register (USBEpDMADis - address 0x5000 C28C) bit description

Bit Symbol Value Description Reset value

0 EP0_DMA_DISABLE 0 Control endpoint OUT (DMA cannot be enabled for this endpoint and

the EP0_DMA_DISABLE bit value must be 0).

0

1 EP1_DMA_DISABLE 0 Control endpoint IN (DMA cannot be enabled for this endpoint and the

EP1_DMA_DISABLE bit value must be 0).

0

31:2 EPxx_DMA_DISABLE Endpoint xx (2

xx 31) DMA disable control bit. 0

0No effect.

1 Disable the DMA operation for endpoint EPxx.

Loading...

Loading...