UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 167 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

10.13 Receive filter register definitions

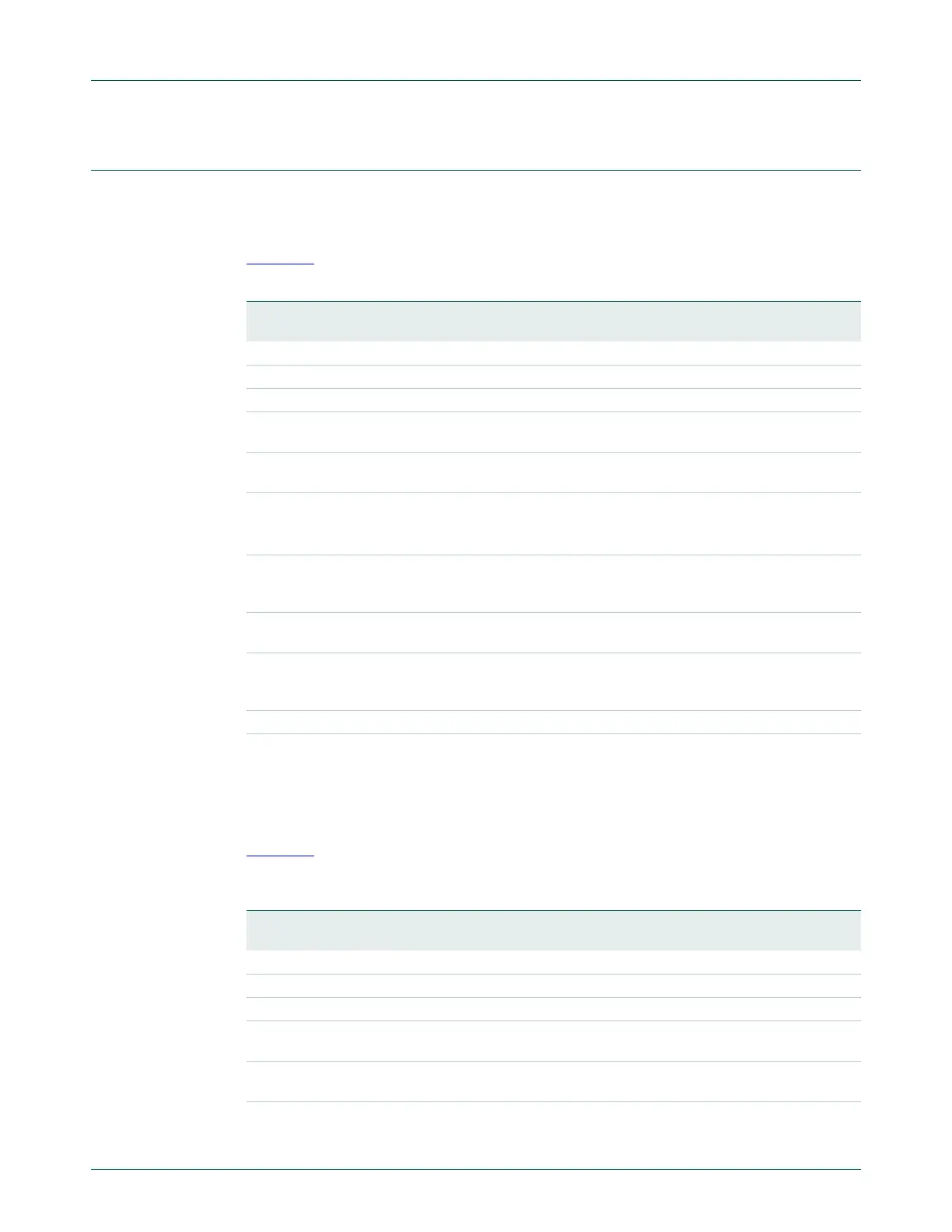

10.13.1 Receive Filter Control Register (RxFilterCtrl - 0x5000 0200)

The Receive Filter Control register (RxFilterCtrl) has an address of 0x5000 0200.

Table 165

lists the definition of the individual bits in the register.

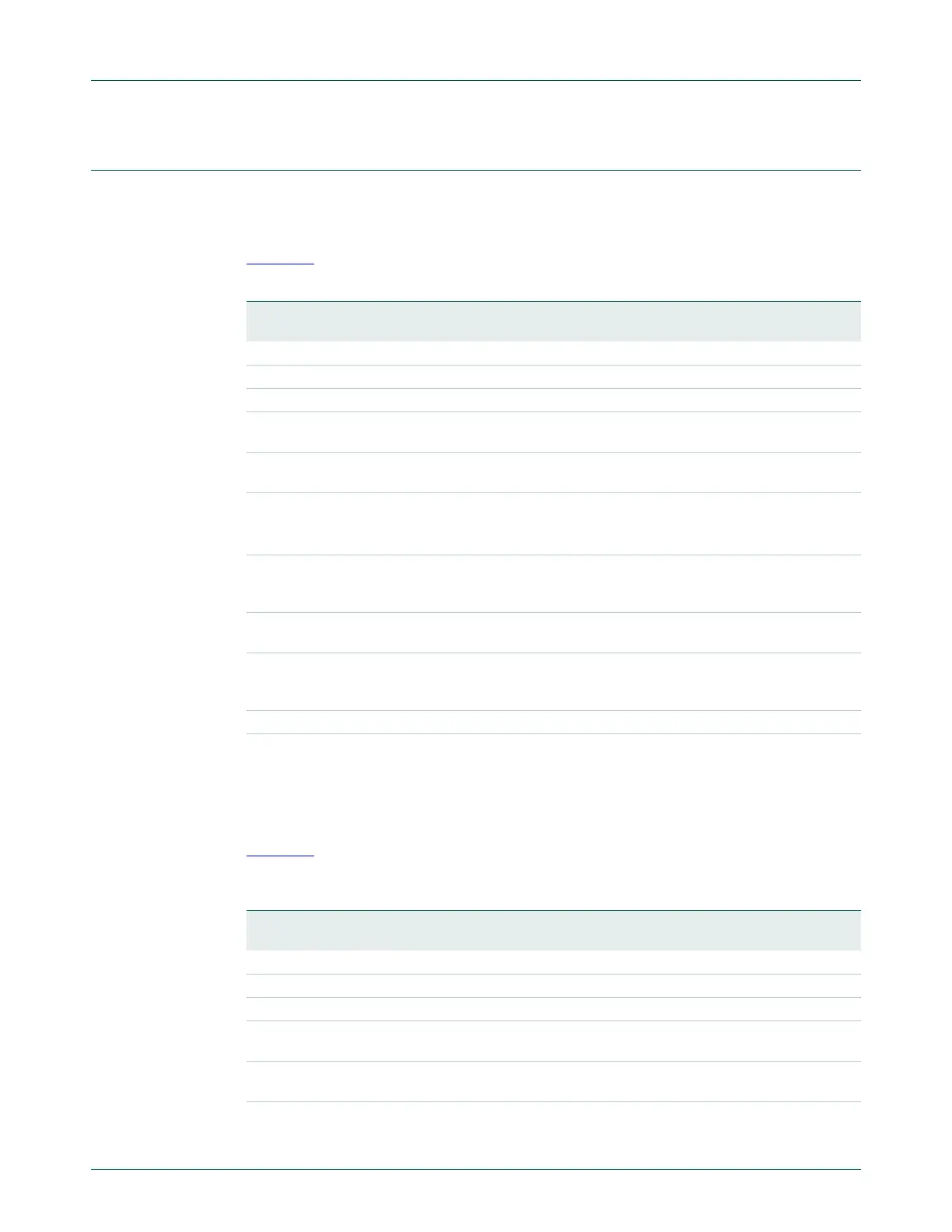

10.13.2 Receive Filter WoL Status Register (RxFilterWoLStatus - 0x5000 0204)

The Receive Filter Wake-up on LAN Status register (RxFilterWoLStatus) is a read-only

register with an address of 0x5000 0204.

Table 166

lists the definition of the individual bits in the register.

Table 165. Receive Filter Control register (RxFilterCtrl - address 0x5000 0200) bit description

Bit Symbol Function Reset

value

0 AcceptUnicastEn When set to ’1’, all unicast frames are accepted. 0

1 AcceptBroadcastEn When set to ’1’, all broadcast frames are accepted. 0

2 AcceptMulticastEn When set to ’1’, all multicast frames are accepted. 0

3 AcceptUnicastHashEn When set to ’1’, unicast frames that pass the imperfect

hash filter are accepted.

0

4 AcceptMulticastHashEn When set to ’1’, multicast frames that pass the

imperfect hash filter are accepted.

0

5 AcceptPerfectEn When set to ’1’, the frames with a destination address

identical to the

station address are accepted.

0

11:6 - Reserved, user software should not write ones to

reserved bits. The value read from a reserved bit is not

defined.

NA

12 MagicPacketEnWoL When set to ’1’, the result of the magic packet filter will

generate a WoL interrupt when there is a match.

0

13 RxFilterEnWoL When set to ’1’, the result of the perfect address

matching filter and the imperfect hash filter will

generate a WoL interrupt when there is a match.

0

31:14 - Unused 0x0

Table 166. Receive Filter WoL Status register (RxFilterWoLStatus - address 0x5000 0204) bit

description

Bit Symbol Function Reset

value

0 AcceptUnicastWoL When the value is ’1’, a unicast frames caused WoL. 0

1 AcceptBroadcastWoL When the value is ’1’, a broadcast frame caused WoL. 0

2 AcceptMulticastWoL When the value is ’1’, a multicast frame caused WoL. 0

3 AcceptUnicastHashWoL When the value is ’1’, a unicast frame that passes the

imperfect hash filter caused WoL.

0

4 AcceptMulticastHashWoL When the value is ’1’, a multicast frame that passes the

imperfect hash filter caused WoL.

0

5 AcceptPerfectWoL When the value is ’1’, the perfect address matching filter

caused WoL.

0

Loading...

Loading...