UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 154 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

10.11.5 Collision Window / Retry Register (CLRT - 0x5000 0010)

The Collision window / Retry register (CLRT) has an address of 0x5000 0010. Its bit

definition is shown in Table 134

.

10.11.6 Maximum Frame Register (MAXF - 0x5000 0014)

The Maximum Frame register (MAXF) has an address of 0x5000 0014. Its bit definition is

shown in Table 135

.

10.11.7 PHY Support Register (SUPP - 0x5000 0018)

The PHY Support register (SUPP) has an address of 0x5000 0018. The SUPP register

provides additional control over the RMII interface. The bit definition of this register is

shown in Table 136

.

Unused bits in the PHY support register should be left as zeroes.

10.11.8 Test Register (TEST - 0x5000 001C)

The Test register (TEST) has an address of 0x5000 001C. The bit definition of this register

is shown in Table 137

. These bits are used for testing purposes only.

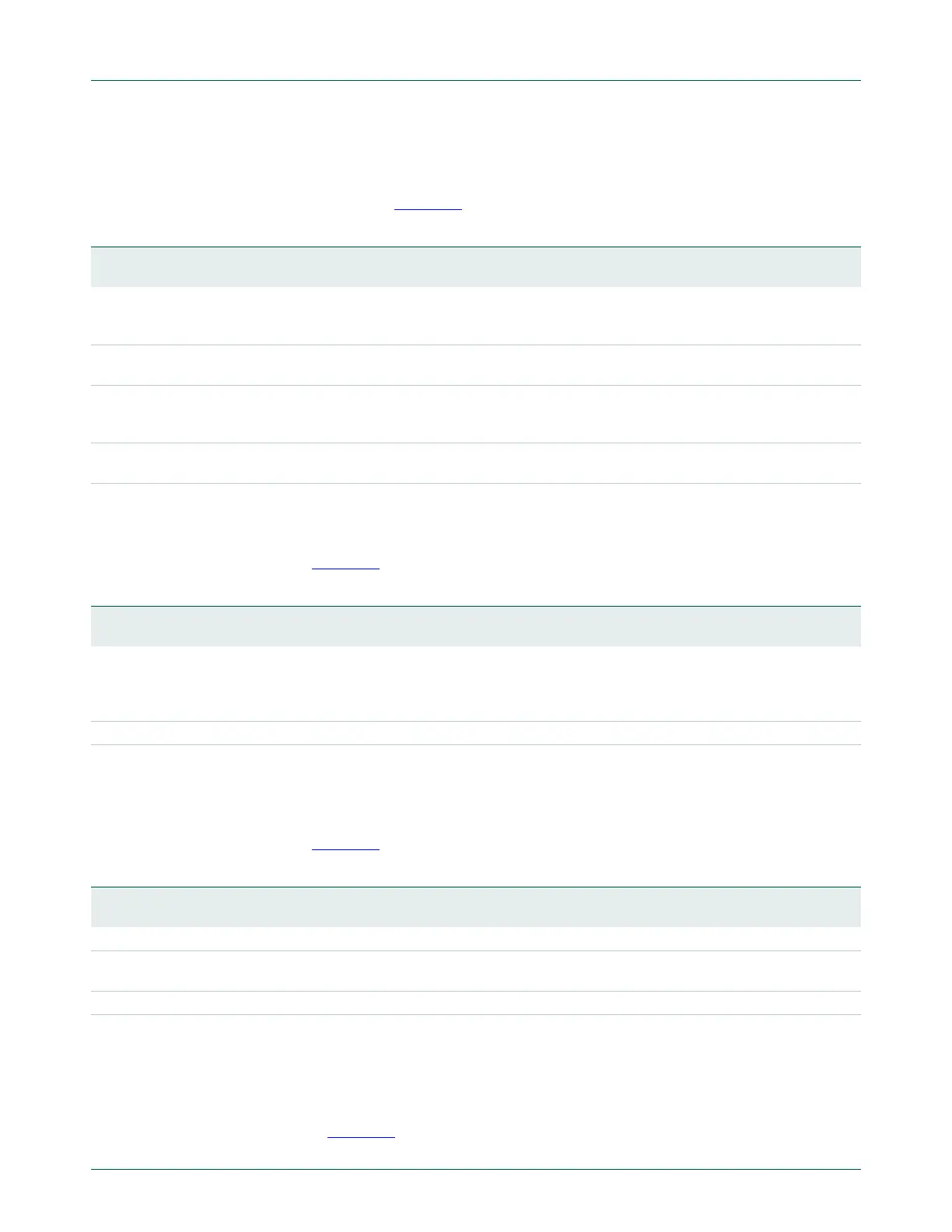

Table 134. Collision Window / Retry register (CLRT - address 0x5000 0010) bit description

Bit Symbol Function Reset

value

3:0 RETRANSMISSION

MAXIMUM

This is a programmable field specifying the number of retransmission attempts

following a collision before aborting the packet due to excessive collisions. The

Standard specifies the attemptLimit to be 0xF (15d). See IEEE 802.3/4.2.3.2.5.

0xF

7:4 - Reserved. User software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

0x0

13:8 COLLISION

WINDOW

This is a programmable field representing the slot time or collision window during

which collisions occur in properly configured networks. The default value of 0x37

(55d) represents a 56 byte window following the preamble and SFD.

0x37

31:14 - Reserved, user software should not write ones to reserved bits. The value read from

a reserved bit is not defined.

NA

Table 135. Maximum Frame register (MAXF - address 0x5000 0014) bit description

Bit Symbol Function Reset

value

15:0 MAXIMUM FRAME

LENGTH

This field resets to the value 0x0600, which represents a maximum receive frame of

1536 octets. An untagged maximum size Ethernet frame is 1518 octets. A tagged

frame adds four octets for a total of 1522 octets. If a shorter maximum length

restriction is desired, program this 16-bit field.

0x0600

31:16 - Unused 0x0

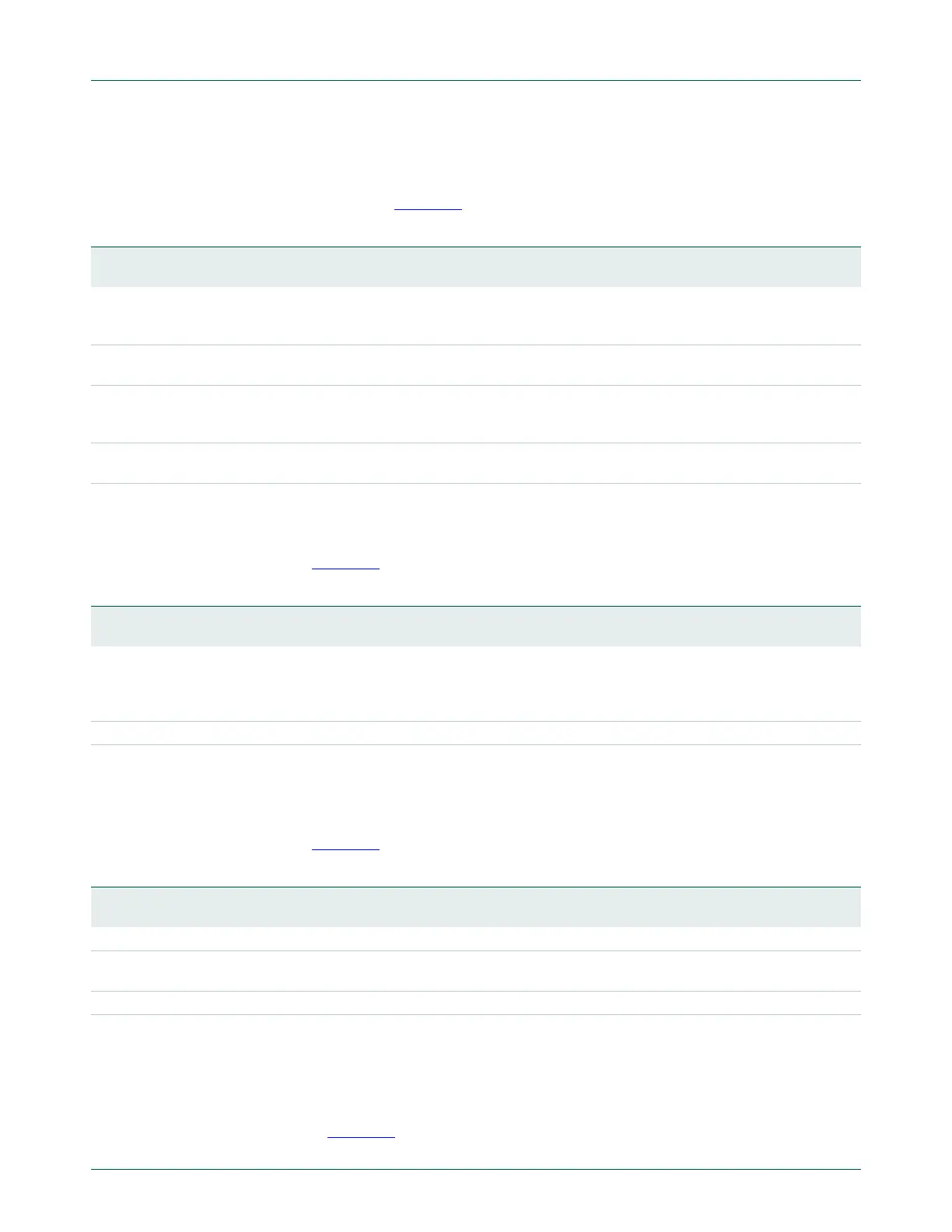

Table 136. PHY Support register (SUPP - address 0x5000 0018) bit description

Bit Symbol Function Reset

value

7:0 - Unused 0x0

8 SPEED This bit configures the Reduced MII logic for the current operating speed. When set,

100 Mbps mode is selected. When cleared, 10 Mbps mode is selected.

0

31:9 - Unused 0x0

Loading...

Loading...