UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 222 of 841

NXP Semiconductors

UM10360

Chapter 11: LPC176x/5x USB device controller

[1] Reset value reflects the data stored in used bits only. It does not include reserved bits content.

[2] Reading WO register will return an invalid value.

11.10.1 Clock control registers

11.10.1.1 USB Clock Control register (USBClkCtrl - 0x5000 CFF4)

This register controls the clocking of the USB Device Controller. Whenever software

wants to access the device controller registers, both DEV_CLK_EN and AHB_CLK_EN

must be set.

The software does not have to repeat this exercise for every register access, provided that

the corresponding USBClkCtrl bits are already set. Note that this register is functional only

when the PCUSB bit of PCONP is set; when PCUSB is cleared, all clocks to the device

controller are disabled irrespective of the contents of this register. USBClkCtrl is a

read/write register.

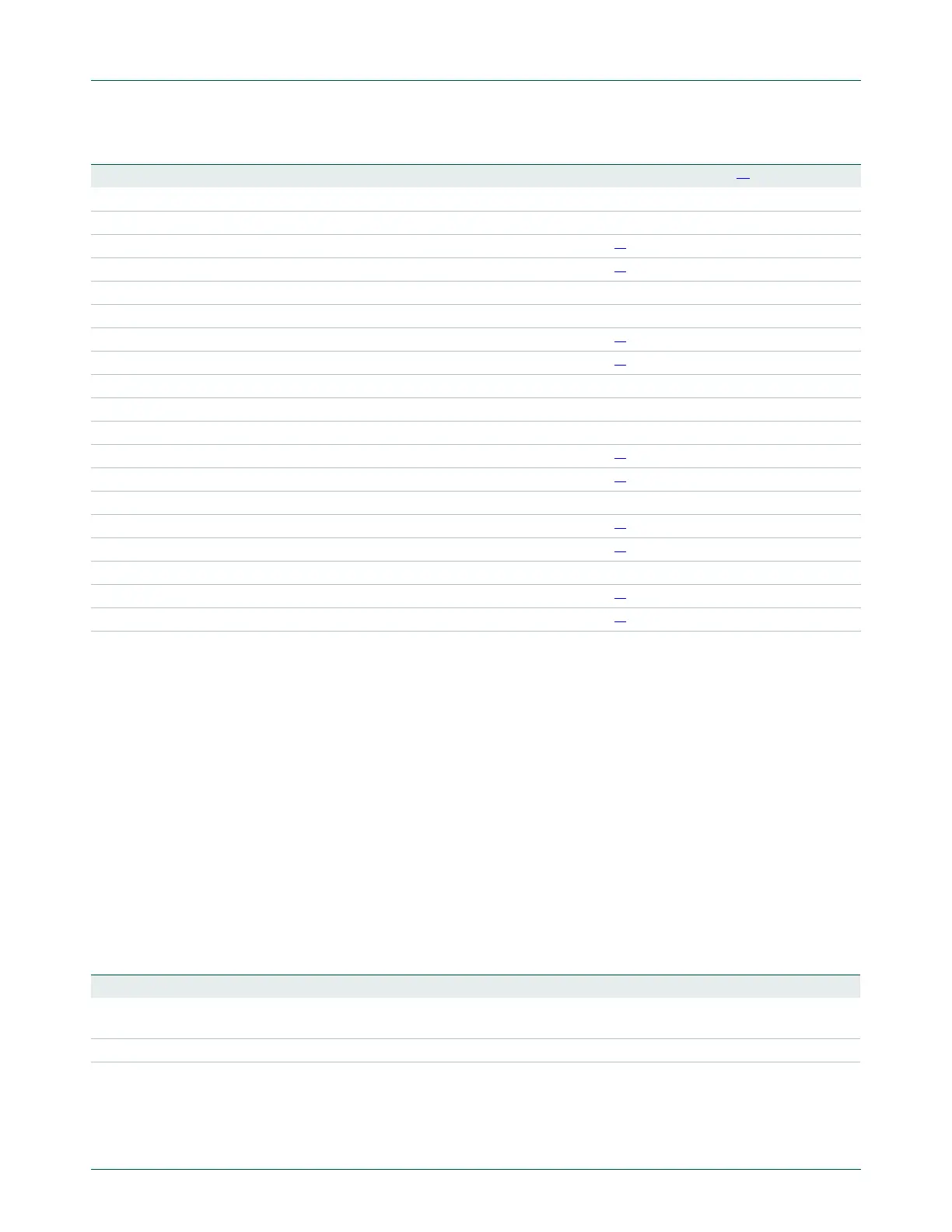

DMA registers

USBDMARSt USB DMA Request Status RO 0 0x5000 C250

USBDMARClr USB DMA Request Clear WO

[2]

0 0x5000 C254

USBDMARSet USB DMA Request Set WO

[2]

0 0x5000 C258

USBUDCAH USB UDCA Head R/W 0 0x5000 C280

USBEpDMASt USB Endpoint DMA Status RO 0 0x5000 C284

USBEpDMAEn USB Endpoint DMA Enable WO

[2]

0 0x5000 C288

USBEpDMADis USB Endpoint DMA Disable WO

[2]

0 0x5000 C28C

USBDMAIntSt USB DMA Interrupt Status RO 0 0x5000 C290

USBDMAIntEn USB DMA Interrupt Enable R/W 0 0x5000 C294

USBEoTIntSt USB End of Transfer Interrupt Status RO 0 0x5000 C2A0

USBEoTIntClr USB End of Transfer Interrupt Clear WO

[2]

0 0x5000 C2A4

USBEoTIntSet USB End of Transfer Interrupt Set WO

[2]

0 0x5000 C2A8

USBNDDRIntSt USB New DD Request Interrupt Status RO 0 0x5000 C2AC

USBNDDRIntClr USB New DD Request Interrupt Clear WO

[2]

0 0x5000 C2B0

USBNDDRIntSet USB New DD Request Interrupt Set WO

[2]

0 0x5000 C2B4

USBSysErrIntSt USB System Error Interrupt Status RO 0 0x5000 C2B8

USBSysErrIntClr USB System Error Interrupt Clear WO

[2]

0 0x5000 C2BC

USBSysErrIntSet USB System Error Interrupt Set WO

[2]

0 0x5000 C2C0

Table 188. USB device register map …continued

Name Description Access Reset value

[1]

Address

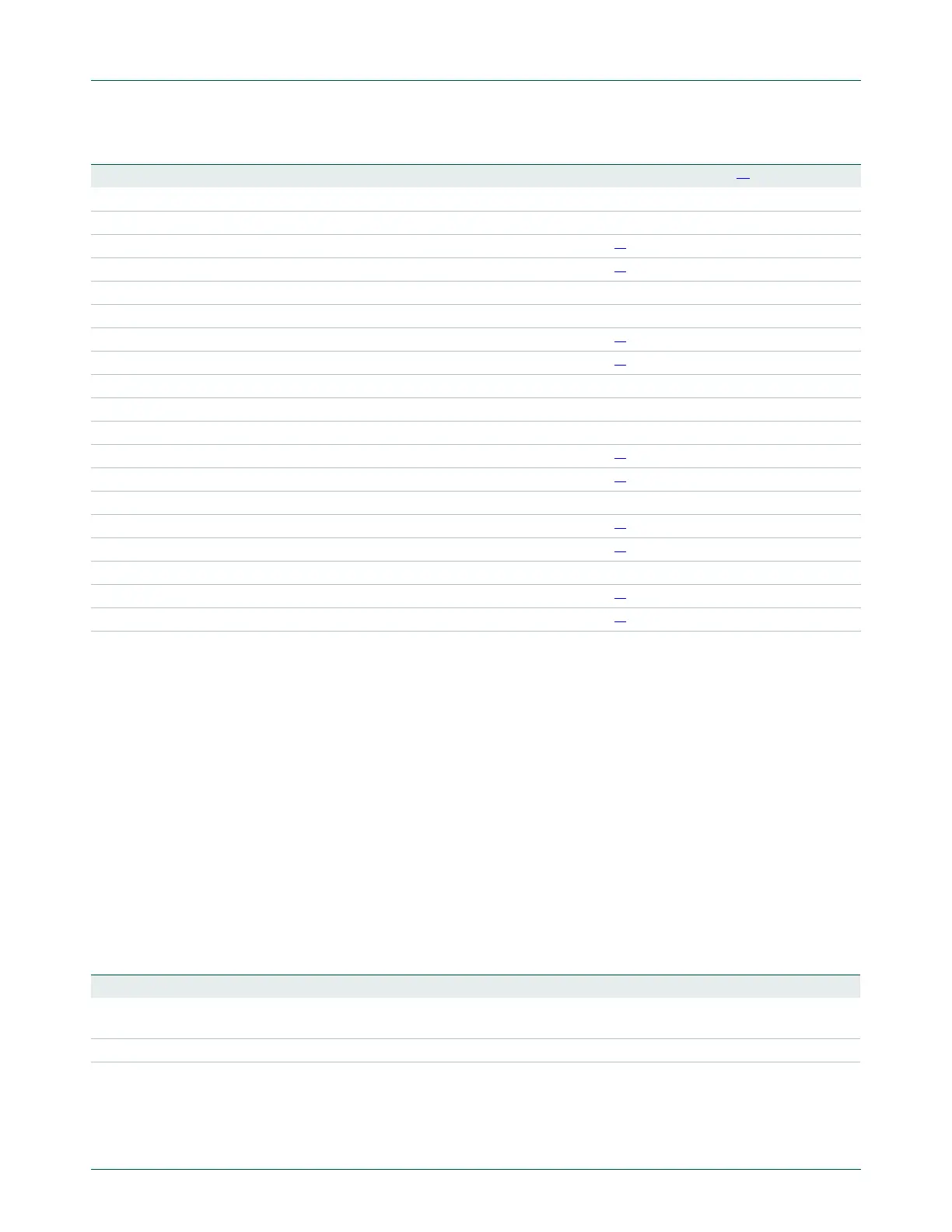

Table 189. USBClkCtrl register (USBClkCtrl - address 0x5000 CFF4) bit description

Bit Symbol Description Reset value

0 - Reserved, user software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

NA

1 DEV_CLK_EN Device clock enable. Enables the usbclk input to the device controller 0

2 - Reserved, user software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

NA

Loading...

Loading...