UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 57 of 841

NXP Semiconductors

UM10360

Chapter 4: LPC176x/5x Clocking and power control

4.7.3 Peripheral Clock Selection registers 0 and 1 (PCLKSEL0 -

0x400F C1A8 and PCLKSEL1 - 0x400F C1AC)

A pair of bits in a Peripheral Clock Selection register controls the rate of the clock signal

that will be supplied to the corresponding peripheral as specified in Table 40

, Table 41 and

Table 42

.

Remark: The peripheral clock for the RTC block is fixed at CCLK/8.

[1] PCLK_CAN1 and PCLK_CAN2 must have the same PCLK divide value when the CAN function is used.

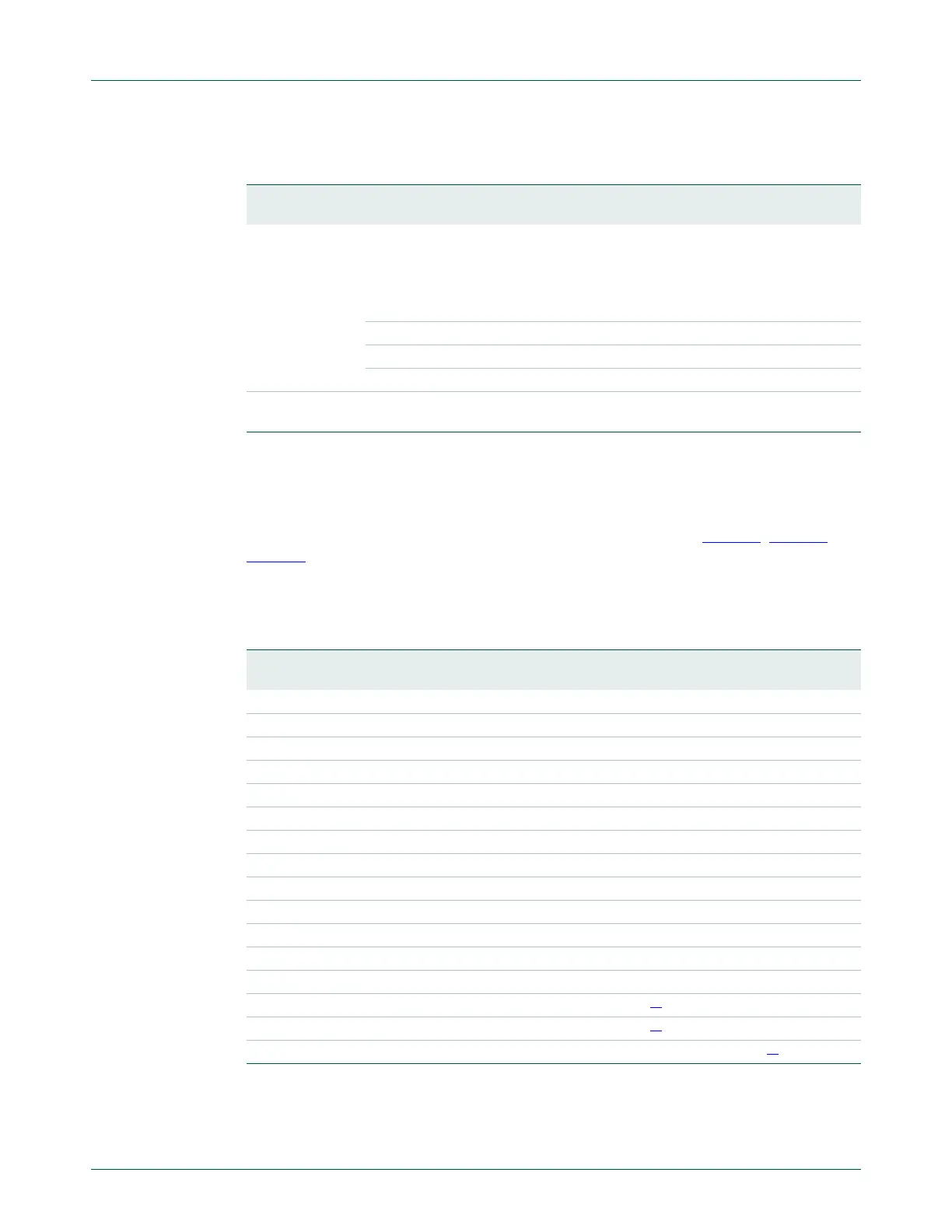

Table 39. USB Clock Configuration register (USBCLKCFG - address 0x400F C108) bit

description

Bit Symbol Value Description Reset

value

3:0 USBSEL Selects the divide value for creating the USB clock from the

PLL0 output. Only the values shown below can produce even

number multiples of 48 MHz from the PLL0 output.

Warning: Improper setting of this value will result in incorrect

operation of the USB interface.

0

5 PLL0 output is divided by 6. PLL0 output must be 288 MHz.

7 PLL0 output is divided by 8. PLL0 output must be 384 MHz.

9 PLL0 output is divided by 10. PLL0 output must be 480 MHz.

31:4 - Reserved, user software should not write ones to reserved

bits. The value read from a reserved bit is not defined.

NA

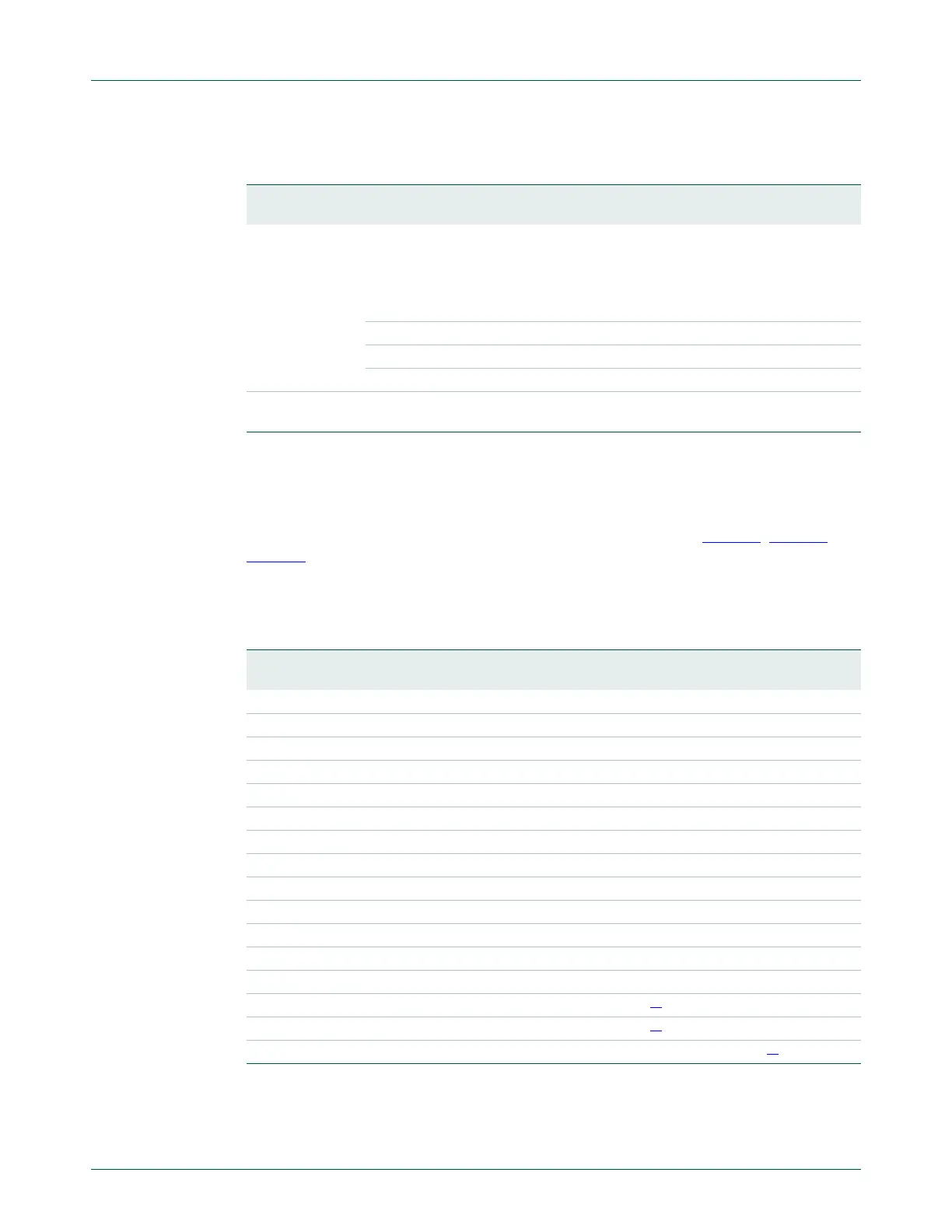

Table 40. Peripheral Clock Selection register 0 (PCLKSEL0 - address 0x400F C1A8) bit

description

Bit Symbol Description Reset

value

1:0 PCLK_WDT Peripheral clock selection for WDT. 00

3:2 PCLK_TIMER0 Peripheral clock selection for TIMER0. 00

5:4 PCLK_TIMER1 Peripheral clock selection for TIMER1. 00

7:6 PCLK_UART0 Peripheral clock selection for UART0. 00

9:8 PCLK_UART1 Peripheral clock selection for UART1. 00

11:10 - Reserved. NA

13:12 PCLK_PWM1 Peripheral clock selection for PWM1. 00

15:14 PCLK_I2C0 Peripheral clock selection for I

2

C0. 00

17:16 PCLK_SPI Peripheral clock selection for SPI. 00

19:18 - Reserved. NA

21:20 PCLK_SSP1 Peripheral clock selection for SSP1. 00

23:22 PCLK_DAC Peripheral clock selection for DAC. 00

25:24 PCLK_ADC Peripheral clock selection for ADC. 00

27:26 PCLK_CAN1 Peripheral clock selection for CAN1.

[1]

00

29:28 PCLK_CAN2 Peripheral clock selection for CAN2.

[1]

00

31:30 PCLK_ACF Peripheral clock selection for CAN acceptance filtering.

[1]

00

Loading...

Loading...