UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 58 of 841

NXP Semiconductors

UM10360

Chapter 4: LPC176x/5x Clocking and power control

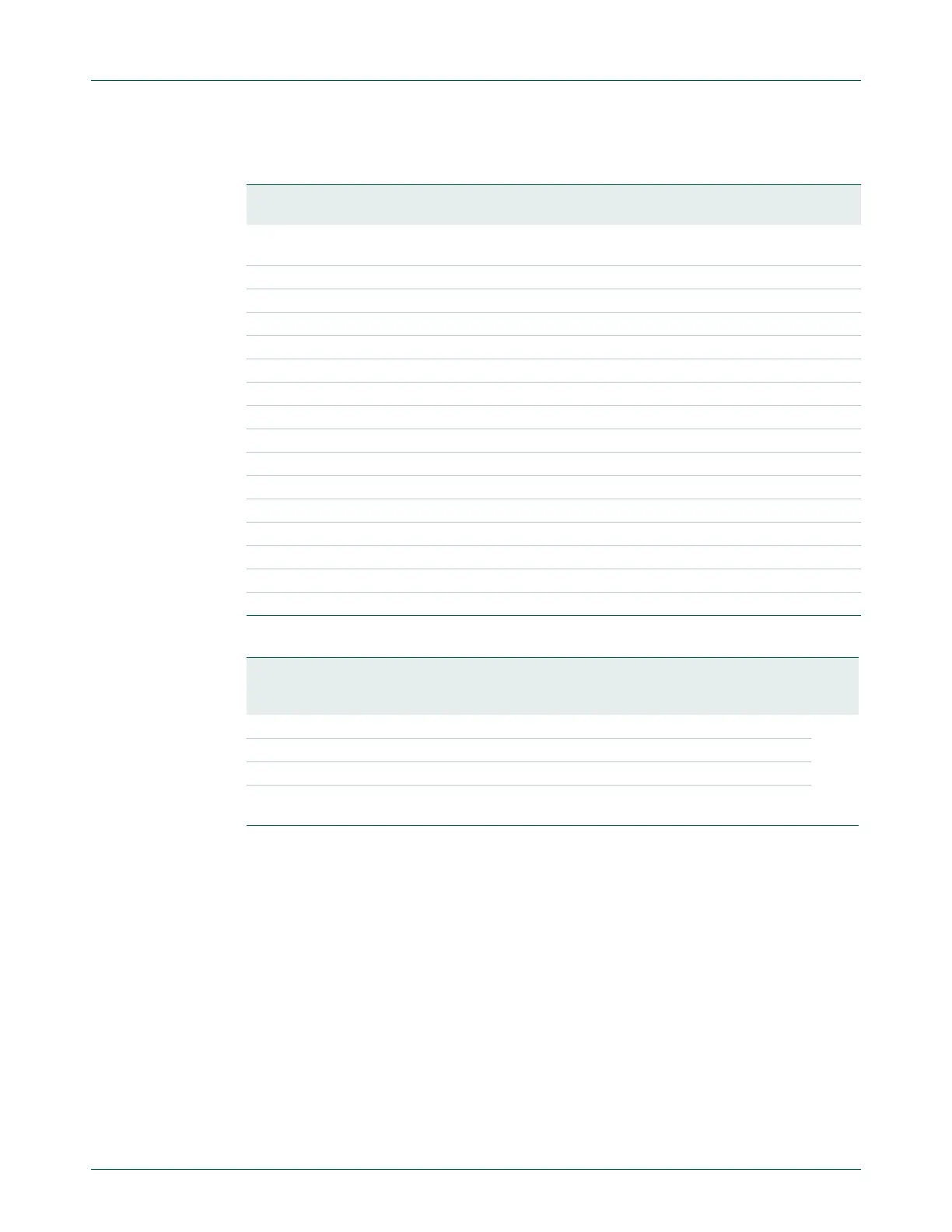

Table 41. Peripheral Clock Selection register 1 (PCLKSEL1 - address 0x400F C1AC) bit

description

Bit Symbol Description Reset

value

1:0 PCLK_QEI Peripheral clock selection for the Quadrature Encoder

Interface.

00

3:2 PCLK_GPIOINT Peripheral clock selection for GPIO interrupts. 00

5:4 PCLK_PCB Peripheral clock selection for the Pin Connect block. 00

7:6 PCLK_I2C1 Peripheral clock selection for I

2

C1. 00

9:8 - Reserved. NA

11:10 PCLK_SSP0 Peripheral clock selection for SSP0. 00

13:12 PCLK_TIMER2 Peripheral clock selection for TIMER2. 00

15:14 PCLK_TIMER3 Peripheral clock selection for TIMER3. 00

17:16 PCLK_UART2 Peripheral clock selection for UART2. 00

19:18 PCLK_UART3 Peripheral clock selection for UART3. 00

21:20 PCLK_I2C2 Peripheral clock selection for I

2

C2. 00

23:22 PCLK_I2S Peripheral clock selection for I

2

S. 00

25:24 - Reserved. NA

27:26 PCLK_RIT Peripheral clock selection for Repetitive Interrupt Timer. 00

29:28 PCLK_SYSCON Peripheral clock selection for the System Control block. 00

31:30 PCLK_MC Peripheral clock selection for the Motor Control PWM. 00

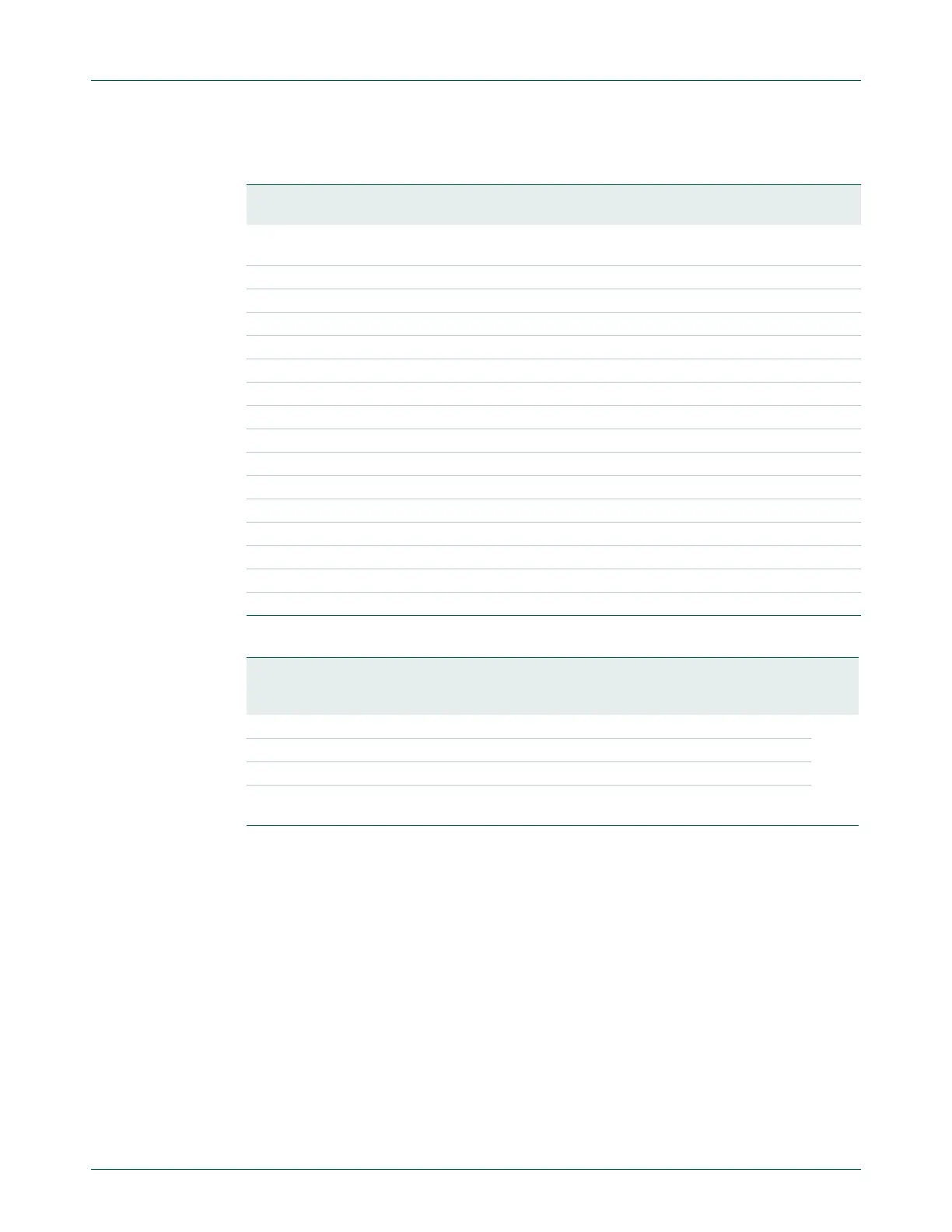

Table 42. Peripheral Clock Selection register bit values

PCLKSEL0 and PCLKSEL1

individual peripheral’s clock

select options

Function Reset

value

00 PCLK_peripheral = CCLK/4 00

01 PCLK_peripheral = CCLK

10 PCLK_peripheral = CCLK/2

11 PCLK_peripheral = CCLK/8, except for CAN1, CAN2, and

CAN filtering when “11” selects = CCLK/6.

Loading...

Loading...