UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 215 of 841

NXP Semiconductors

UM10360

Chapter 11: LPC176x/5x USB device controller

11.4 Features

• Fully compliant with the USB 2.0 specification (full speed).

• Supports 32 physical (16 logical) endpoints.

• Supports Control, Bulk, Interrupt and Isochronous endpoints.

• Scalable realization of endpoints at run time.

• Endpoint maximum packet size selection (up to USB maximum specification) by

software at run time.

• Supports SoftConnect and GoodLink features.

• Supports DMA transfers on all non-control endpoints.

• Allows dynamic switching between CPU controlled and DMA modes.

• Double buffer implementation for Bulk and Isochronous endpoints.

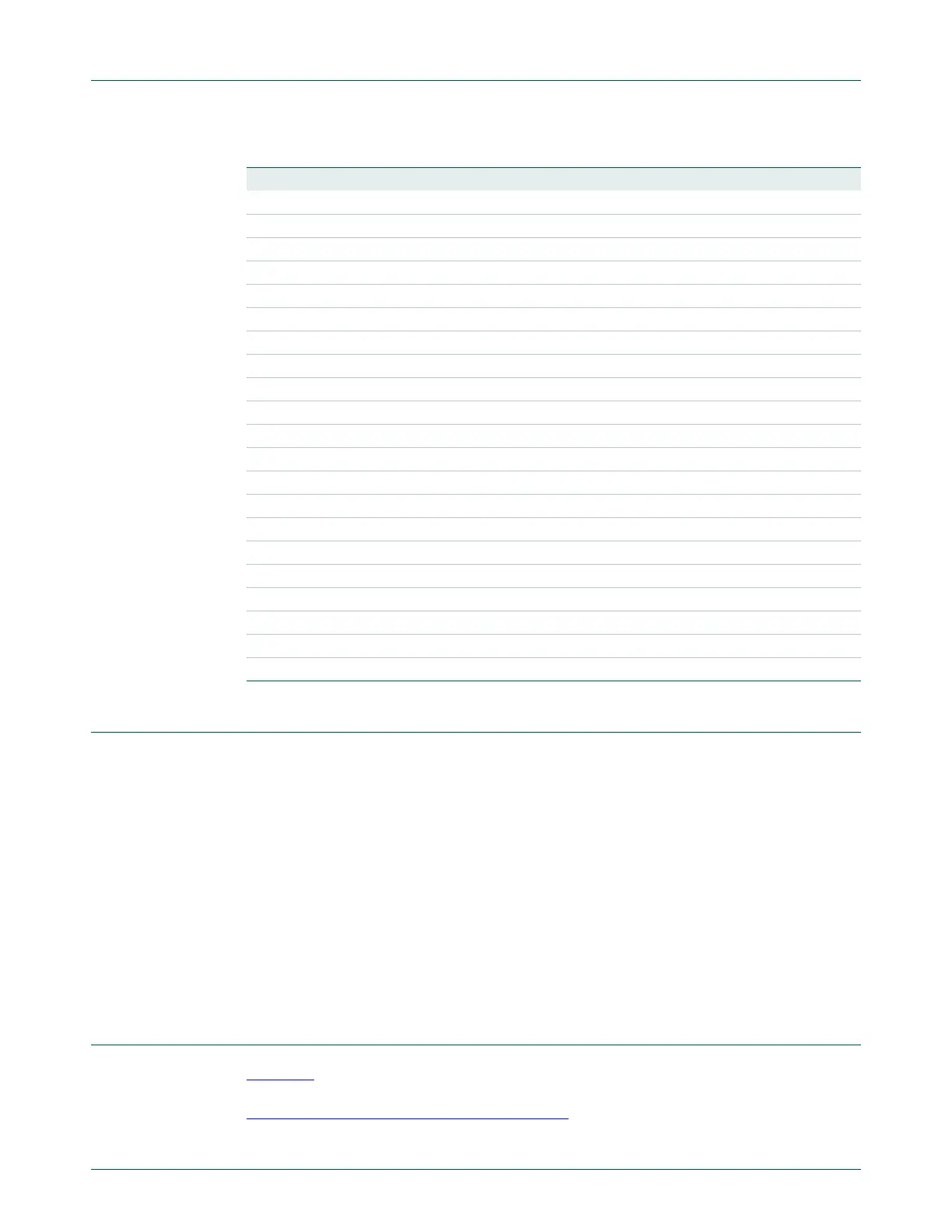

11.5 Fixed endpoint configuration

Table 185 shows the supported endpoint configurations. Endpoints are realized and

configured at run time using the Endpoint realization registers, documented in

Section 11.10.4 “

Endpoint realization registers”.

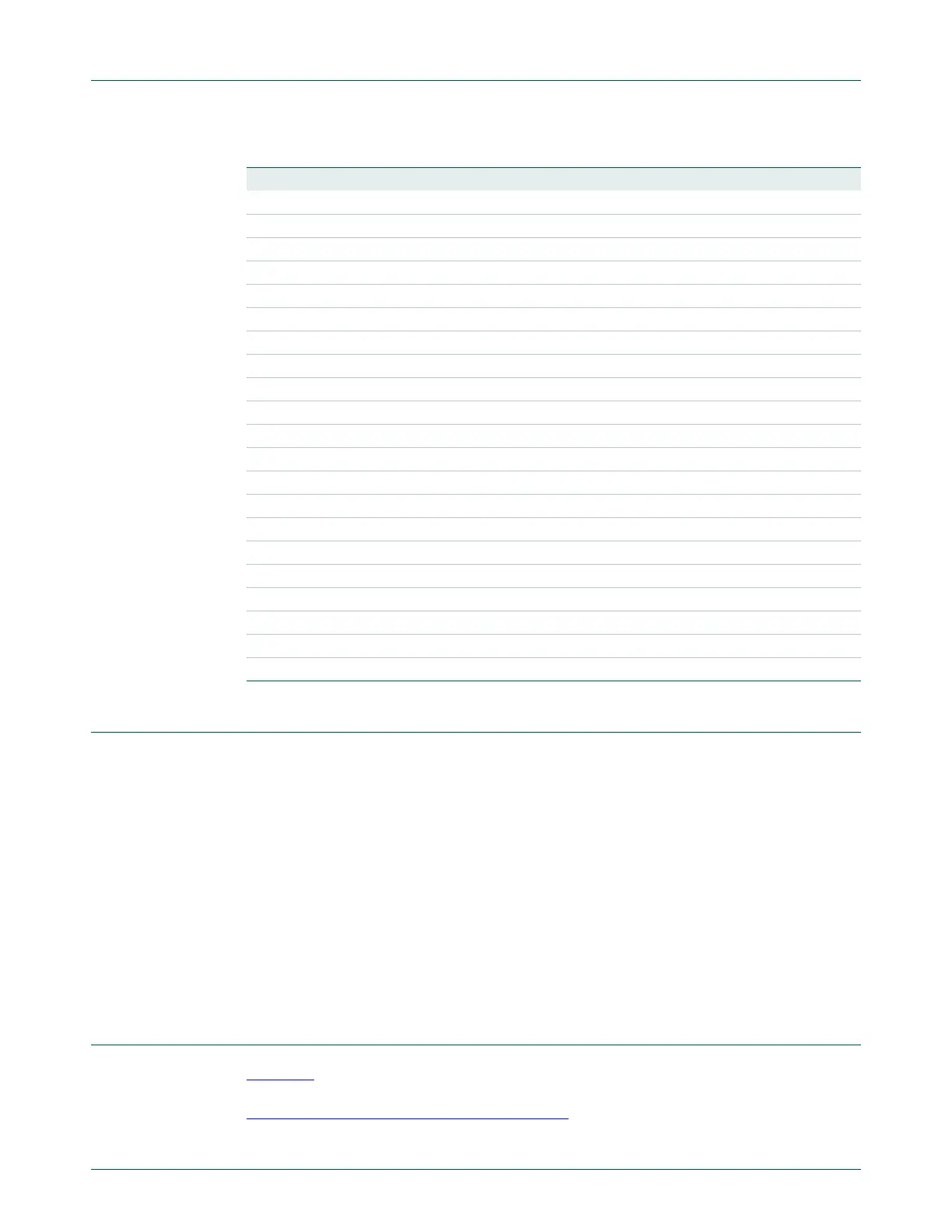

Table 184. USB related acronyms, abbreviations, and definitions used in this chapter

Acronym/abbreviation Description

AHB Advanced High-performance bus

ATLE Auto Transfer Length Extraction

ATX Analog Transceiver

DD DMA Descriptor

DDP DMA Description Pointer

DMA Direct Memory Access

EOP End-Of-Packet

EP Endpoint

EP_RAM Endpoint RAM

FS Full Speed

LED Light Emitting Diode

LS Low Speed

MPS Maximum Packet Size

NAK Negative Acknowledge

PLL Phase Locked Loop

RAM Random Access Memory

SOF Start-Of-Frame

SIE Serial Interface Engine

SRAM Synchronous RAM

UDCA USB Device Communication Area

USB Universal Serial Bus

Loading...

Loading...