UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 527 of 841

NXP Semiconductors

UM10360

Chapter 25: LPC176x/5x Motor control PWM

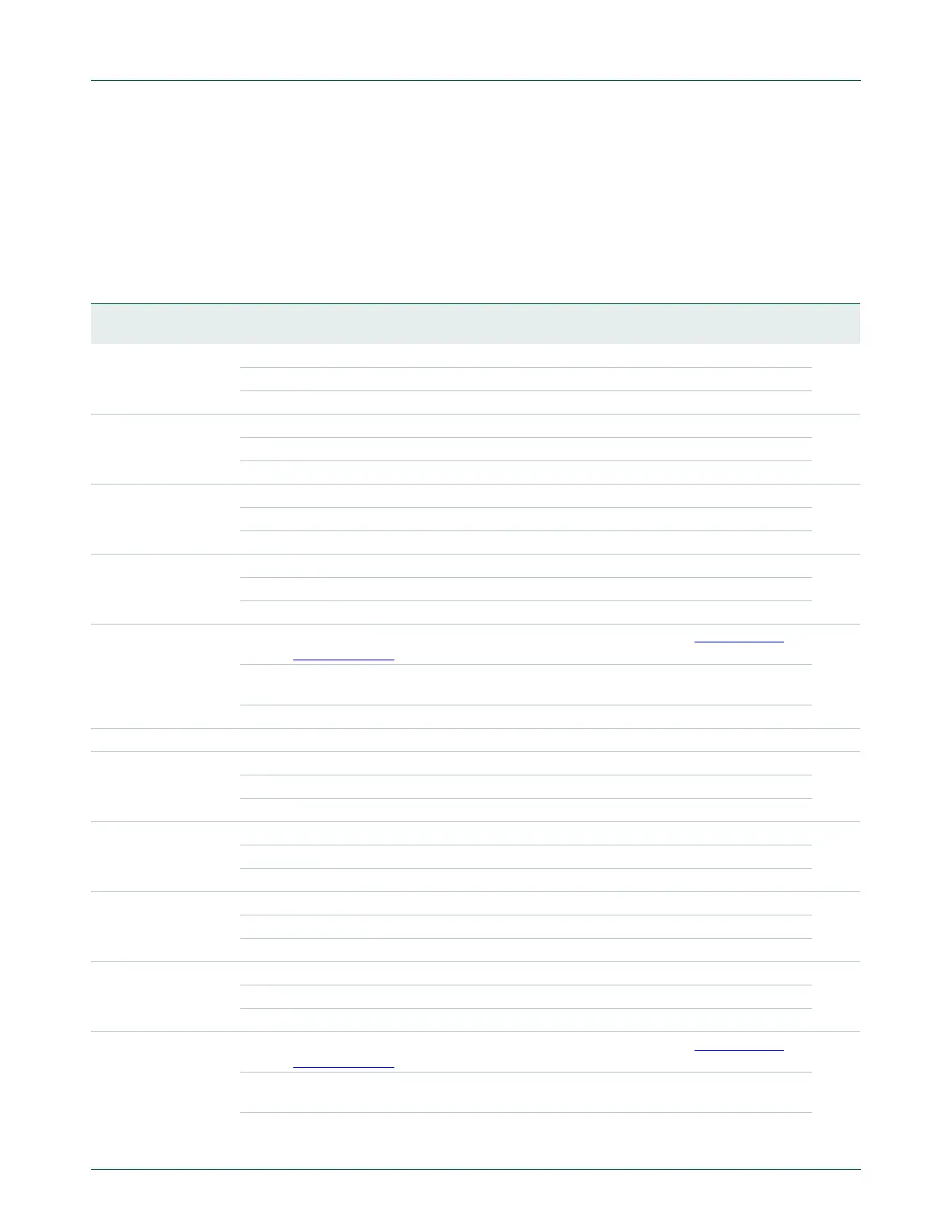

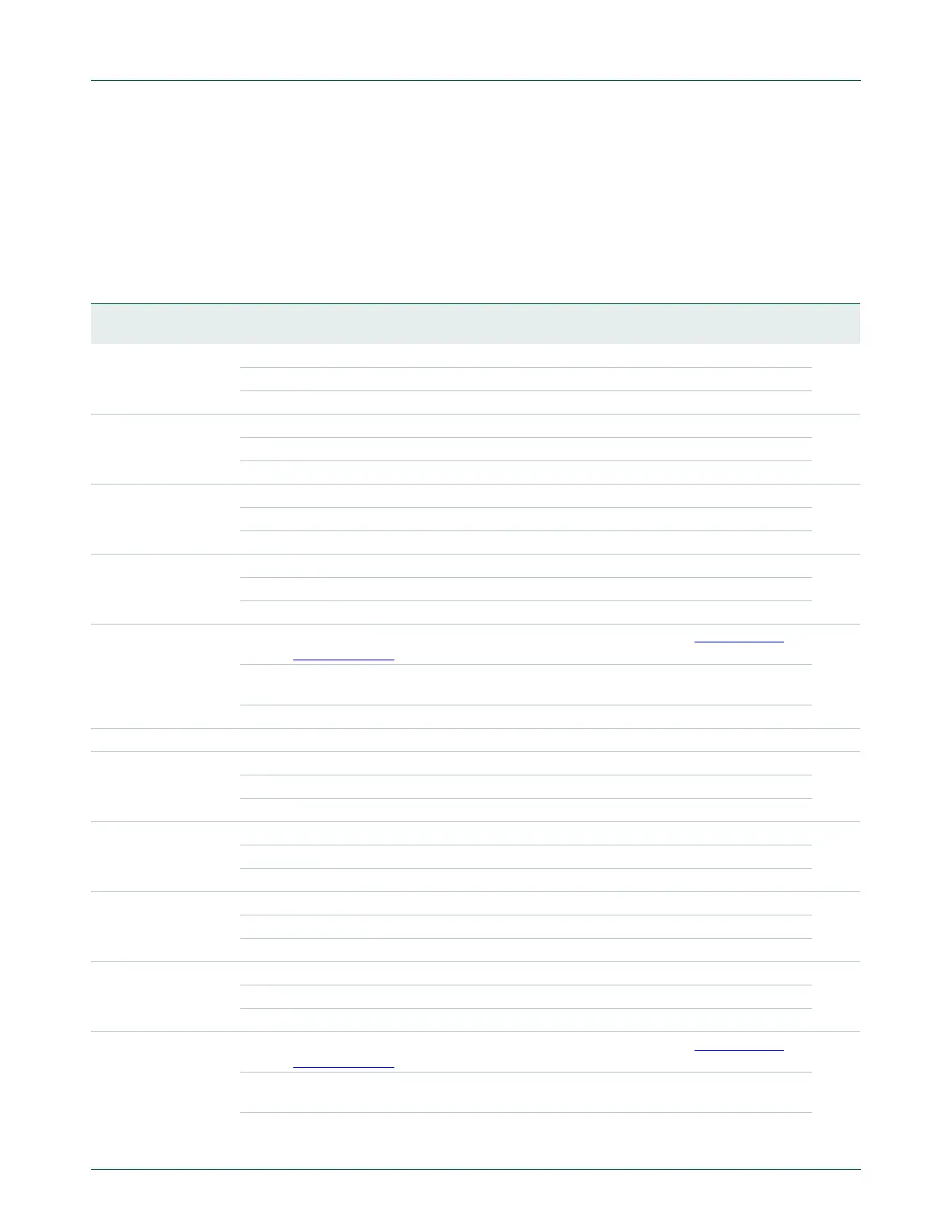

25.7.1 MCPWM Control register

25.7.1.1 MCPWM Control read address (MCCON - 0x400B 8000)

The MCCON register controls the operation of all channels of the PWM. This address is

read-only, but the underlying register can be modified by writing to addresses

MCCON_SET and MCCON_CLR.

Table 455. MCPWM Control read address (MCCON - 0x400B 8000) bit description

Bit Symbol Value Description Reset

value

0 RUN0 Stops/starts timer channel 0. 0

0Stop.

1Run.

1 CENTER0 Edge/center aligned operation for channel 0. 0

0 Edge-aligned.

1 Center-aligned.

2 POLA0 Selects polarity of the MCOA0 and MCOB0 pins. 0

0 Passive state is LOW, active state is HIGH.

1 Passive state is HIGH, active state is LOW.

3 DTE0 Controls the dead-time feature for channel 0. 0

0 Dead-time disabled.

1 Dead-time enabled.

4 DISUP0 Enable/disable updates of functional registers for channel 0 (see Section 25.8.2

,

Section 25.7.6.1

).

0

0 Functional registers are updated from the write registers at the end of each PWM

cycle.

1 Functional registers remain the same as long as the timer is running.

7:5 - - Reserved.

8 RUN1 Stops/starts timer channel 1. 0

0Stop.

1Run.

9 CENTER1 Edge/center aligned operation for channel 1. 0

0 Edge-aligned.

1 Center-aligned.

10 POLA1 Selects polarity of the MCOA1 and MCOB1 pins. 0

0 Passive state is LOW, active state is HIGH.

1 Passive state is HIGH, active state is LOW.

11 DTE1 Controls the dead-time feature for channel 1. 0

0 Dead-time disabled.

1 Dead-time enabled.

12 DISUP1 Enable/disable updates of functional registers for channel 1 (see Section 25.8.2

,

Section 25.7.6.1

).

0

0 Functional registers are updated from the write registers at the end of each PWM

cycle.

1 Functional registers remain the same as long as the timer is running.

Loading...

Loading...