UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 159 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

The station address is used for perfect address filtering and for sending pause control

frames. For the ordering of the octets in the packet please refer to Figure 18

.

10.12 Control register definitions

10.12.1 Command Register (Command - 0x5000 0100)

The Command register (Command) register has an address of 0x5000 0100. Its bit

definition is shown in Table 148

.

All bits can be written and read. The Tx/RxReset bits are write-only, reading will return a 0.

10.12.2 Status Register (Status - 0x5000 0104)

The Status register (Status) is a read-only register with an address of 0x5000 0104. Its bit

definition is shown in Table 149

.

The values represent the status of the two channels/data paths. When the status is 1, the

channel is active, meaning:

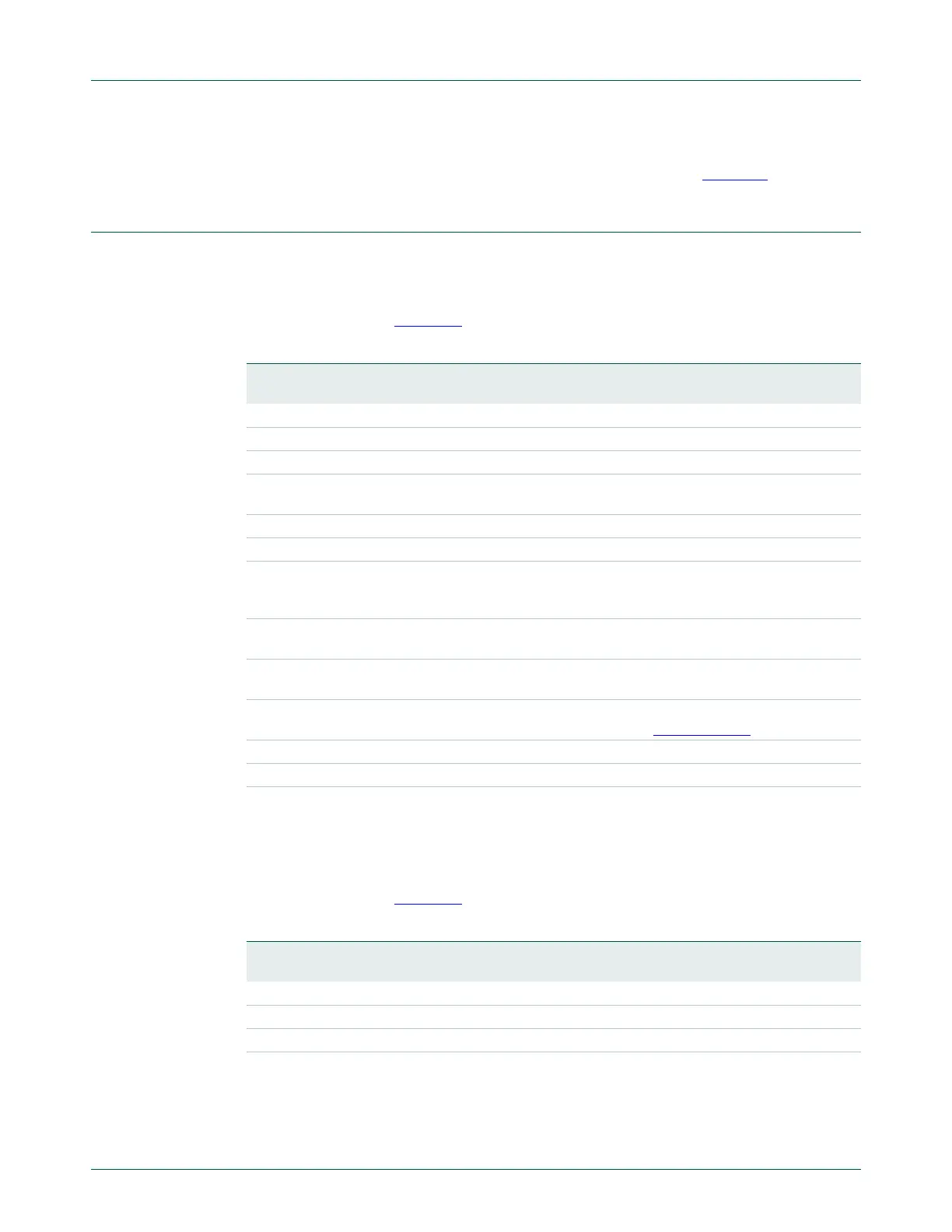

Table 148. Command register (Command - address 0x5000 0100) bit description

Bit Symbol Function Reset

value

0 RxEnable Enable receive. 0

1 TxEnable Enable transmit. 0

2 - Unused 0x0

3 RegReset When a ’1’ is written, all datapaths and the host registers are

reset. The MAC needs to be reset separately.

0

4 TxReset When a ’1’ is written, the transmit datapath is reset. 0

5 RxReset When a ’1’ is written, the receive datapath is reset. 0

6 PassRuntFrame When set to ’1’, passes runt frames smaller than 64 bytes to

memory unless they have a CRC error. If ’0’ runt frames are

filtered out.

0

7 PassRxFilter When set to ’1’, disables receive filtering i.e. all frames

received are written to memory.

0

8 TxFlowControl Enable IEEE 802.3 / clause 31 flow control sending pause

frames in full duplex and continuous preamble in half duplex.

0

9 RMII When set to “1”, RMII mode is selected. This bit must be set to

one during Ethernet initialization. See Section 10.17.2

.

0

10 FullDuplex When set to “1”, indicates full duplex operation. 0

31:11 - Unused 0x0

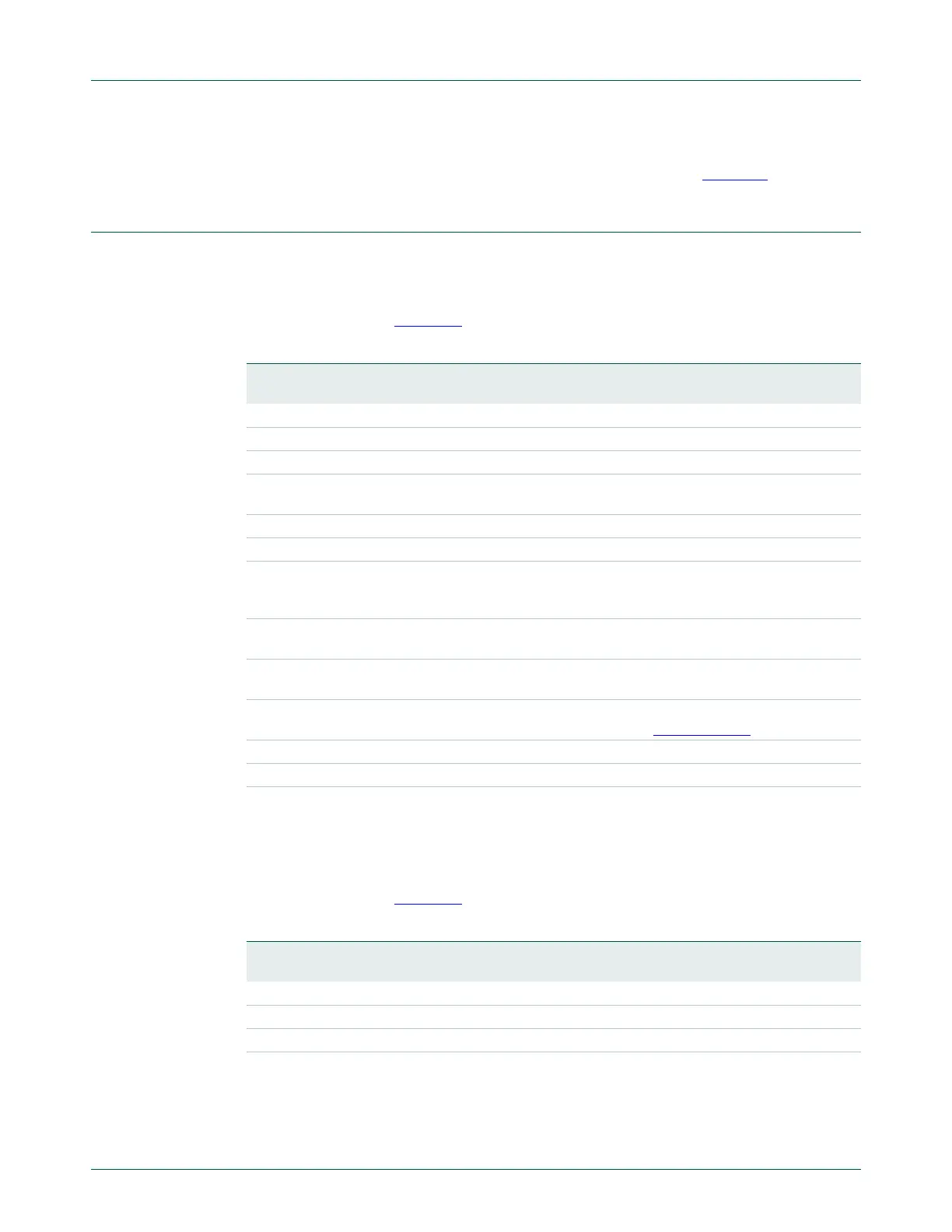

Table 149. Status register (Status - address 0x5000 0104) bit description

Bit Symbol Function Reset

value

0 RxStatus If 1, the receive channel is active. If 0, the receive channel is inactive. 0

1 TxStatus If 1, the transmit channel is active. If 0, the transmit channel is inactive. 0

31:2 - Unused 0x0

Loading...

Loading...