UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 62 of 841

NXP Semiconductors

UM10360

Chapter 4: LPC176x/5x Clocking and power control

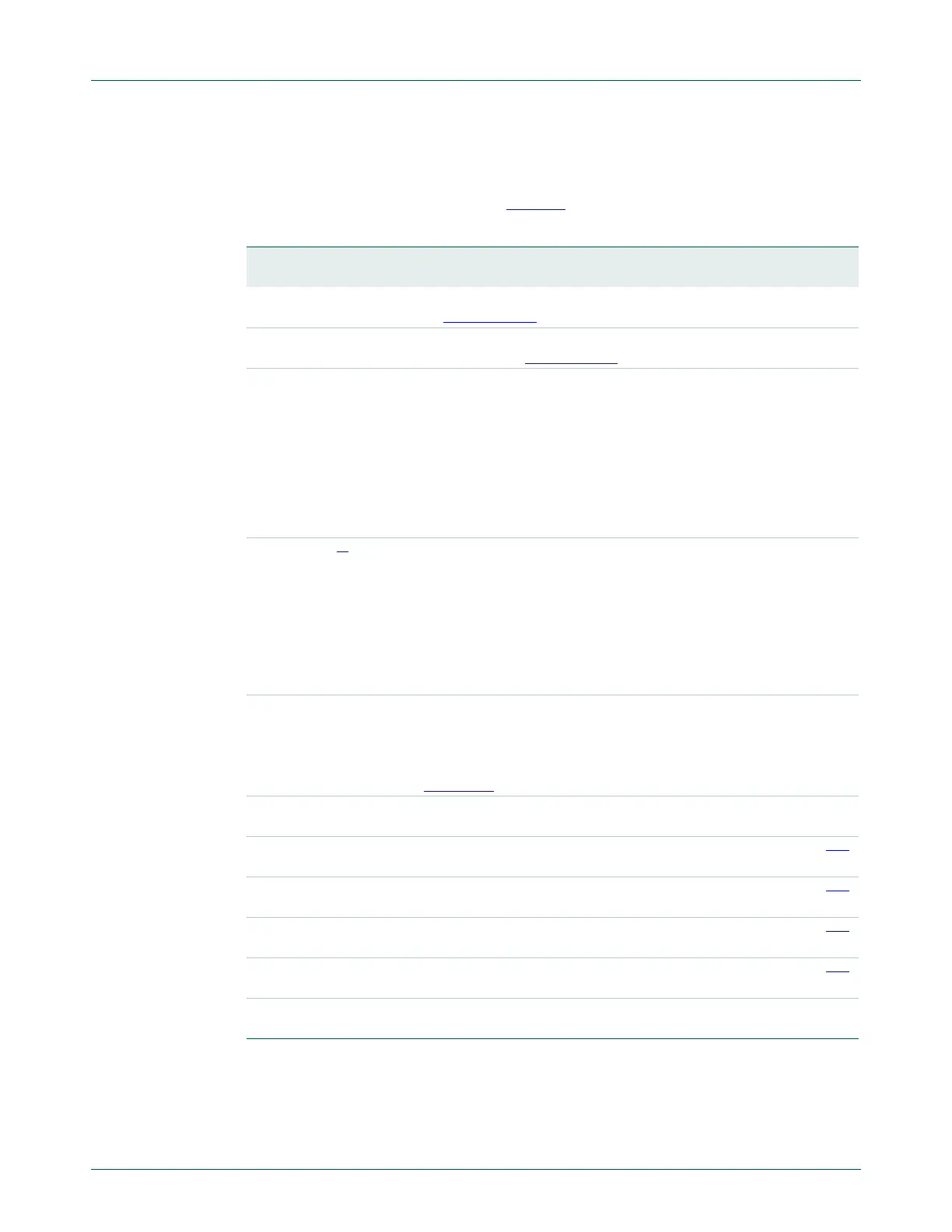

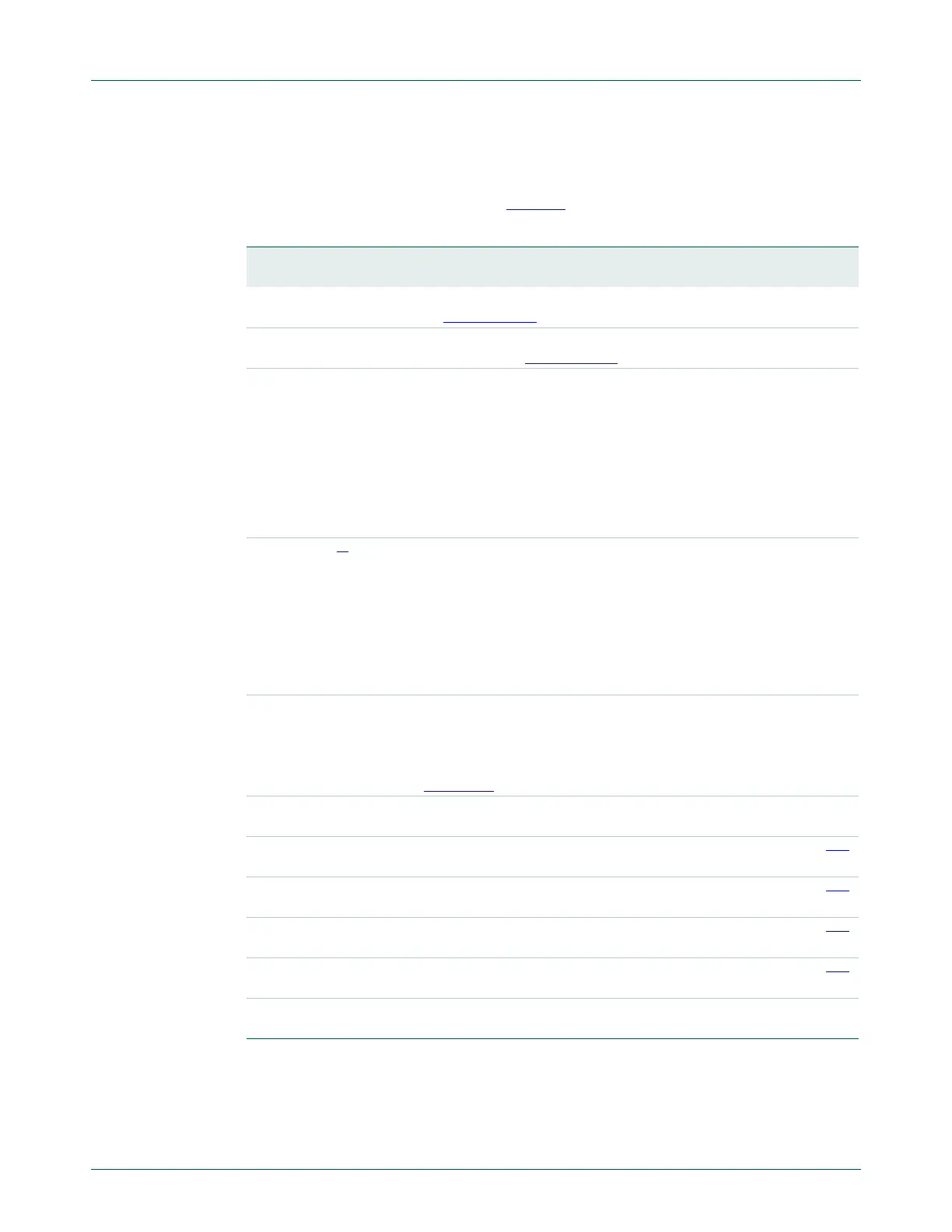

4.8.7 Power Mode Control register (PCON - 0x400F C0C0)

Controls for some reduced power modes and other power related controls are contained

in the PCON register, as described in Table 44

.

[1] BOD reset (BORD- bit 4 in PCON register) and BOD interrupt needs to be disabled before a user disables

or enables the power to BOD (BOGD - bit 3 in PCON register).

[2] Only one of these flags will be valid at a specific time.

[3] Hardware reset only for a power-up of core power or by a brownout detect event.

[4] Hardware reset only for a power-up event on Vbat.

Table 44. Power Mode Control register (PCON - address 0x400F C0C0) bit description

Bit Symbol Description Reset

value

0 PM0 Power mode control bit 0. This bit controls entry to the Power-down

mode. See Section 4.8.7.1

below for details.

0

1 PM1 Power mode control bit 1. This bit controls entry to the Deep

Power-down mode. See Section 4.8.7.1

below for details.

0

2 BODRPM Brown-Out Reduced Power Mode. When BODRPM is 1, the

Brown-Out Detect circuitry will be turned off when chip Power-down

mode or Deep Sleep mode is entered, resulting in a further reduction

in power usage. However, the possibility of using Brown-Out Detect as

a wake-up source from the reduced power mode will be lost.

When 0, the Brown-Out Detect function remains active during

Power-down and Deep Sleep modes.

See the System Control Block chapter for details of Brown-Out

detection.

0

3BOGD

[1]

Brown-Out Global Disable. When BOGD is 1, the Brown-Out Detect

circuitry is fully disabled at all times, and does not consume power.

When 0, the Brown-Out Detect circuitry is enabled.

See the System Control Block chapter for details of Brown-Out

detection.

Note: the Brown-Out Reset Disable (BORD, in this register) and the

Brown-Out Interrupt (xx) must be disabled when software changes the

value of this bit.

0

4 BORD Brown-Out Reset Disable. When BORD is 1, the BOD will not reset

the device when the V

DD(REG)(3V3)

voltage dips goes below the BOD

reset trip level. The Brown-Out interrupt is not affected.

When BORD is 0, the BOD reset is enabled.

See the Section 3.5

for details of Brown-Out detection.

0

7:3 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

8 SMFLAG Sleep Mode entry flag. Set when the Sleep mode is successfully

entered. Cleared by software writing a one to this bit.

0

[2][3]

9 DSFLAG Deep Sleep entry flag. Set when the Deep Sleep mode is successfully

entered. Cleared by software writing a one to this bit.

0

[2][3]

10 PDFLAG Power-down entry flag. Set when the Power-down mode is

successfully entered. Cleared by software writing a one to this bit.

0

[2][3]

11 DPDFLAG Deep Power-down entry flag. Set when the Deep Power-down mode

is successfully entered. Cleared by software writing a one to this bit.

0

[2][4]

31:12 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Loading...

Loading...