UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 35 of 841

NXP Semiconductors

UM10360

Chapter 4: LPC176x/5x Clocking and power control

4.4 Clock source selection multiplexer

Several clock sources may be chosen to drive PLL0 and ultimately the CPU and on-chip

peripheral devices. The clock sources available are the main oscillator, the RTC oscillator,

and the Internal RC oscillator.

The clock source selection can only be changed safely when PLL0 is not connected. For a

detailed description of how to change the clock source in a system using PLL0 see

Section 4.5.13 “

PLL0 setup sequence”.

Note the following restrictions regarding the choice of clock sources:

• Only the main oscillator must be used (via PLL0) as the clock source for the USB

subsystem. The IRC or RTC oscillators do not provide the proper tolerances for this

use.

• The IRC oscillator should not be used (via PLL0) as the clock source for the CAN

controllers if the CAN baud rate is higher than 100 kbit/s.

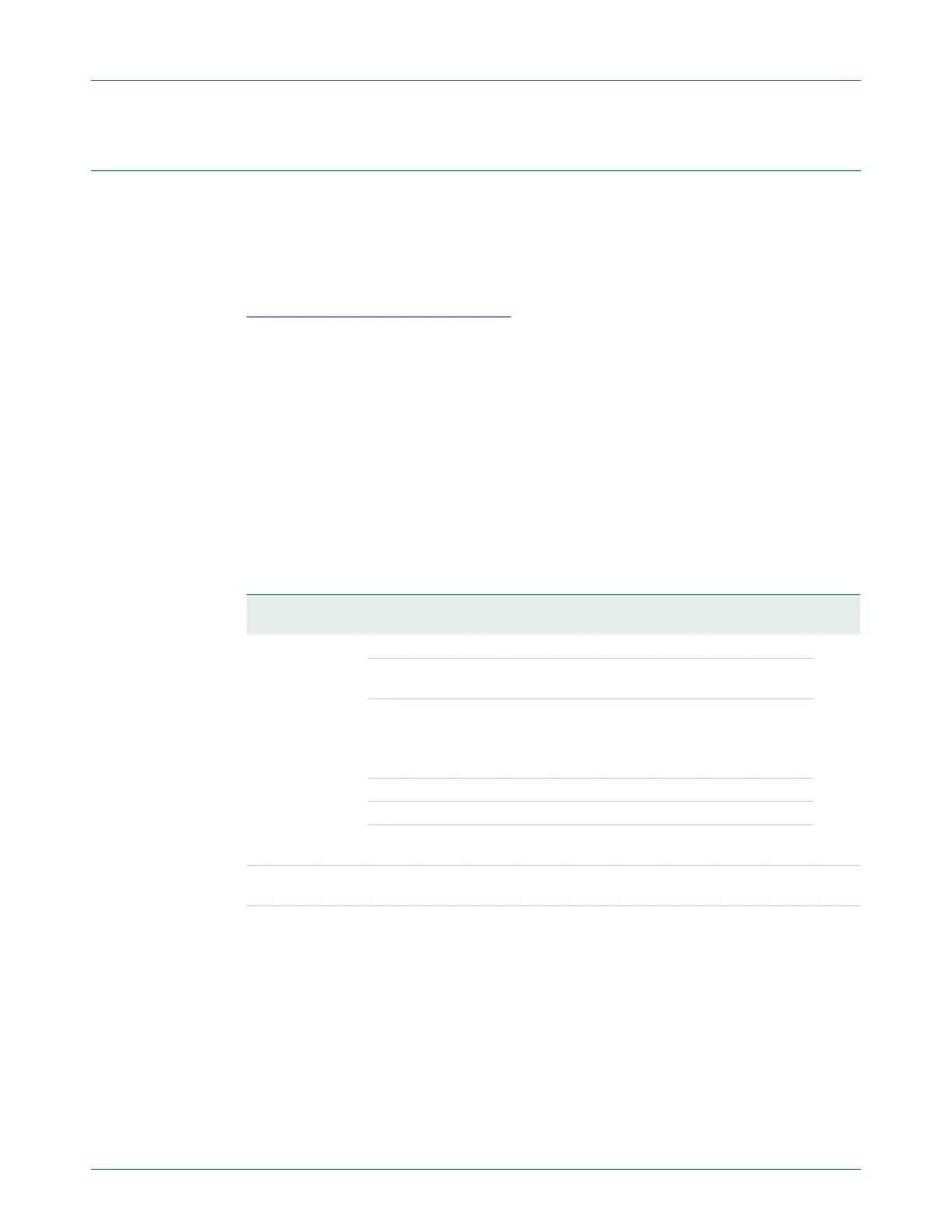

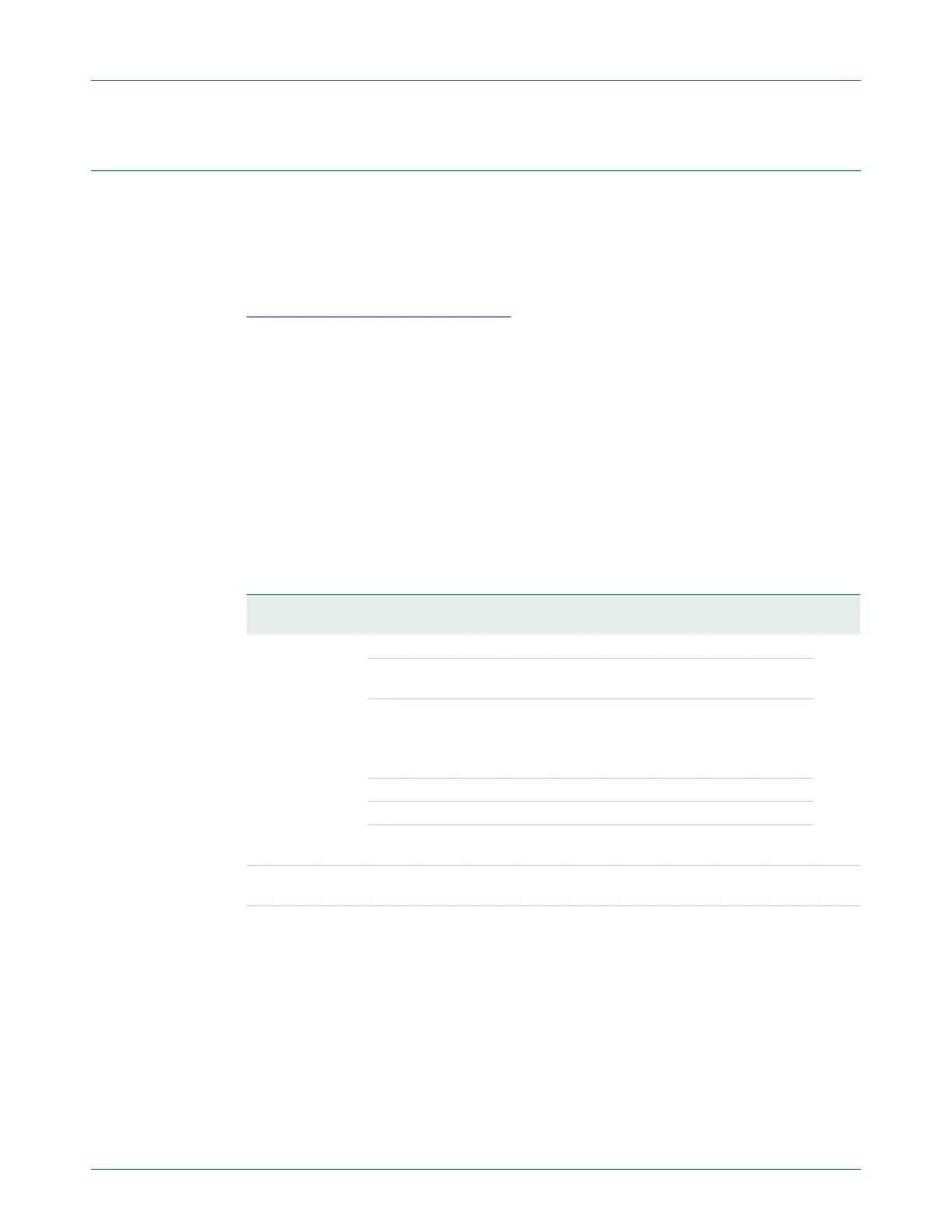

4.4.1 Clock Source Select register (CLKSRCSEL - 0x400F C10C)

The CLKSRCSEL register contains the bits that select the clock source for PLL0.

Table 17. Clock Source Select register (CLKSRCSEL - address 0x400F C10C) bit

description

Bit Symbol Value Description Reset

value

1:0 CLKSRC Selects the clock source for PLL0 as follows: 0

00 Selects the Internal RC oscillator as the PLL0 clock source

(default).

01 Selects the main oscillator as the PLL0 clock source.

Remark: Select the main oscillator as PLL0 clock source if the

PLL0 clock output is used for USB or for CAN with baudrates

> 100 kBit/s.

10 Selects the RTC oscillator as the PLL0 clock source.

11 Reserved, do not use this setting.

Warning: Improper setting of this value, or an incorrect sequence of

changing this value may result in incorrect operation of the device.

31:2 - 0 Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA

Loading...

Loading...