UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 19 of 841

NXP Semiconductors

UM10360

Chapter 3: LPC176x/5x System control

3.3 Register description

All registers, regardless of size, are on word address boundaries. Details of the registers

appear in the description of each function.

3.4 Reset

Reset has 4 sources on the LPC176x/5x: the RESET pin, Watchdog Reset, Power On

Reset (POR), and Brown Out Detect (BOD).

The RESET

pin is a Schmitt trigger input pin. Assertion of chip Reset by any source, once

the operating voltage attains a usable level, starts the wake-up timer (see description in

Section 4.9 “

Wake-up timer” in this chapter), causing reset to remain asserted until the

external Reset is de-asserted, the oscillator is running, a fixed number of clocks have

passed, and the flash controller has completed its initialization. The reset logic is shown in

the following block diagram (see Figure 4

).

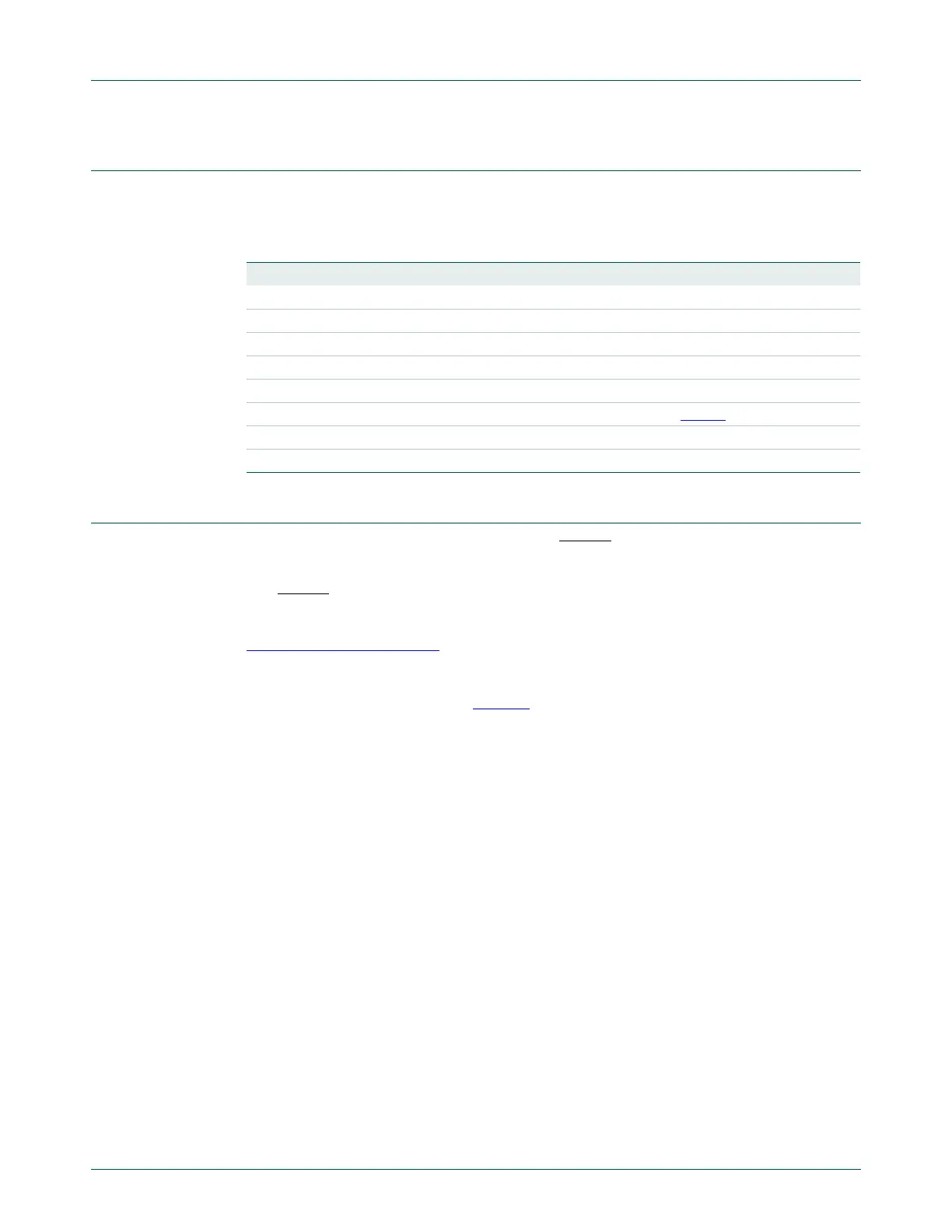

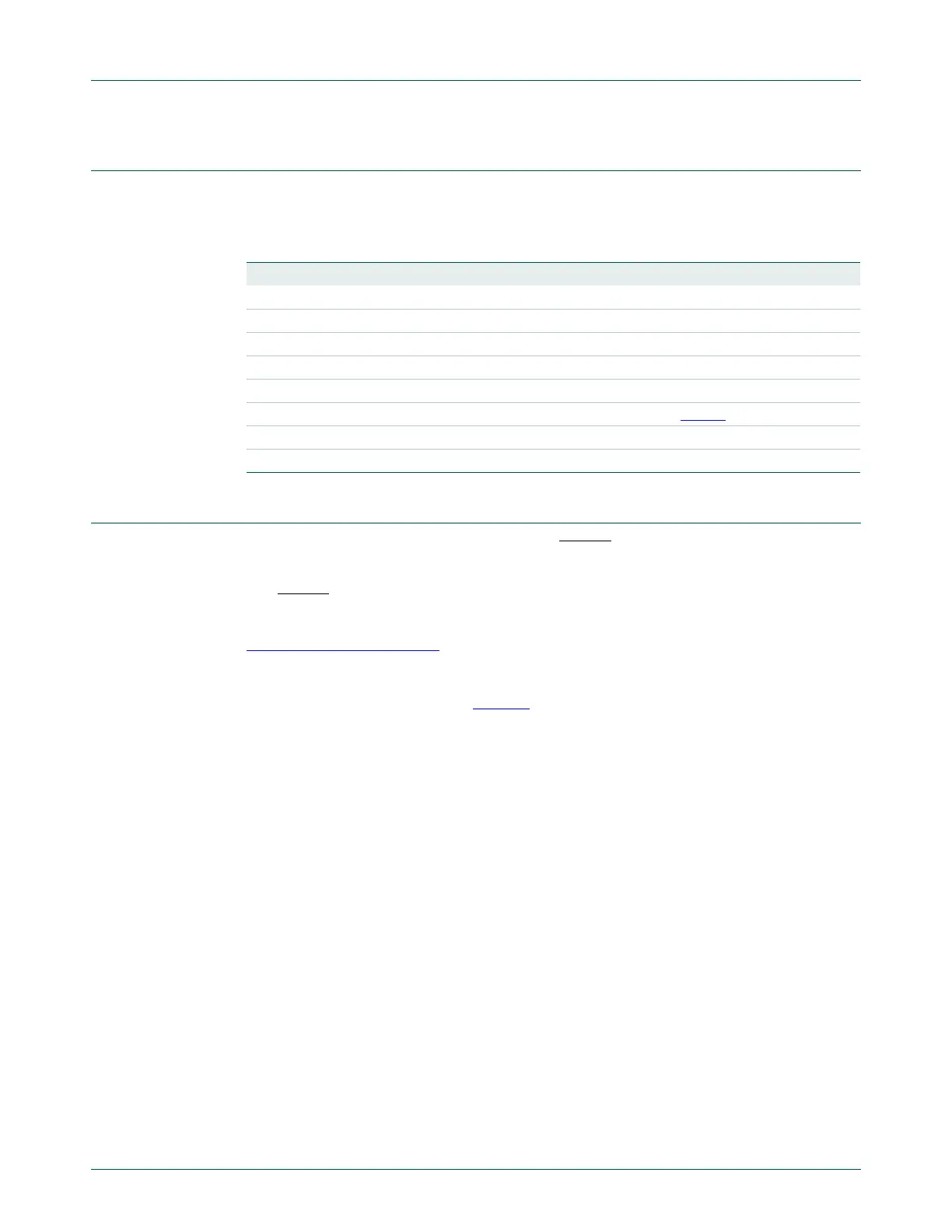

Table 7. Summary of system control registers

Name Description Access Reset value Address

External Interrupts

EXTINT External Interrupt Flag Register R/W 0 0x400F C140

EXTMODE External Interrupt Mode register R/W 0 0x400F C148

EXTPOLAR External Interrupt Polarity Register R/W 0 0x400F C14C

Reset

RSID Reset Source Identification Register R/W see Table 8 0x400F C180

Syscon Miscellaneous Registers

SCS System Control and Status R/W 0 0x400F C1A0

Loading...

Loading...