UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 409 of 841

NXP Semiconductors

UM10360

Chapter 17: LPC176x/5x SPI

17.7.2 SPI Status Register (S0SPSR - 0x4002 0004)

The S0SPSR register controls the operation of SPI0 as per the configuration bits setting

shown in Table 362

.

17.7.3 SPI Data Register (S0SPDR - 0x4002 0008)

This bi-directional data register provides the transmit and receive data for the SPI.

Transmit data is provided to the SPI by writing to this register. Data received by the SPI

can be read from this register. When used as a master, a write to this register will start an

SPI data transfer. Writes to this register will be blocked when a data transfer starts, or

when the SPIF status bit is set, and the SPI Status Register has not been read.

17.7.4 SPI Clock Counter Register (S0SPCCR - 0x4002 000C)

This register controls the frequency of a master’s SCK. The register indicates the number

of SPI peripheral clock cycles that make up an SPI clock.

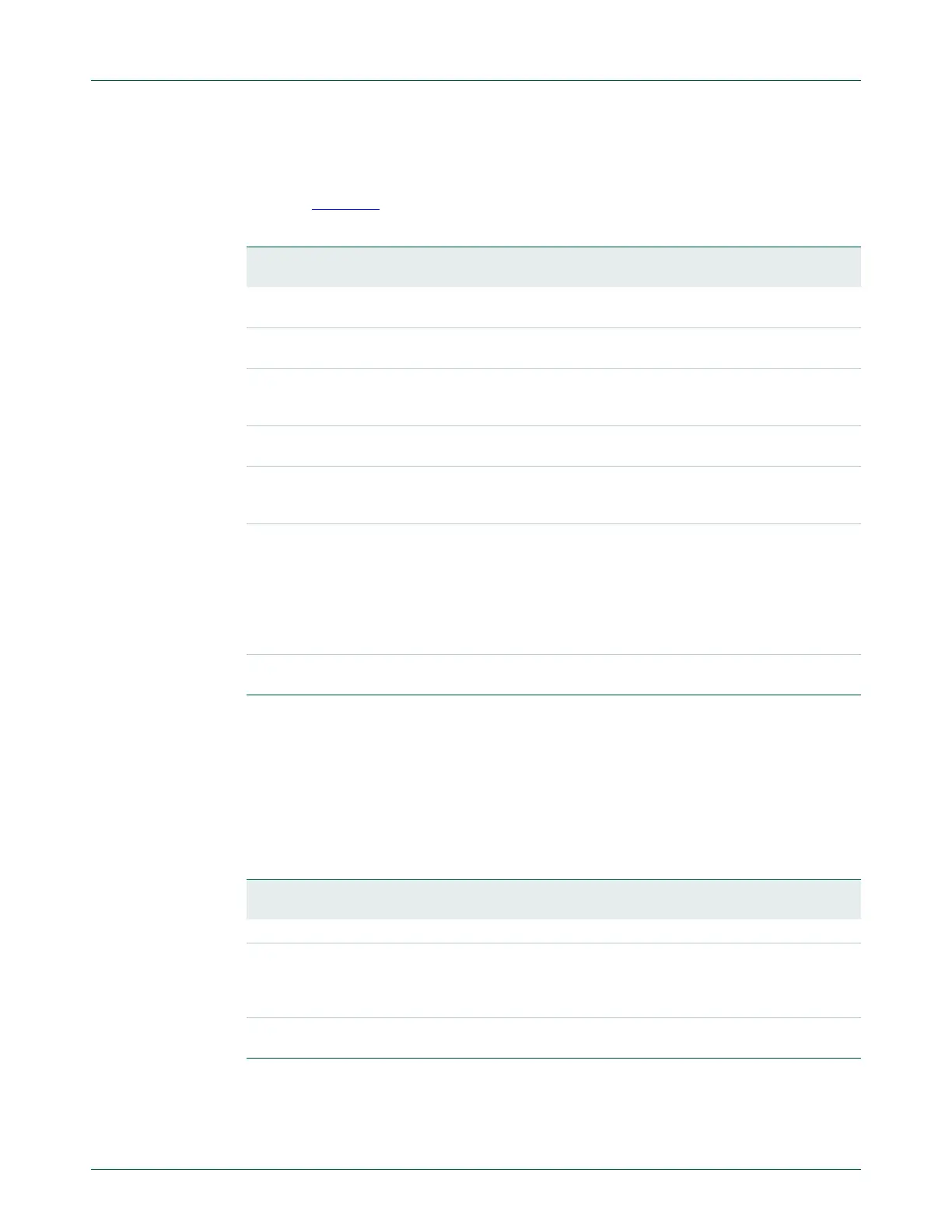

Table 362: SPI Status Register (S0SPSR - address 0x4002 0004) bit description

Bit Symbol Description Reset

Value

2:0 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

3 ABRT Slave abort. When 1, this bit indicates that a slave abort has occurred.

This bit is cleared by reading this register.

0

4 MODF Mode fault. when 1, this bit indicates that a Mode fault error has

occurred. This bit is cleared by reading this register, then writing the

SPI0 control register.

0

5 ROVR Read overrun. When 1, this bit indicates that a read overrun has

occurred. This bit is cleared by reading this register.

0

6 WCOL Write collision. When 1, this bit indicates that a write collision has

occurred. This bit is cleared by reading this register, then accessing the

SPI Data Register.

0

7 SPIF SPI transfer complete flag. When 1, this bit indicates when a SPI data

transfer is complete. When a master, this bit is set at the end of the last

cycle of the transfer. When a slave, this bit is set on the last data

sampling edge of the SCK. This bit is cleared by first reading this

register, then accessing the SPI Data Register.

Note: this is not the SPI interrupt flag. This flag is found in the SPINT

register.

0

31:8 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

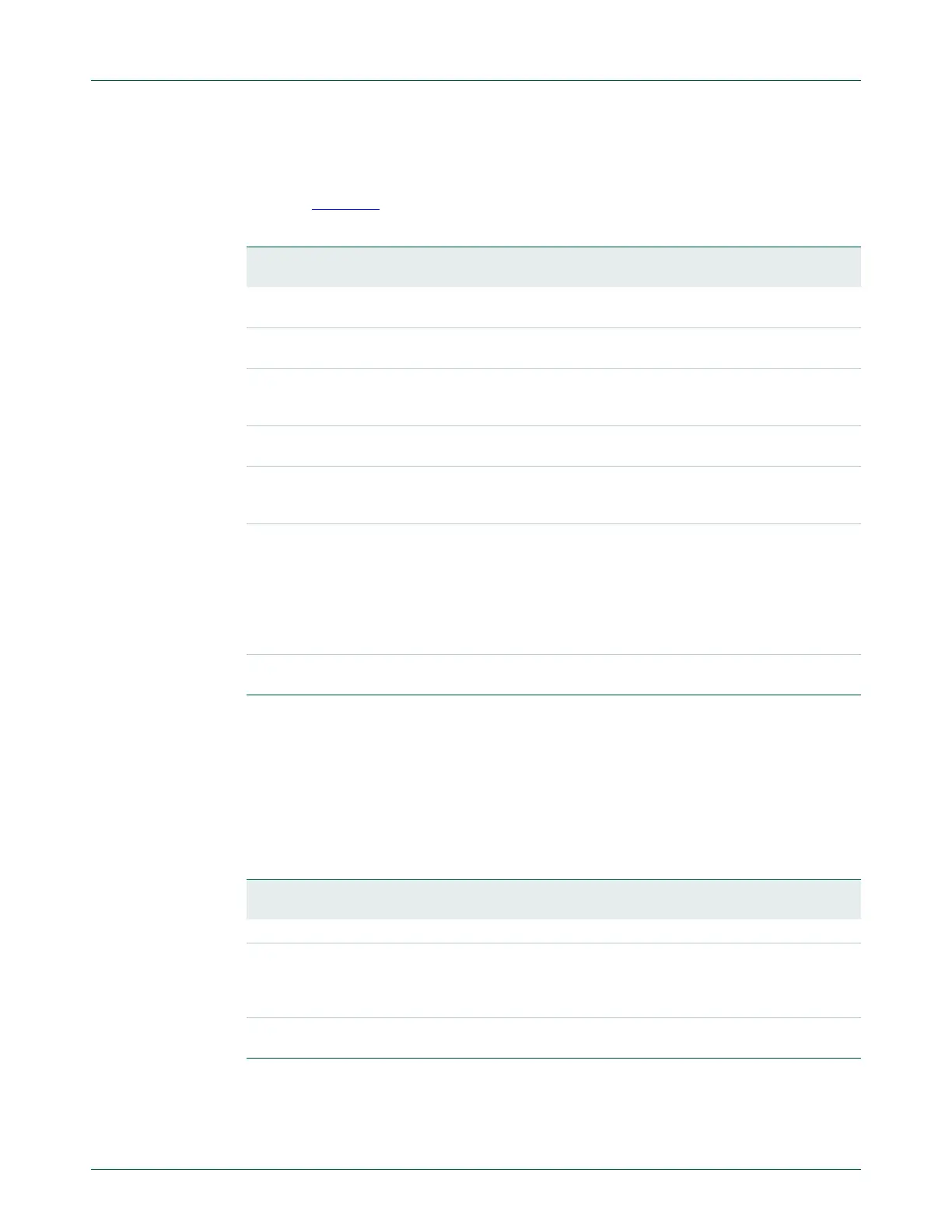

Table 363: SPI Data Register (S0SPDR - address 0x4002 0008) bit description

Bit Symbol Description Reset

Value

7:0 DataLow SPI Bi-directional data port. 0x00

15:8 DataHigh If bit 2 of the SPCR is 1 and bits 11:8 are other than 1000, some or all

of these bits contain the additional transmit and receive bits. When less

than 16 bits are selected, the more significant among these bits read

as zeroes.

0x00

31:16 - Reserved, user software should not write ones to reserved bits. The

value read from a reserved bit is not defined.

NA

Loading...

Loading...