UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 408 of 841

NXP Semiconductors

UM10360

Chapter 17: LPC176x/5x SPI

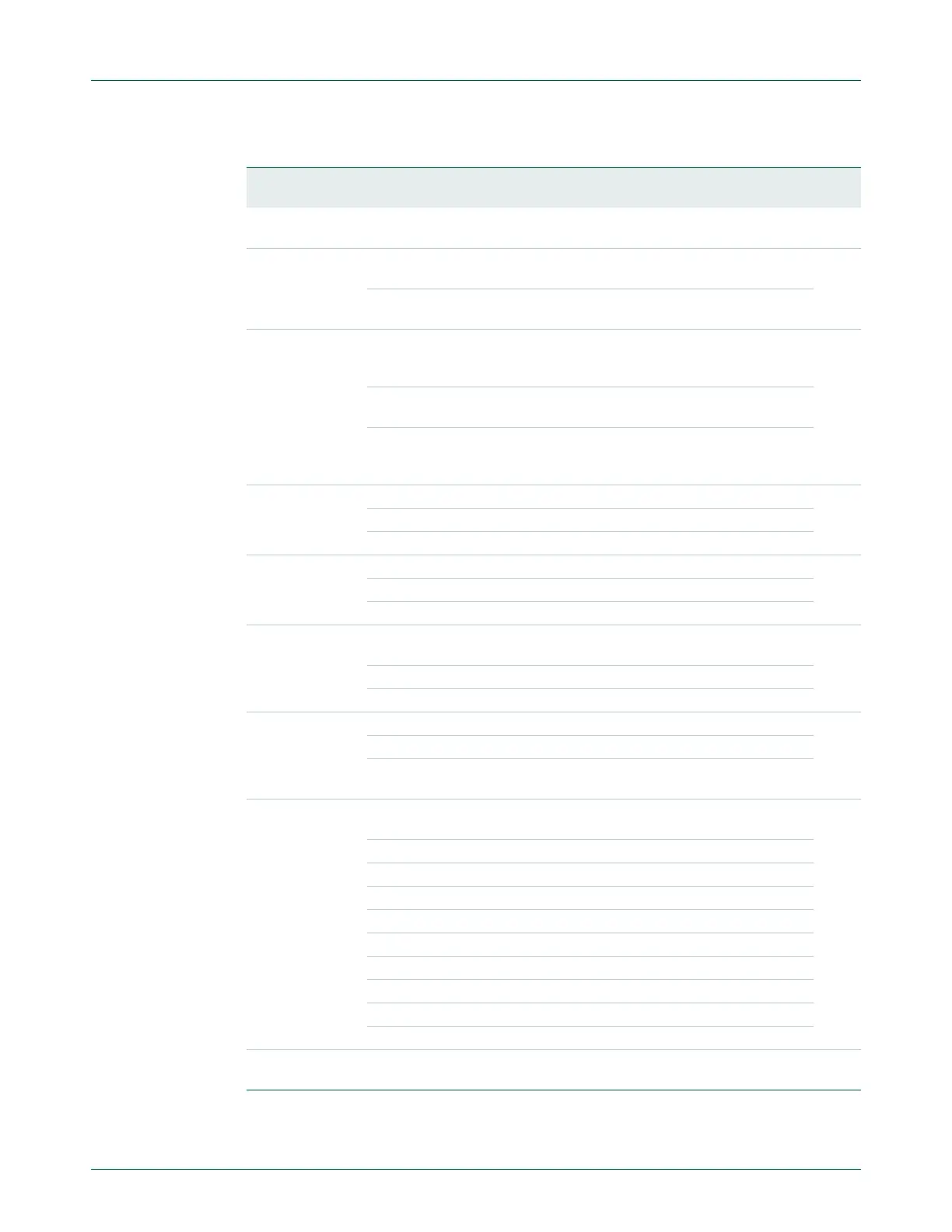

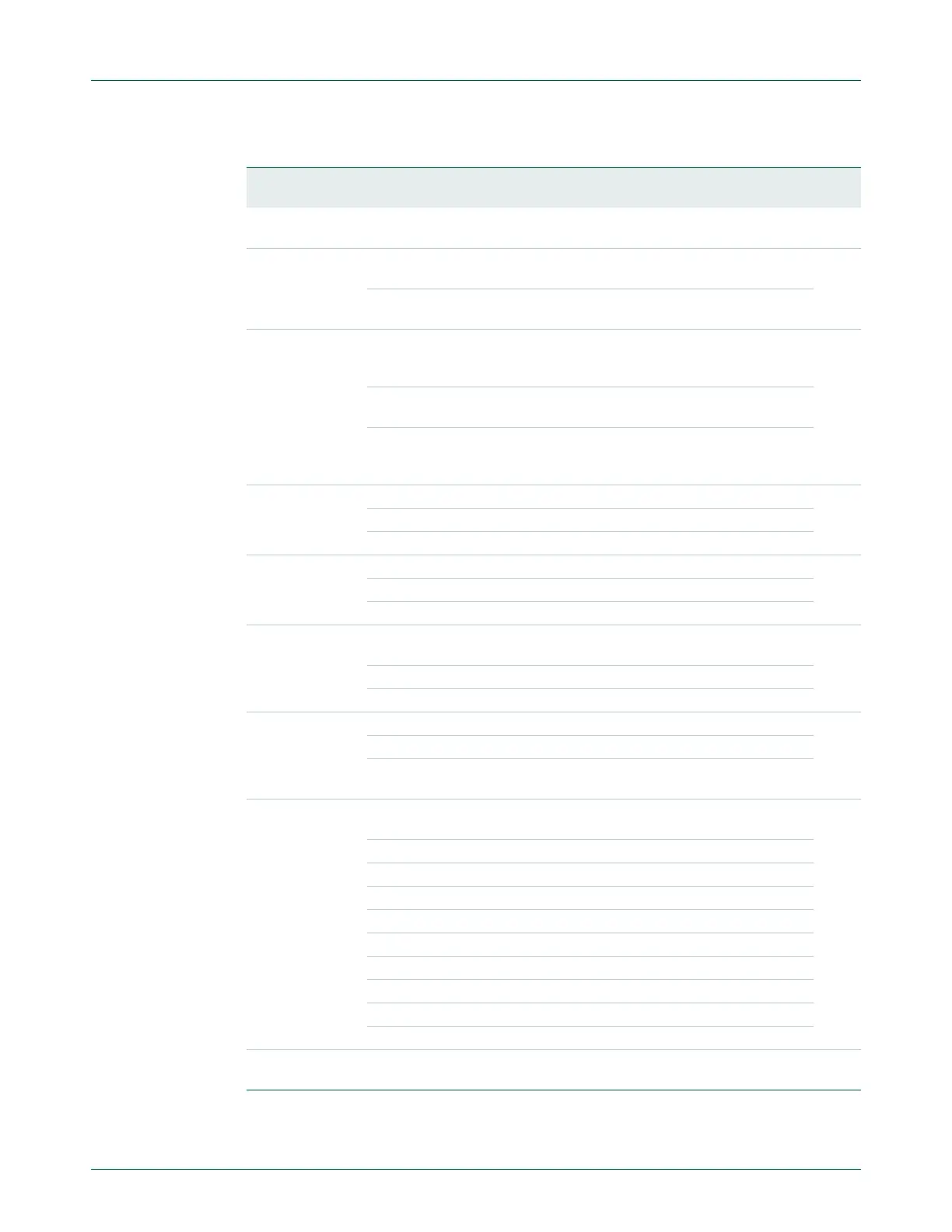

Table 361: SPI Control Register (S0SPCR - address 0x4002 0000) bit description

Bit Symbol Value Description Reset

Value

1:0 - Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA

2 BitEnable 0 The SPI controller sends and receives 8 bits of data per

transfer.

0

1 The SPI controller sends and receives the number of bits

selected by bits 11:8.

3 CPHA Clock phase control determines the relationship between the

data and the clock on SPI transfers, and controls when a slave

transfer is defined as starting and ending.

0

0 Data is sampled on the first clock edge of SCK. A transfer starts

and ends with activation and deactivation of the SSEL signal.

1 Data is sampled on the second clock edge of the SCK. A

transfer starts with the first clock edge, and ends with the last

sampling edge when the SSEL signal is active.

4 CPOL Clock polarity control. 0

0 SCK is active high.

1 SCK is active low.

5 MSTR Master mode select. 0

0 The SPI operates in Slave mode.

1 The SPI operates in Master mode.

6 LSBF LSB First controls which direction each byte is shifted when

transferred.

0

0 SPI data is transferred MSB (bit 7) first.

1 SPI data is transferred LSB (bit 0) first.

7 SPIE Serial peripheral interrupt enable. 0

0 SPI interrupts are inhibited.

1 A hardware interrupt is generated each time the SPIF or MODF

bits are activated.

11:8 BITS When bit 2 of this register is 1, this field controls the number of

bits per transfer:

0000

1000 8 bits per transfer

1001 9 bits per transfer

1010 10 bits per transfer

1011 11 bits per transfer

1100 12 bits per transfer

1101 13 bits per transfer

1110 14 bits per transfer

1111 15 bits per transfer

0000 16 bits per transfer

31:12 - Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA

Loading...

Loading...