UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 564 of 841

NXP Semiconductors

UM10360

Chapter 27: LPC176x/5x Real-Time Clock (RTC) and backup registers

27.6.2.3 Counter Increment Interrupt Register (CIIR - 0x4002 400C)

The Counter Increment Interrupt Register (CIIR) gives the ability to generate an interrupt

every time a counter is incremented. This interrupt remains valid until cleared by writing a

1 to bit 0 of the Interrupt Location Register (ILR[0]).

27.6.2.4 Alarm Mask Register (AMR - 0x4002 4010)

The Alarm Mask Register (AMR) allows the user to mask any of the alarm registers.

Table 511

shows the relationship between the bits in the AMR and the alarms. For the

alarm function, every non-masked alarm register must match the corresponding time

counter for an interrupt to be generated. The interrupt is generated only when the counter

comparison first changes from no match to match. The interrupt is removed when a one is

written to the appropriate bit of the Interrupt Location Register (ILR). If all mask bits are

set, then the alarm is disabled.

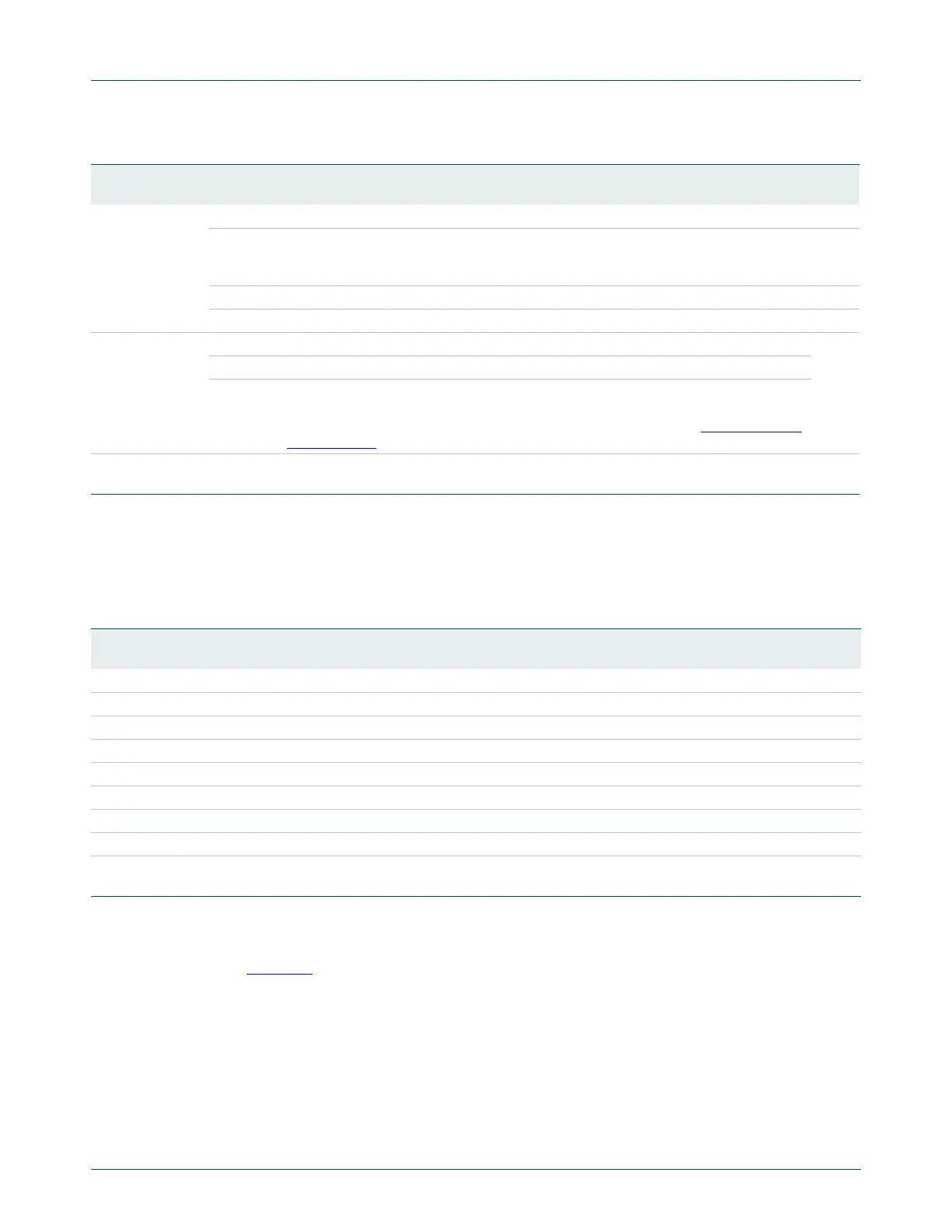

1 CTCRST CTC Reset. 0

1 When one, the elements in the internal oscillator divider are reset, and remain reset until

CCR[1] is changed to zero. This is the divider that generates the 1 Hz clock from the

32.768 kHz crystal. The state of the divider is not visible to software.

0No effect.

3:2 - Internal test mode controls. These bits must be 0 for normal RTC operation. NC

4 CCALEN Calibration counter enable. NC

1 The calibration counter is disabled and reset to zero.

0 The calibration counter is enabled and counting, using the 1 Hz clock. When the

calibration counter is equal to the value of the CALIBRATION register, the counter resets

and repeats counting up to the value of the CALIBRATION register. See Section 27.6.4.2

and Section 27.6.5

.

31:5 - Reserved, user software should not write ones to reserved bits. The value read from a

reserved bit is not defined.

NA

Table 509. Clock Control Register (CCR - address 0x4002 4008) bit description

…continued

Bit Symbol Value Description Reset

value

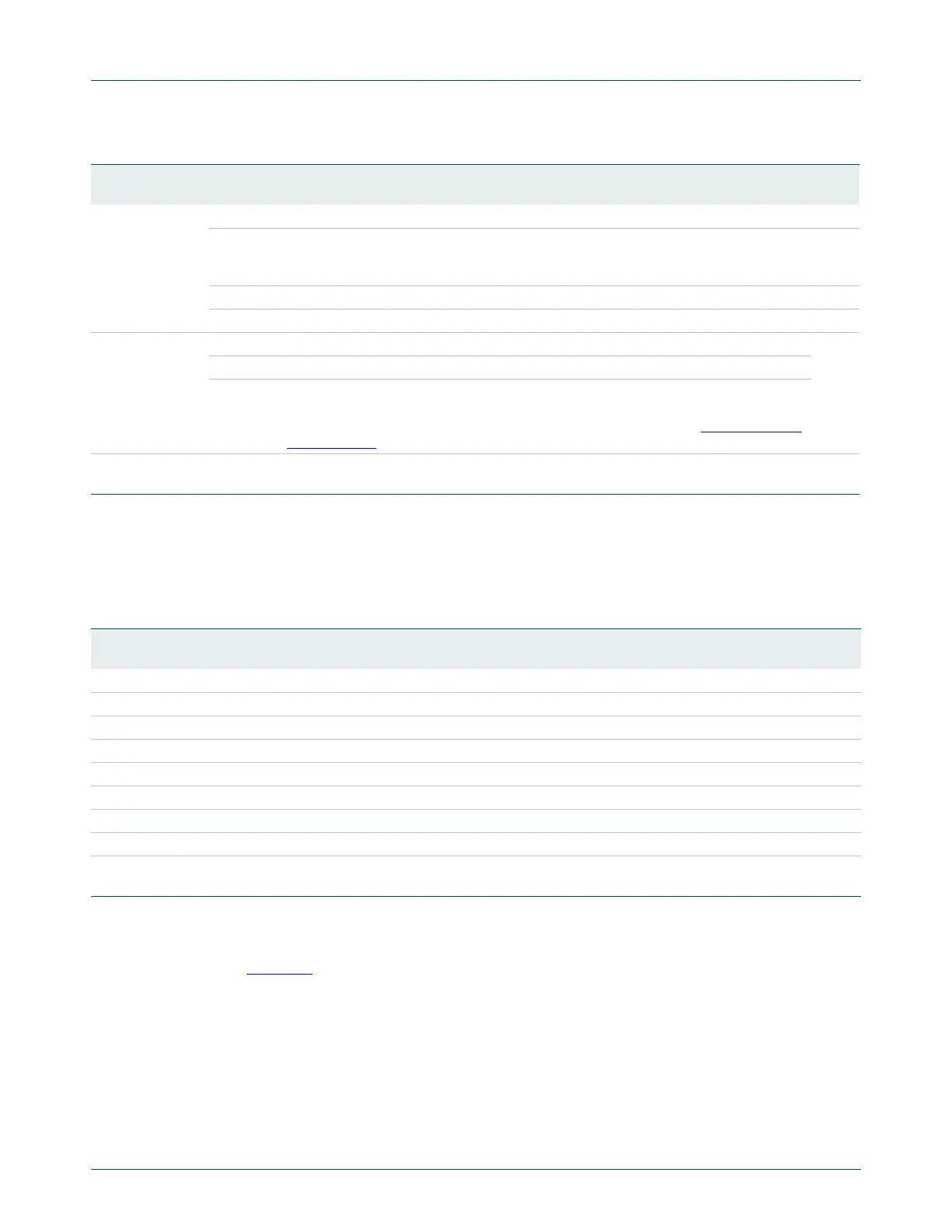

Table 510. Counter Increment Interrupt Register (CIIR - address 0x4002 400C) bit description

Bit Symbol Description Reset

value

0 IMSEC When 1, an increment of the Second value generates an interrupt. 0

1 IMMIN When 1, an increment of the Minute value generates an interrupt. 0

2 IMHOUR When 1, an increment of the Hour value generates an interrupt. 0

3 IMDOM When 1, an increment of the Day of Month value generates an interrupt. 0

4 IMDOW When 1, an increment of the Day of Week value generates an interrupt. 0

5 IMDOY When 1, an increment of the Day of Year value generates an interrupt. 0

6 IMMON When 1, an increment of the Month value generates an interrupt. 0

7 IMYEAR When 1, an increment of the Year value generates an interrupt. 0

31:8 - Reserved, user software should not write ones to reserved bits. The value read from a reserved

bit is not defined.

NA

Loading...

Loading...