UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 421 of 841

NXP Semiconductors

UM10360

Chapter 18: LPC176x/5x SSP0/1

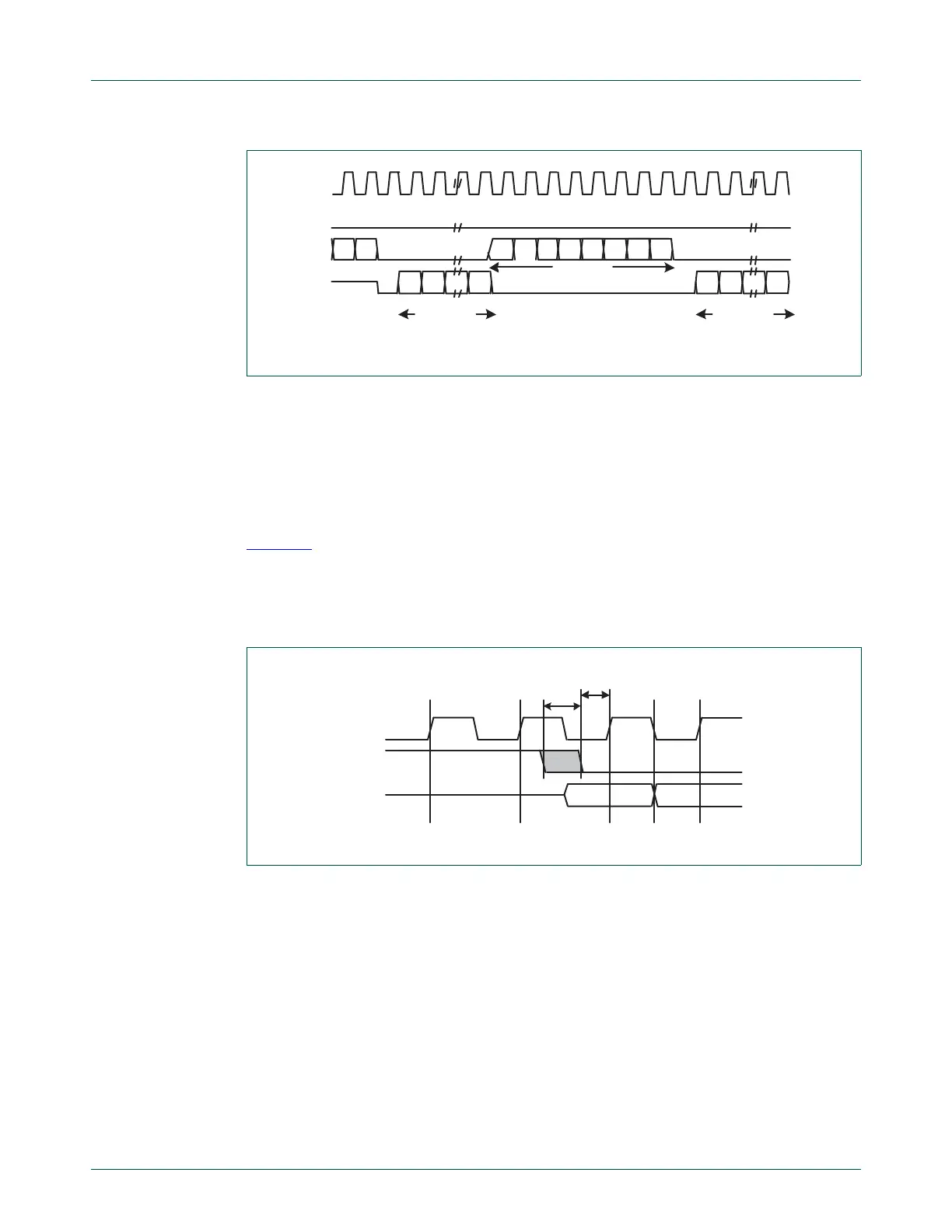

18.5.3.1 Setup and hold time requirements on CS with respect to SK in Microwire

mode

In the Microwire mode, the SSP slave samples the first bit of receive data on the rising

edge of SK after CS has gone LOW. Masters that drive a free-running SK must ensure

that the CS signal has sufficient setup and hold margins with respect to the rising edge of

SK.

Figure 83

illustrates these setup and hold time requirements. With respect to the SK rising

edge on which the first bit of receive data is to be sampled by the SSP slave, CS must

have a setup of at least two times the period of SK on which the SSP operates. With

respect to the SK rising edge previous to this edge, CS must have a hold of at least one

SK period.

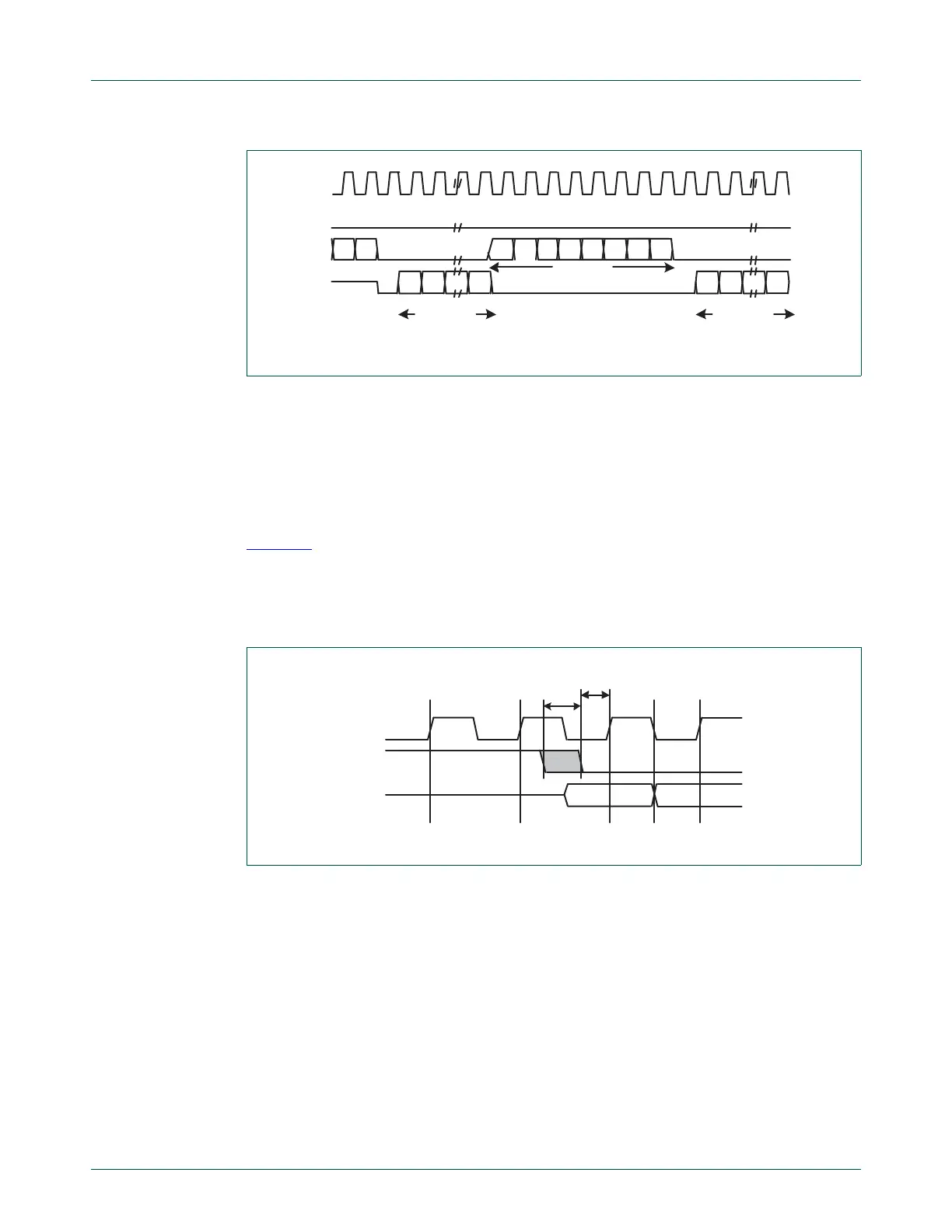

Fig 82. Microwire frame format (continuos transfers)

SK

CS

SO

SI

MSB LSB

4 to 16 bits

output data

8-bit control

4 to 16 bits

output data

MSB LSB

0

MSB LSB

LSB

Fig 83. Microwire frame format setup and hold details

SK

CS

SI

t

HOLD

= t

SK

t

SETUP

=2*t

SK

Loading...

Loading...