UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 353 of 841

NXP Semiconductors

UM10360

Chapter 16: LPC176x/5x CAN1/2

[1] During a Hardware reset or when the Bus Status bit is set '1' (Bus-Off), the Reset Mode bit is set '1' (present). After the Reset Mode bit

is set '0' the CAN Controller will wait for:

- one occurrence of Bus-Free signal (11 recessive bits), if the preceding reset has been caused by a Hardware reset or a CPU-initiated

reset.

- 128 occurrences of Bus-Free, if the preceding reset has been caused by a CAN Controller initiated Bus-Off, before re-entering the

Bus-On mode.

[2] This mode of operation forces the CAN Controller to be error passive. Message Transmission is not possible. The Listen Only Mode can

be used e.g. for software driven bit rate detection and "hot plugging".

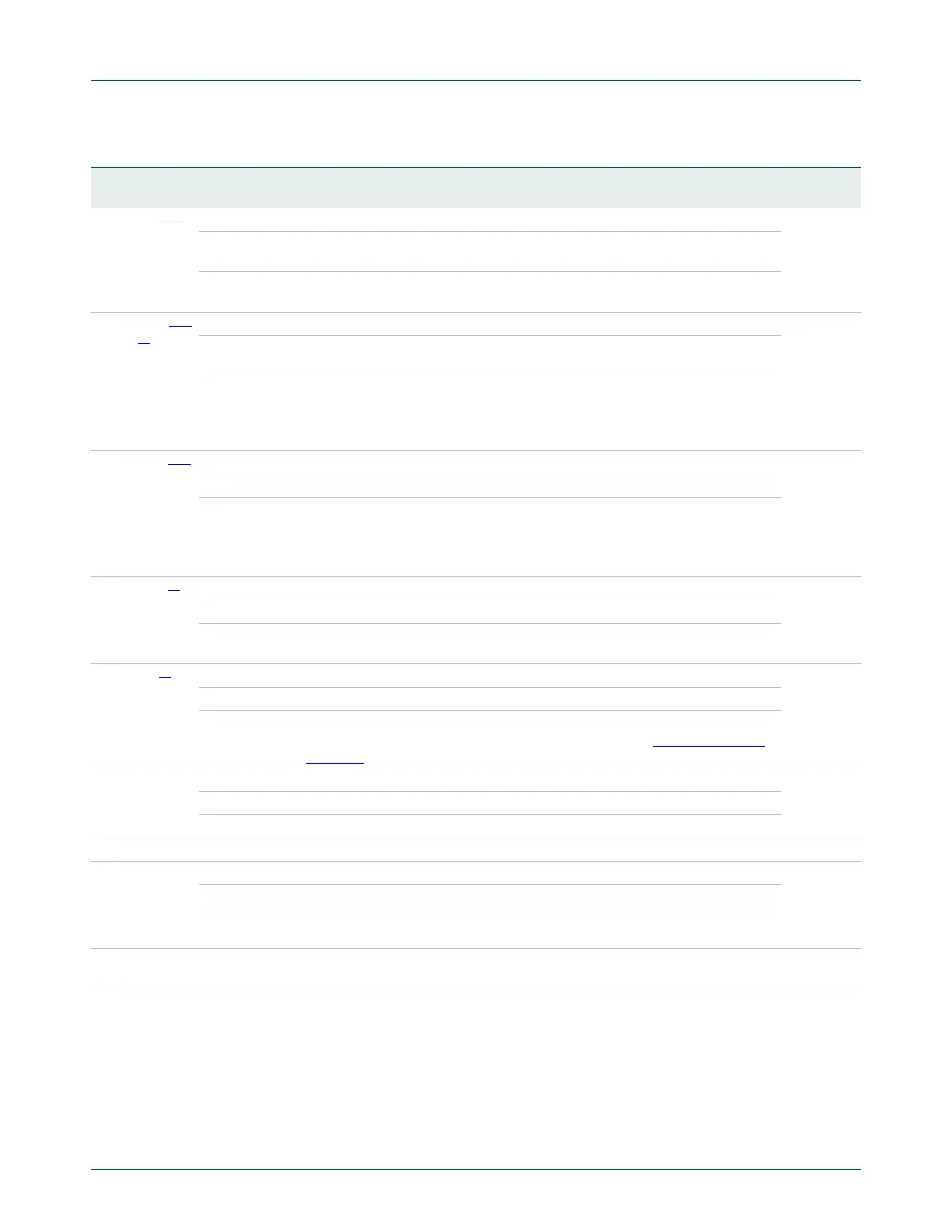

Table 317. CAN Mode register (CAN1MOD - address 0x4004 4000, CAN2MOD - address 0x4004 8000) bit description

Bit Symbol Value Function Reset

Value

RM

Set

0RM

[1][6]

Reset Mode. 1 1

0 (normal) The CAN Controller is in the Operating Mode, and certain registers can not

be written.

1 (reset) CAN operation is disabled, writable registers can be written and the current

transmission/reception of a message is aborted.

1LOM

[3][2]

[6]

Listen Only Mode. 0 x

0 (normal) The CAN controller acknowledges a successfully received message on the

CAN bus. The error counters are stopped at the current value.

1 (listen only) The controller gives no acknowledgment, even if a message is successfully

received. Messages cannot be sent, and the controller operates in “error

passive” mode. This mode is intended for software bit rate detection and

“hot plugging”.

2STM

[3][6]

Self Test Mode. 0 x

0 (normal) A transmitted message must be acknowledged to be considered successful.

1 (self test) The controller will consider a Tx message successful even if there is no

acknowledgment received.

In this mode a full node test is possible without any other active node on the

bus using the SRR bit in CANxCMR.

3TPM

[4]

Transmit Priority Mode. 0 x

0 (CAN ID) The transmit priority for 3 Transmit Buffers depends on the CAN Identifier.

1 (local prio) The transmit priority for 3 Transmit Buffers depends on the contents of the

Tx Priority register within the Transmit Buffer.

4SM

[5]

Sleep Mode. 0 0

0 (wake-up) Normal operation.

1 (sleep) The CAN controller enters Sleep Mode if no CAN interrupt is pending and

there is no bus activity. See the Sleep Mode description Section 16.8.2 on

page 371.

5 RPM Receive Polarity Mode. 0 x

0 (low active) RD input is active Low (dominant bit = 0).

1 (high active) RD input is active High (dominant bit = 1) -- reverse polarity.

6 - - Reserved, user software should not write ones to reserved bits. 0 0

7TM Test Mode. 0 x

0 (disabled) Normal operation.

1 (enabled) The TD pin will reflect the bit, detected on RD pin, with the next positive

edge of the system clock.

31:8 - Reserved, user software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

NA

Loading...

Loading...