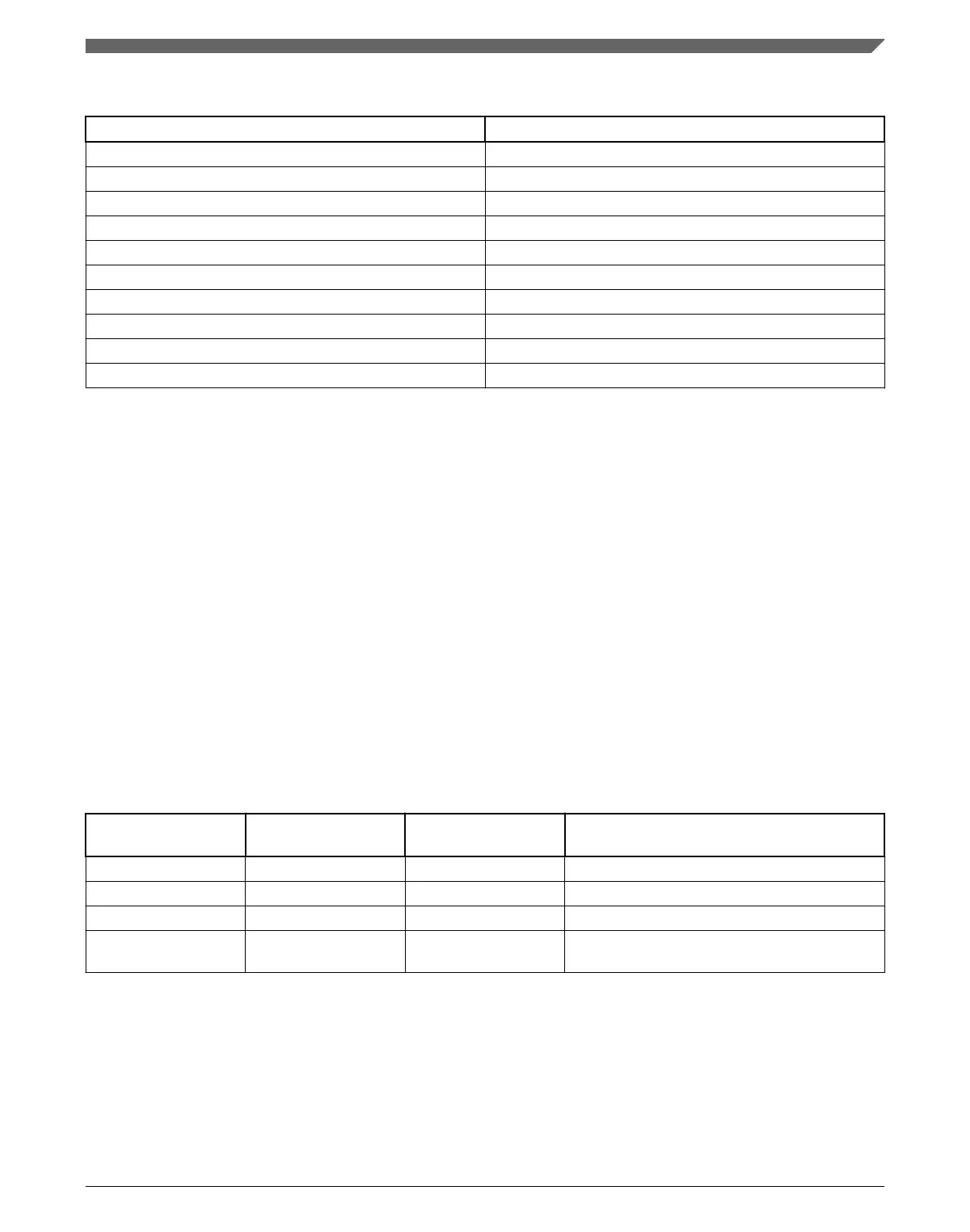

Table 3-43. ADC Alternate trigger options (continued)

SIM_SOPT7[ADCxTRGSEL] Selected source

0110 PIT trigger 2

0111 PIT trigger 3

1000 FTM0 trigger

1001 FTM1 trigger

1010 FTM2 trigger

1011 FTM3 trigger

1100 RTC alarm

1101 RTC seconds

1110 LPTMR trigger

1111 Reserved

For operation of triggers in different modes, refer to Power Management chapter.

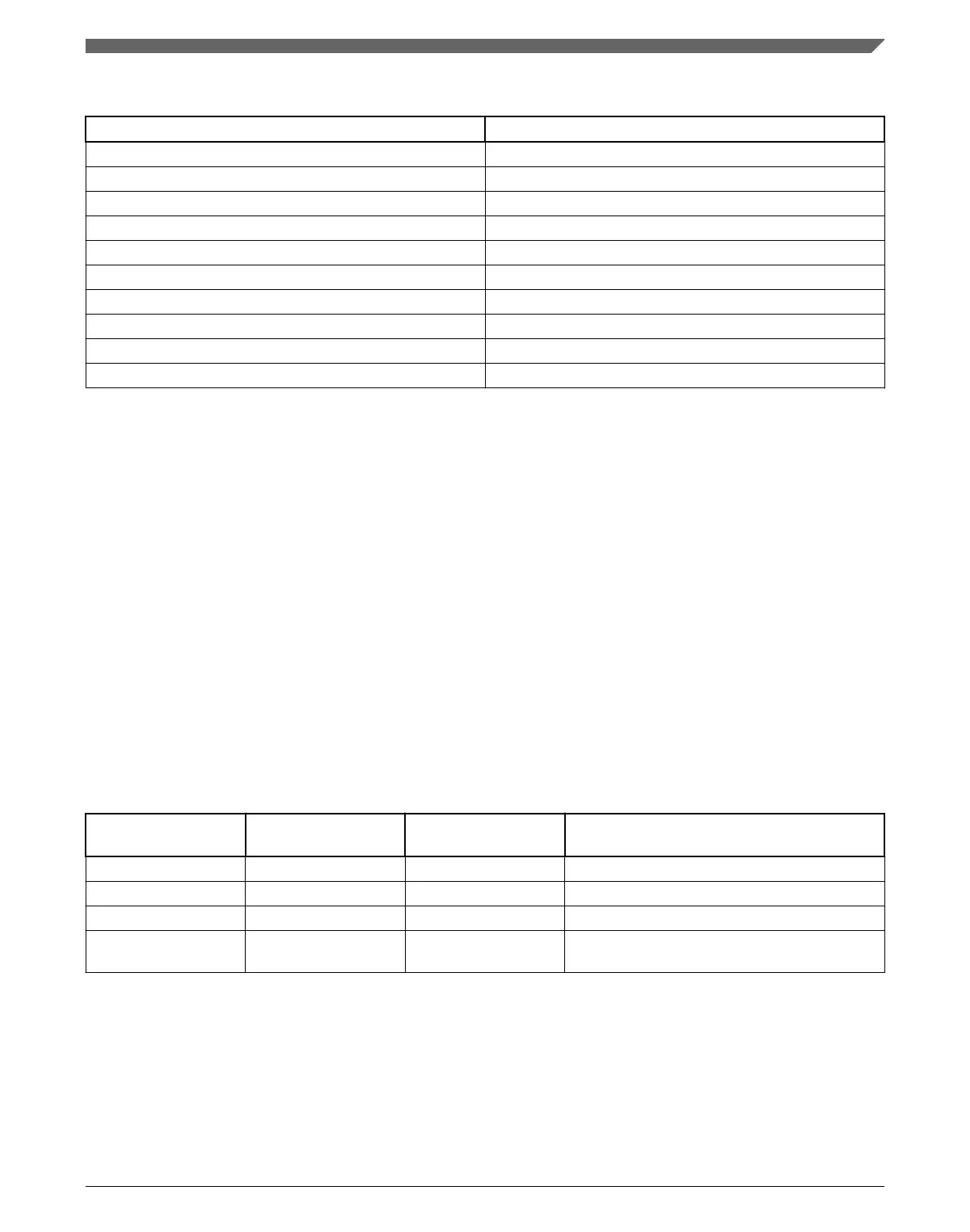

3.7.1.9 ADC conversion clock options

The ADC has multiple input clock sources. Selection is determined by

ADCx_CFG1[ADICLK] bitfield. The following table shows the chip-specific clock

assignments for this bitfield.

NOTE

The ALTCLK option is only usable when OSCERCLK is in the

MHz range. A system with OSCERCLK in the kHz range has

the optional clock source below minimum ADC clock operating

frequency.

Table 3-44. ADC Conversion Clock Options

ADCx_CFG1[ADICLK] ADC defined

selection

Chip clock Note

00 Bus Clock Bus Clock

01 ALTCLK2 IRC48MCLK Note

1

10 ALTCLK OSCERCLK Note

1

11 Asynchronous clock

(ADACK)

N/A - sourced from

within ADC block

Note

1

1. For ADC operation in Compute only, PSTOP1, Stop and VLPS, ADACK and the alternate clock sources are allowed clock

sources. Note however that ALTCLK2 is force disabled and therefore not available in VLPS.

Chapter 3 Chip Configuration

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 103

Loading...

Loading...