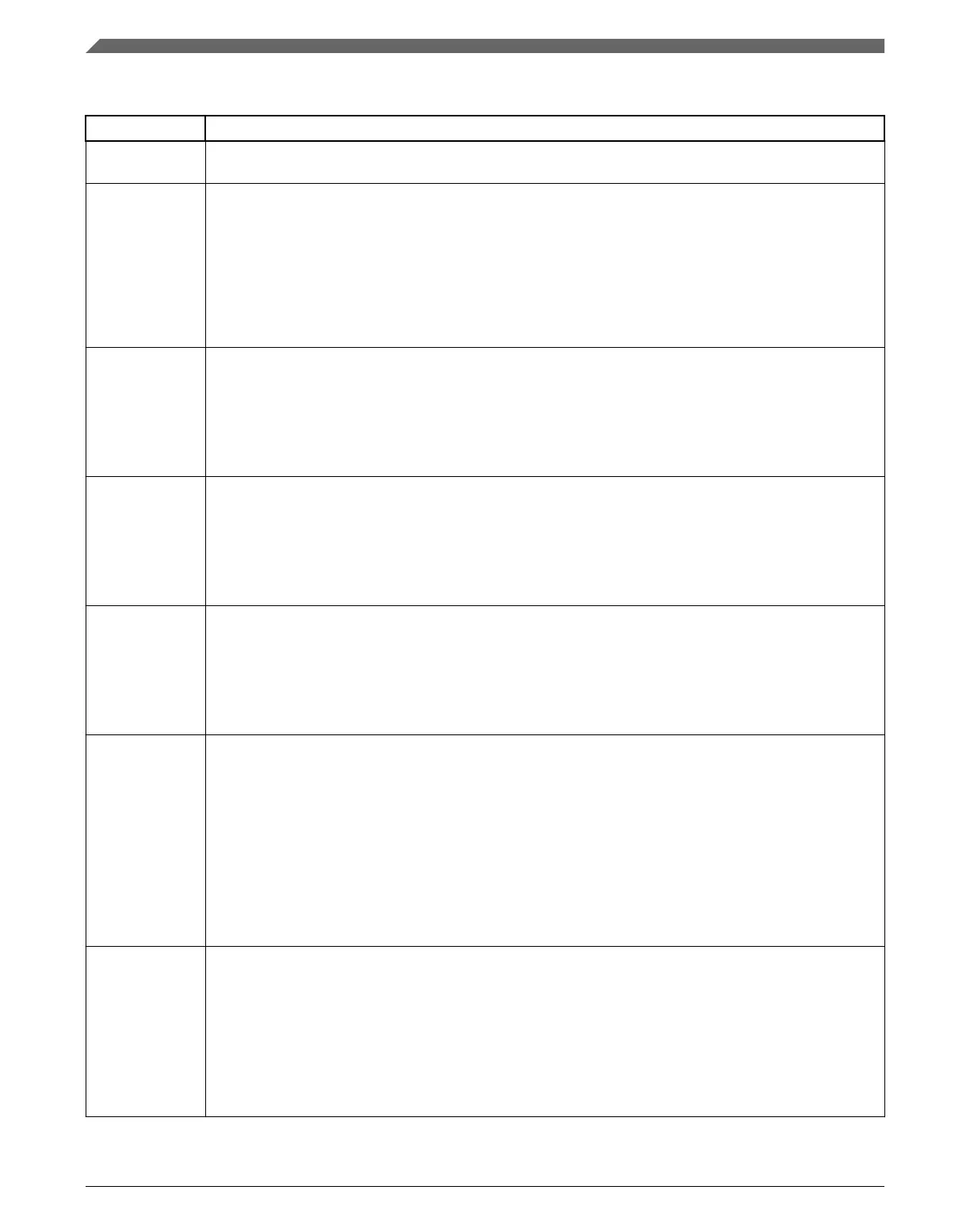

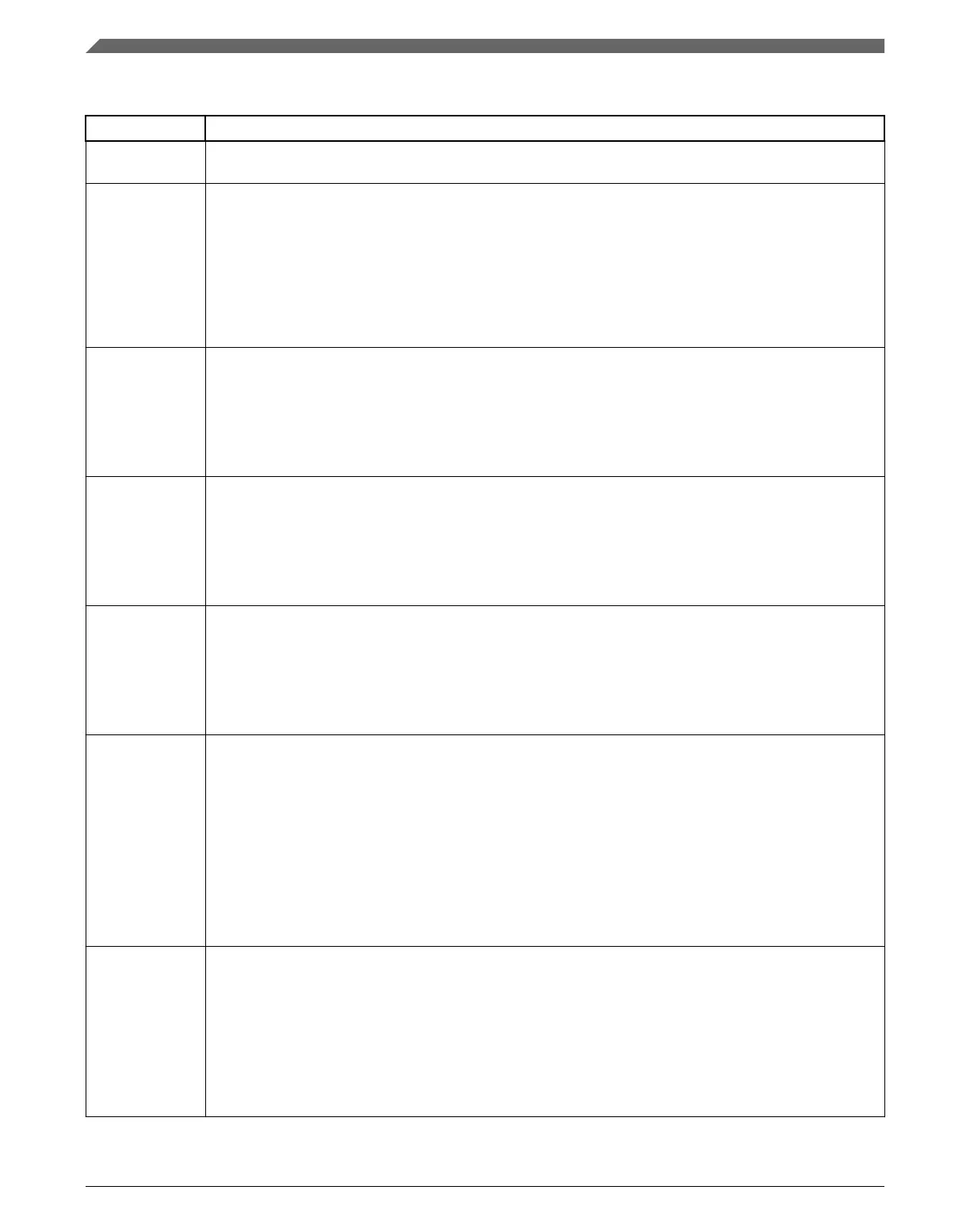

SPIx_MCR field descriptions (continued)

Field Description

0 Doze mode has no effect on the module.

1 Doze mode disables the module.

14

MDIS

Module Disable

Allows the clock to be stopped to the non-memory mapped logic in the module effectively putting it in a

software-controlled power-saving state. The reset value of the MDIS bit is parameterized, with a default

reset value of 1. When the module is used in Slave Mode, it is recommended to leave this bit 0, because a

slave doesn't have control over master transactions.

0 Enables the module clocks.

1 Allows external logic to disable the module clocks.

13

DIS_TXF

Disable Transmit FIFO

When the TX FIFO is disabled, the transmit part of the module operates as a simplified double-buffered

SPI. This bit can be written only when the MDIS bit is cleared.

0 TX FIFO is enabled.

1 TX FIFO is disabled.

12

DIS_RXF

Disable Receive FIFO

When the RX FIFO is disabled, the receive part of the module operates as a simplified double-buffered

SPI. This bit can only be written when the MDIS bit is cleared.

0 RX FIFO is enabled.

1 RX FIFO is disabled.

11

CLR_TXF

Clear TX FIFO

Flushes the TX FIFO. Writing a 1 to CLR_TXF clears the TX FIFO Counter. The CLR_TXF bit is always

read as zero.

0 Do not clear the TX FIFO counter.

1 Clear the TX FIFO counter.

10

CLR_RXF

CLR_RXF

Flushes the RX FIFO. Writing a 1 to CLR_RXF clears the RX Counter. The CLR_RXF bit is always read

as zero.

NOTE:

After every RX FIFO clear operation (MCR [CLR_RXF] = 0b1) following a RX FIFO overflow (SR

[RFOF] = 0b1) scenario, immediately perform a single POP from the RX FIFO and discard the

read data. The POP and discard operation should be completed before the reception of new

incoming frame.

0 Do not clear the RX FIFO counter.

1 Clear the RX FIFO counter.

9–8

SMPL_PT

Sample Point

Controls when the module master samples SIN in Modified Transfer Format. This field is valid only when

CPHA bit in CTARn[CPHA] is 0.

00 0 protocol clock cycles between SCK edge and SIN sample

01 1 protocol clock cycle between SCK edge and SIN sample

10 2 protocol clock cycles between SCK edge and SIN sample

11 Reserved

Table continues on the next page...

Memory Map/Register Definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1134 NXP Semiconductors

Loading...

Loading...