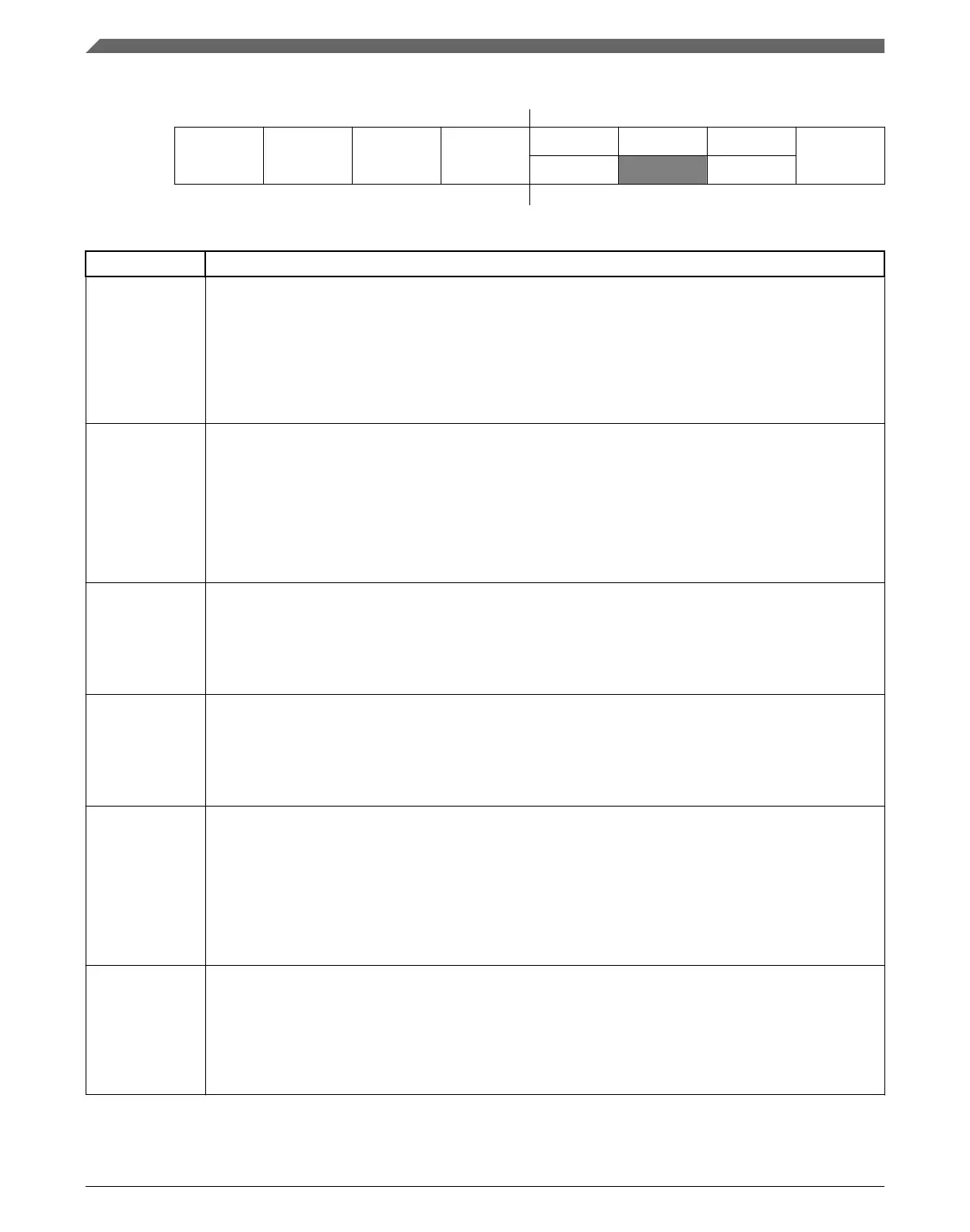

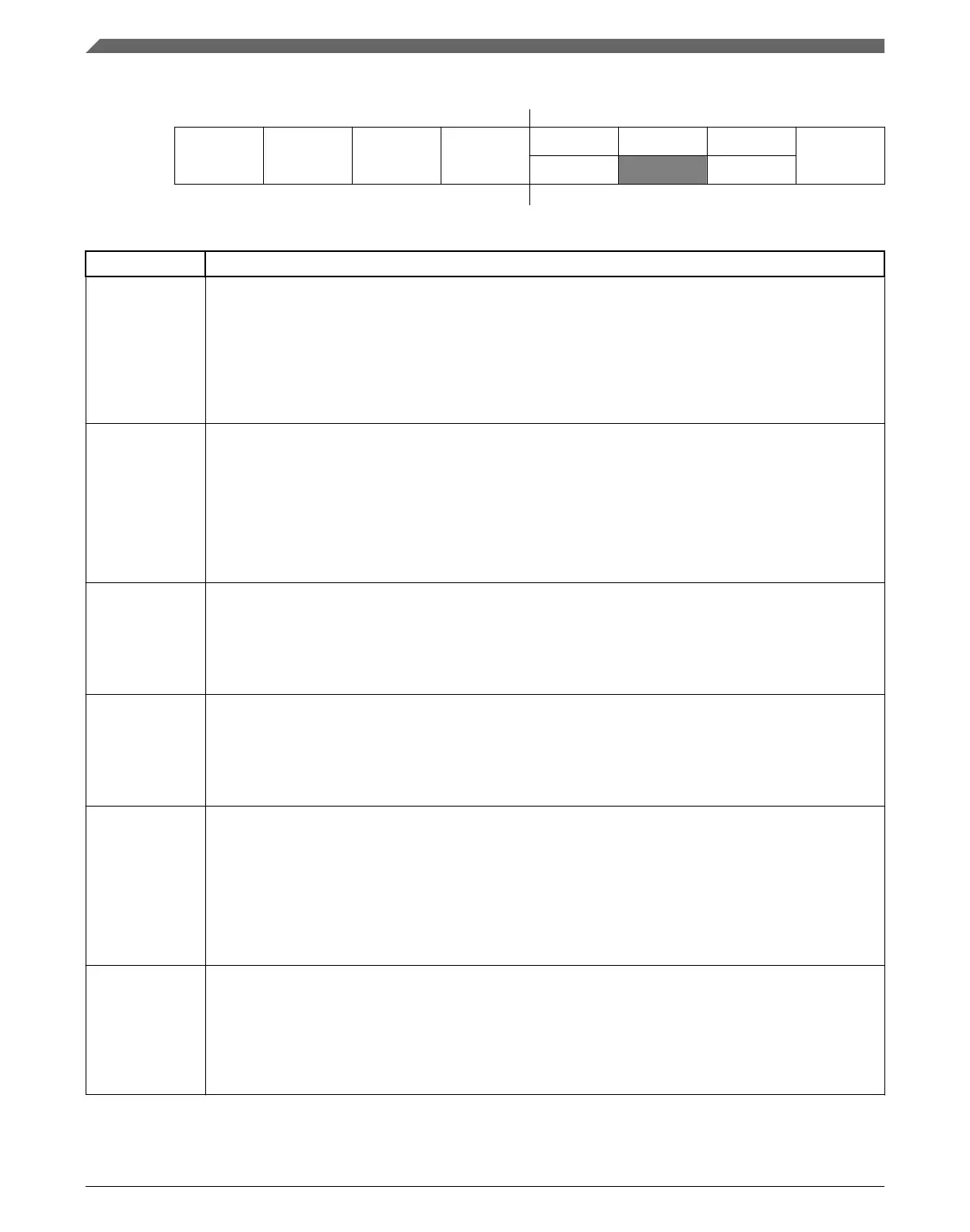

Address: Base address + 8h offset

Bit 7 6 5 4 3 2 1 0

Read

FACK ALERTEN SIICAEN TCKSEL

SLTF SHTF1 SHTF2

SHTF2IE

Write w1c w1c

Reset

0 0 0 0 0 0 0 0

I2Cx_SMB field descriptions

Field Description

7

FACK

Fast NACK/ACK Enable

For SMBus packet error checking, the CPU must be able to issue an ACK or NACK according to the result

of receiving data byte.

0 An ACK or NACK is sent on the following receiving data byte

1 Writing 0 to TXAK after receiving a data byte generates an ACK. Writing 1 to TXAK after receiving a

data byte generates a NACK.

6

ALERTEN

SMBus Alert Response Address Enable

Enables or disables SMBus alert response address matching.

NOTE:

After the host responds to a device that used the alert response address, you must use software

to put the device's address on the bus. The alert protocol is described in the SMBus specification.

0 SMBus alert response address matching is disabled

1 SMBus alert response address matching is enabled

5

SIICAEN

Second I2C Address Enable

Enables or disables SMBus device default address.

0 I2C address register 2 matching is disabled

1 I2C address register 2 matching is enabled

4

TCKSEL

Timeout Counter Clock Select

Selects the clock source of the timeout counter.

0 Timeout counter counts at the frequency of the I2C module clock / 64

1 Timeout counter counts at the frequency of the I2C module clock

3

SLTF

SCL Low Timeout Flag

This bit is set when the SLT register (consisting of the SLTH and SLTL registers) is loaded with a non-zero

value (LoValue) and an SCL low timeout occurs. Software clears this bit by writing a logic 1 to it.

NOTE:

The low timeout function is disabled when the SLT register's value is 0.

0 No low timeout occurs

1 Low timeout occurs

2

SHTF1

SCL High Timeout Flag 1

This read-only bit sets when SCL and SDA are held high more than clock × LoValue / 512, which indicates

the bus is free. This bit is cleared automatically.

0 No SCL high and SDA high timeout occurs

1 SCL high and SDA high timeout occurs

Table continues on the next page...

Memory map/register definition

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

1194 NXP Semiconductors

Loading...

Loading...