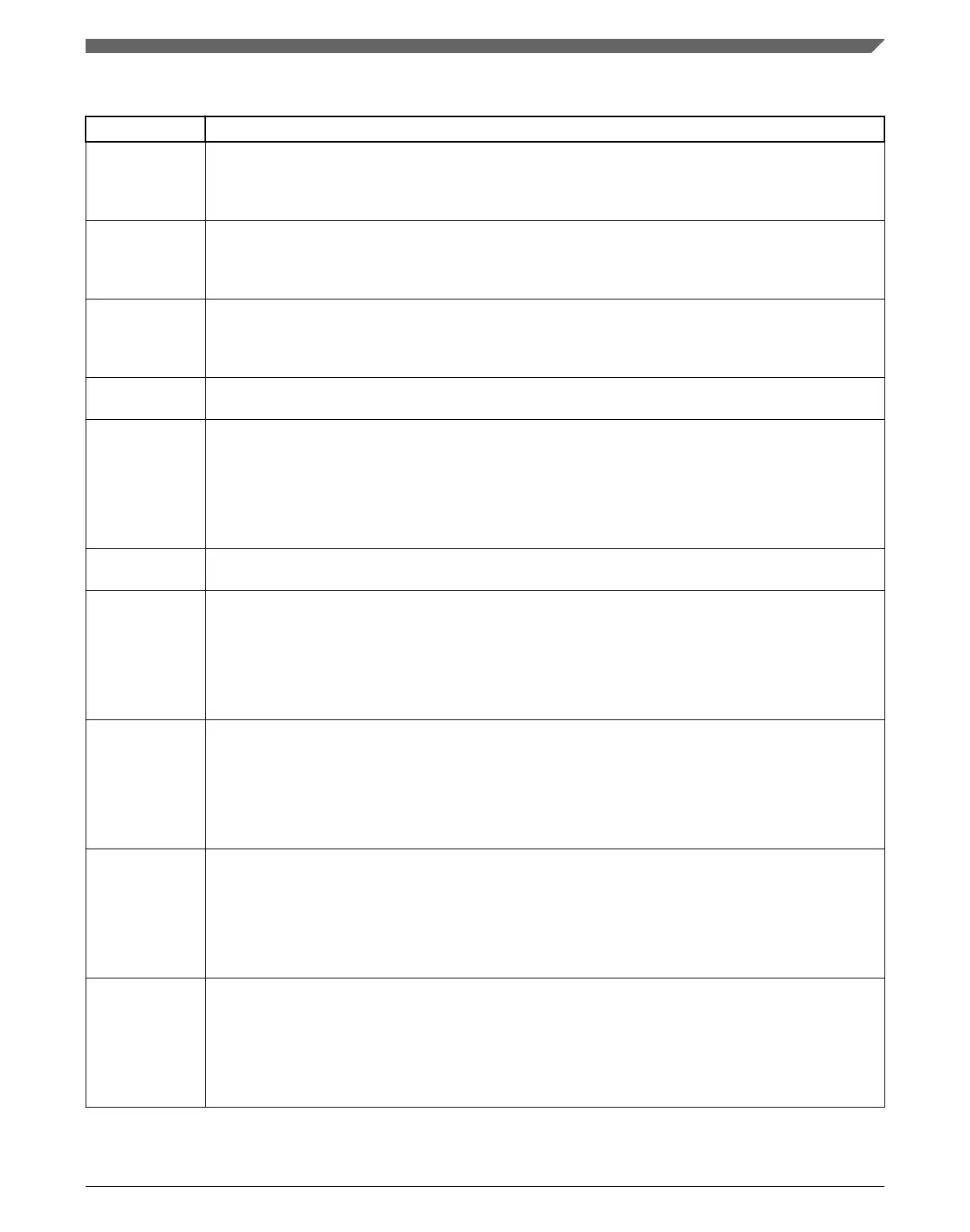

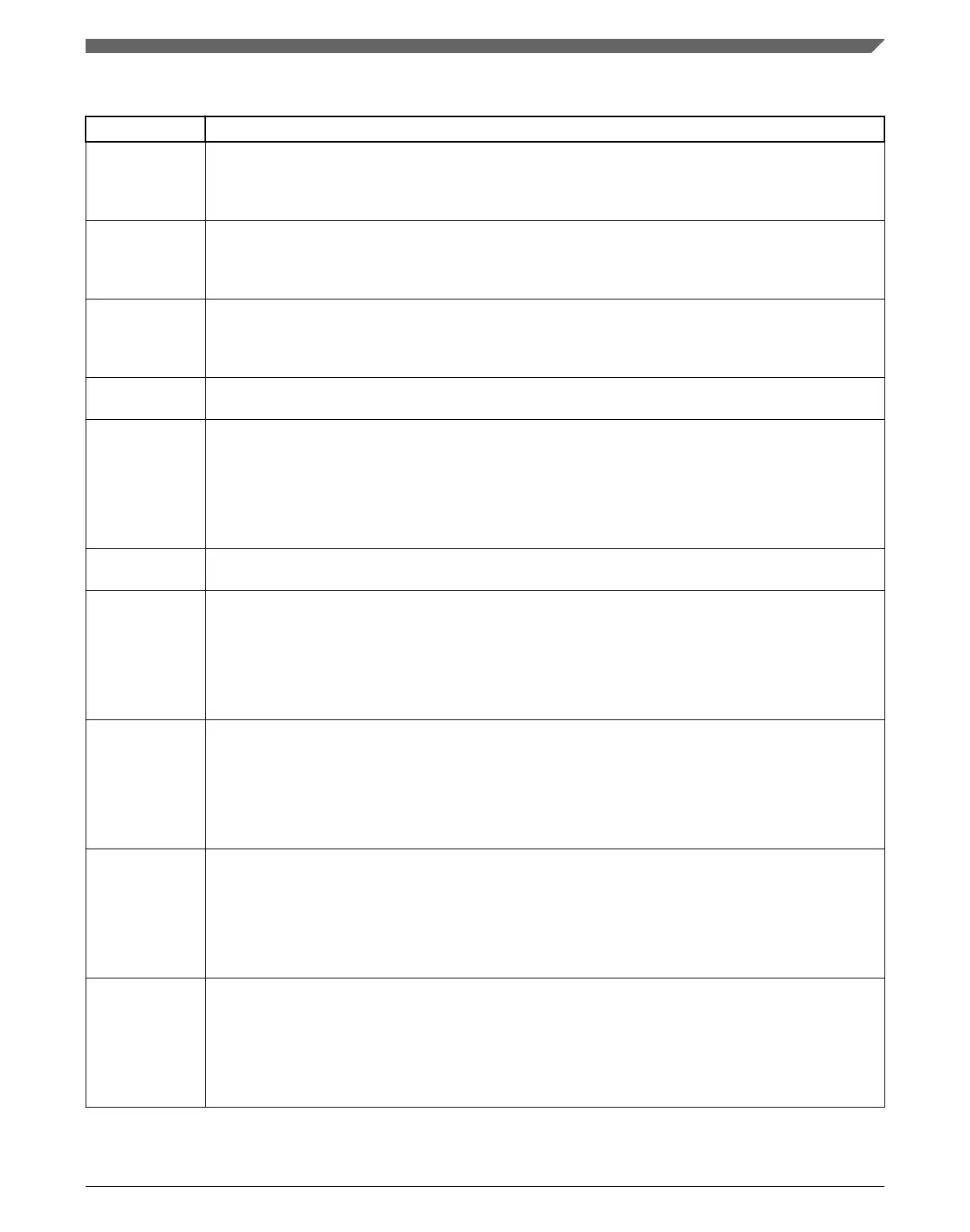

MCM_ISCR field descriptions (continued)

Field Description

26

FOFCE

FPU overflow interrupt enable

0 Disable interrupt

1 Enable interrupt

25

FDZCE

FPU divide-by-zero interrupt enable

0 Disable interrupt

1 Enable interrupt

24

FIOCE

FPU invalid operation interrupt enable

0 Disable interrupt

1 Enable interrupt

23–16

Reserved

This field is reserved.

15

FIDC

FPU input denormal interrupt status

This read-only bit is a copy of the core’s FPSCR[IDC] bit and signals input denormalized number has been

detected in the processor’s FPU. Once set, this bit remains set until software clears the FPSCR[IDC] bit.

0 No interrupt

1 Interrupt occurred

14–13

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

12

FIXC

FPU inexact interrupt status

This read-only bit is a copy of the core’s FPSCR[IXC] bit and signals an inexact number has been

detected in the processor’s FPU. Once set, this bit remains set until software clears the FPSCR[IXC] bit.

0 No interrupt

1 Interrupt occurred

11

FUFC

FPU underflow interrupt status

This read-only bit is a copy of the core’s FPSCR[UFC] bit and signals an underflow has been detected in

the processor’s FPU. Once set, this bit remains set until software clears the FPSCR[UFC] bit.

0 No interrupt

1 Interrupt occurred

10

FOFC

FPU overflow interrupt status

This read-only bit is a copy of the core’s FPSCR[OFC] bit and signals an overflow has been detected in

the processor’s FPU. Once set, this bit remains set until software clears the FPSCR[OFC] bit.

0 No interrupt

1 Interrupt occurred

9

FDZC

FPU divide-by-zero interrupt status

This read-only bit is a copy of the core’s FPSCR[DZC] bit and signals a divide by zero has been detected

in the processor’s FPU. Once set, this bit remains set until software clears the FPSCR[DZC] bit.

0 No interrupt

1 Interrupt occurred

Table continues on the next page...

Chapter 18 Miscellaneous Control Module (MCM)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 403

Loading...

Loading...