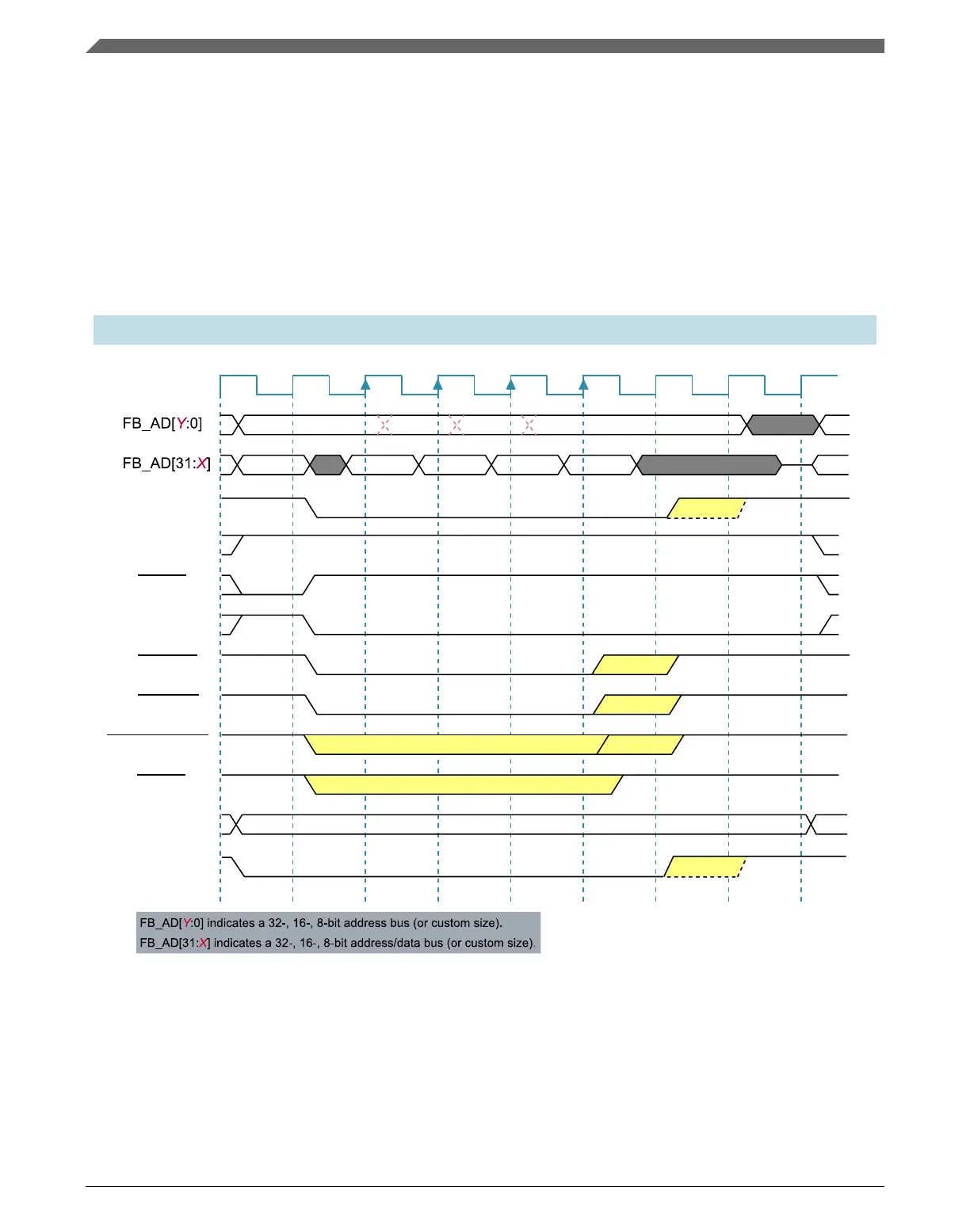

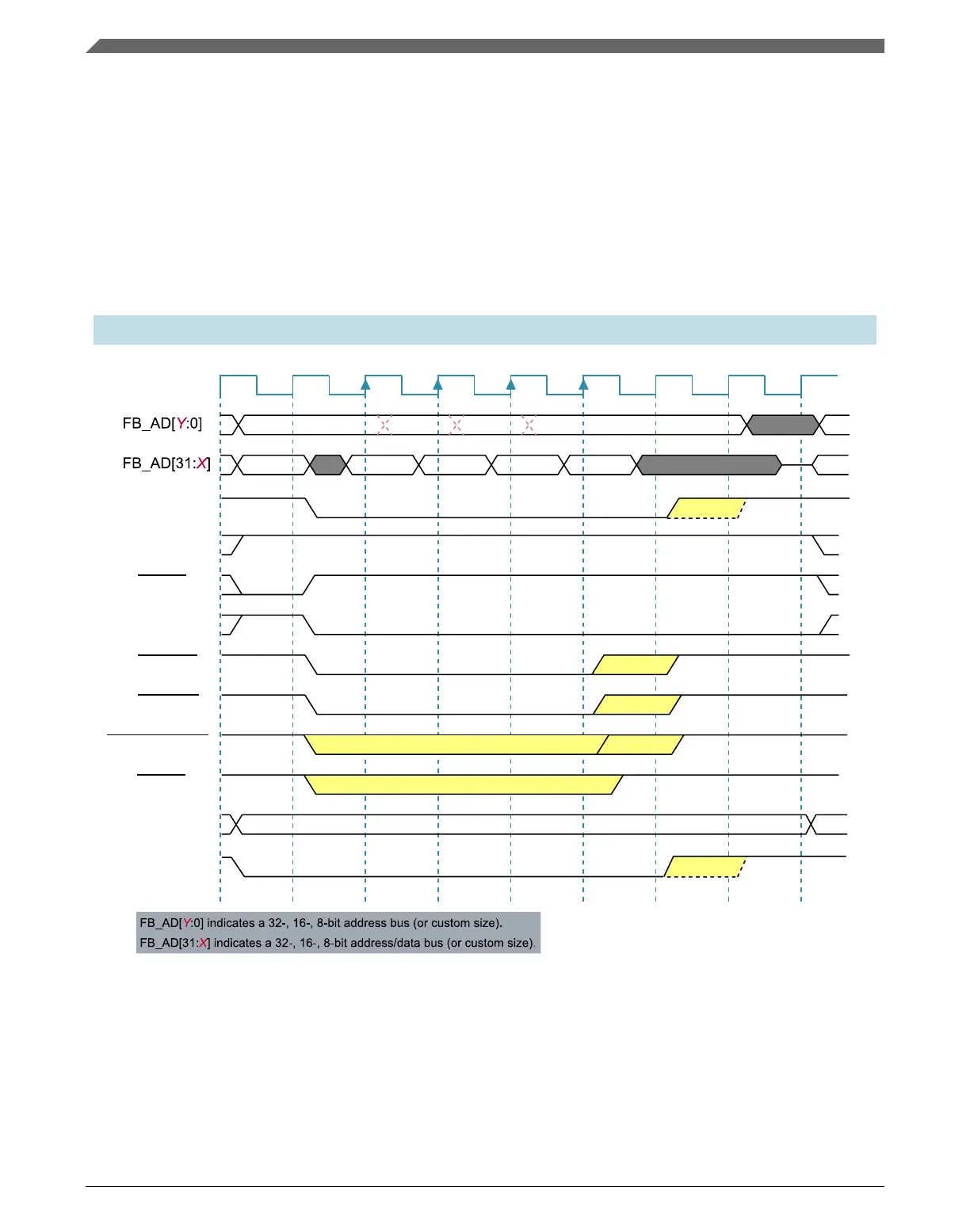

cycles. The first address is driven throughout the entire

burst for externally-terminated cycles.

• In multiplexed address/data mode: the address is driven

on FB_AD only during the first cycle for all terminated

cycles. In other words, the lower address lines only

increment during internally-terminated burst cycles

(assuming that the lower address lines are being driven

with the address during the data phase).

Address

Address DataData Data Data

Add+1 Add+2 Add+3

FB_CLK

FB_TBST

TSIZ =00

AA=1

AA=0

FB_RW

FB_TS

FB_ALE

FB_OEn

FB_BE/BWEn

FB_TA

FB_TSIZ[1:0]

FB_CSn

AA=1

AA=0

32-bit Read Burst from 8-bit port 2-1-1-1, with no Wait states

BEM=1

BEM=0

S0 S2 S2S2S1 S2 S3 ?

TIP

S0 S2 S2S2S1 S2 S3 S0

Read32bBurst2111.svg

S0

AA=1

AA=0

AA=1

AA=0

If AA=1, the address increments

If AA=0, the address stays the same

Figure 31-22. 32-bit-Read burst from 8-Bit port 2-1-1-1 (no wait states)

Functional description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

730 NXP Semiconductors

Loading...

Loading...