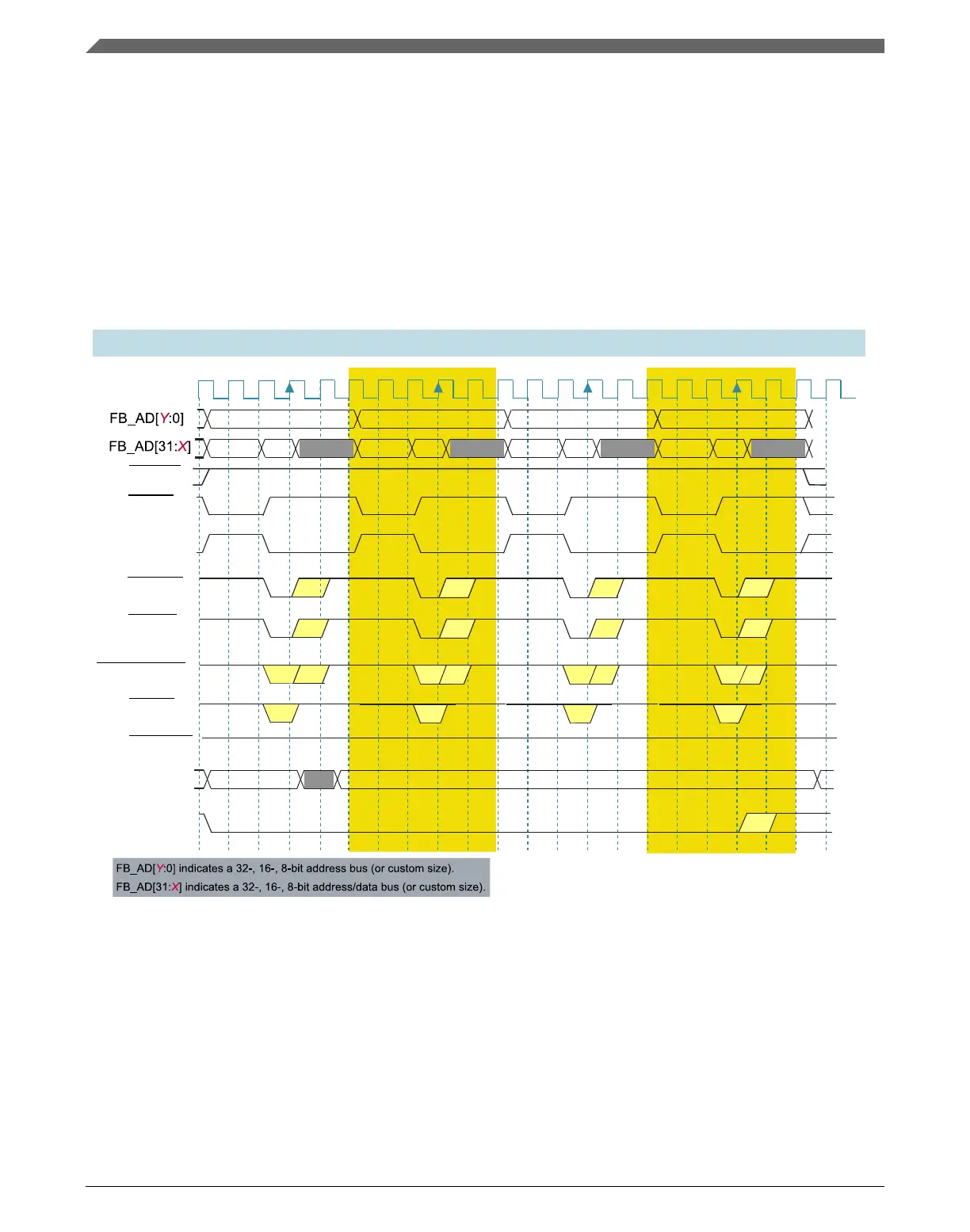

31.4.12.5 32-bit-read burst-inhibited from 8-bit port (no wait states)

The following figure shows a 32-bit read from an 8-bit device with burst inhibited. The

transfer results in four individual transfers. The transfer size is driven at 32-bit (00b)

during the first transfer and at byte (01b) during the next three transfers.

Note

There is an extra clock of address setup (AS) for each burst-

inhibited transfer between states S0 and S1.

AA=1

AA=0

FB_CLK

S2S1S0 AS S3

Address

S2S1S0 AS S3 S2S1S0 AS S3 S2S1S0 AS S3 S0 AS

Add+1

Add+2

Add+3

Add

Data

Add+1

Data

Add+2

Data

Add+3

Data

FB_RW

FB_TS

FB_ALEFB_ALE

FB_CSn

FB_OE

FB_BE/BWEn

FB_TA

FB_TBST

FB_TSIZ[1:0]

AA=1

AA=0

AA=1

AA=0

TSIZ=00 TSIZ=01

32-bit-read burst-inhibited to 8-bit port (no wait states)

TIP

AA=1

AA=0

AA=1

AA=0

AA=1

AA=0

BEM=0

BEM=1

Read32bBurstInhibit.svg

S2S1S0 AS S3 S2S1S0 AS S3 S2S1S0 AS S3 S2S1S0 AS S3 S0 AS

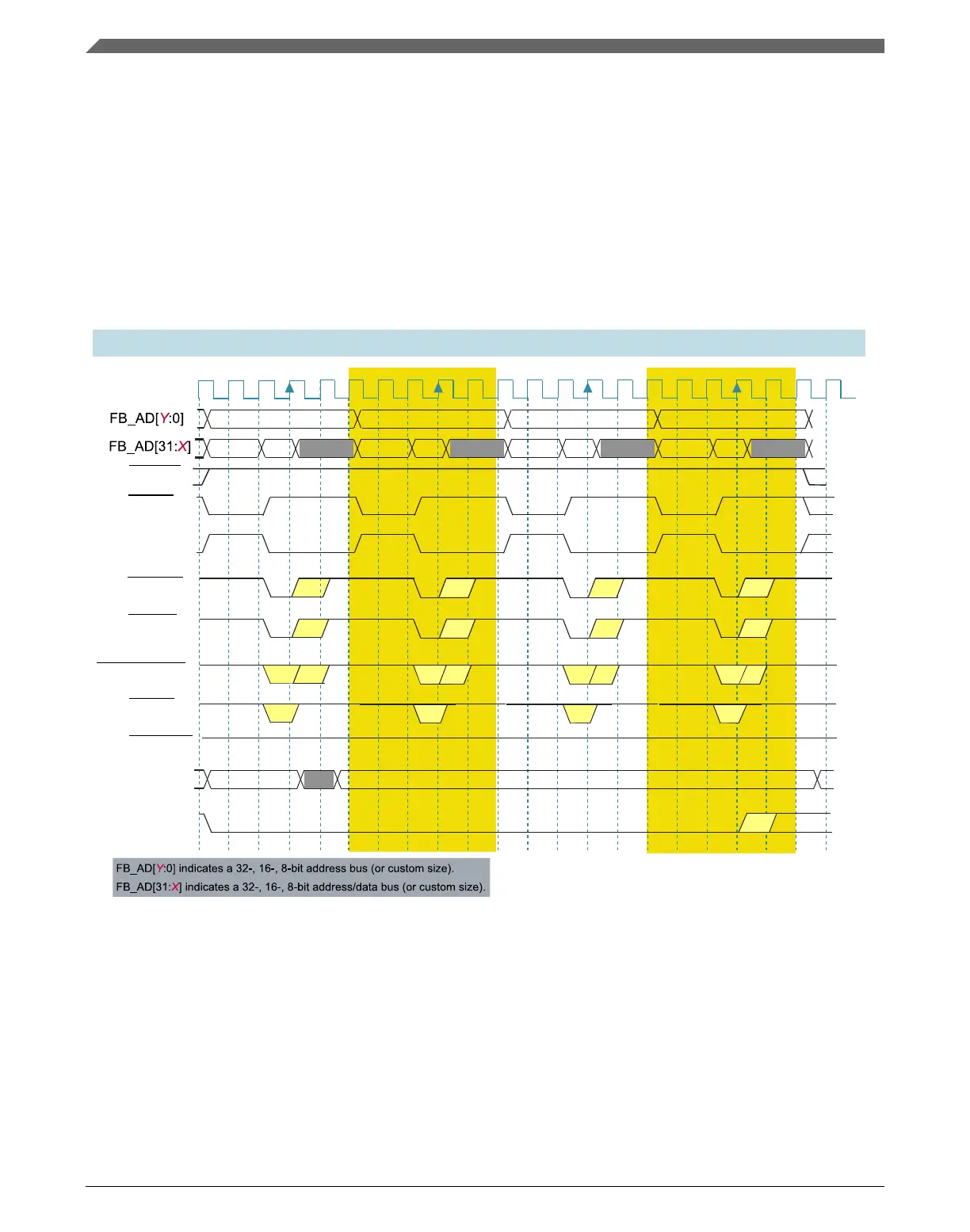

31.4.12.6 32-bit-write burst-inhibited to 8-bit port (no wait states)

The following figure shows a 32-bit write to an 8-bit device with burst inhibited. The

transfer results in four individual transfers. The transfer size is driven at 32-bit (00b)

during the first transfer and at byte (01b) during the next three transfers.

Functional description

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

732 NXP Semiconductors

Loading...

Loading...