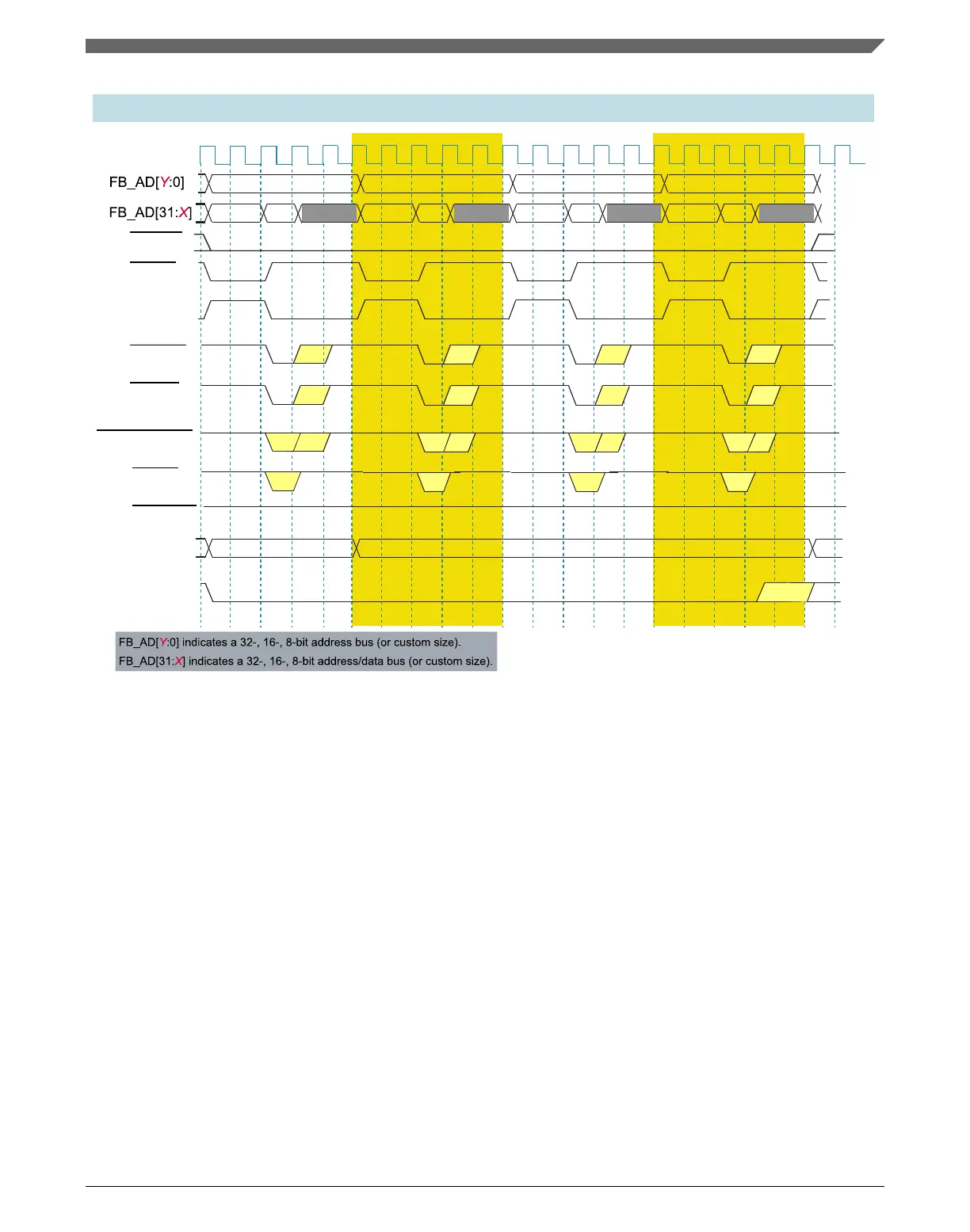

AA=1

AA=0

FB_CLK

S2S1S0 AS S3

Address

S2S1S0 AS S3 S2S1S0 AS S3 S2S1S0 AS S3 S0 AS

Add+1

Add+2

Add+3

Add

Data

Add+1

Data

Add+2

Data

Add+3

Data

FB_RW

FB_TS

FB_ALEFB_ALE

FB_CSn

FB_OE

FB_BE/BWEn

FB_TA

FB_TBST

FB_TSIZ[1:0]

AA=1

AA=0

AA=1

AA=0

TSIZ=00 TSIZ=01

32-bit-write burst-inhibited to 8-bit port (no wait states)

TIP

AA=1

AA=0

AA=1

AA=0

BEM=0

BEM=1

Write32bBurstInhibit.svg

S2S1S0 AS S3 S2S1S0 AS S3 S2S1S0 AS S3 S2S1S0 AS S3 S0 AS

Figure 31-24. 32-bit-write burst-inhibited to 8-bit port (no wait states)

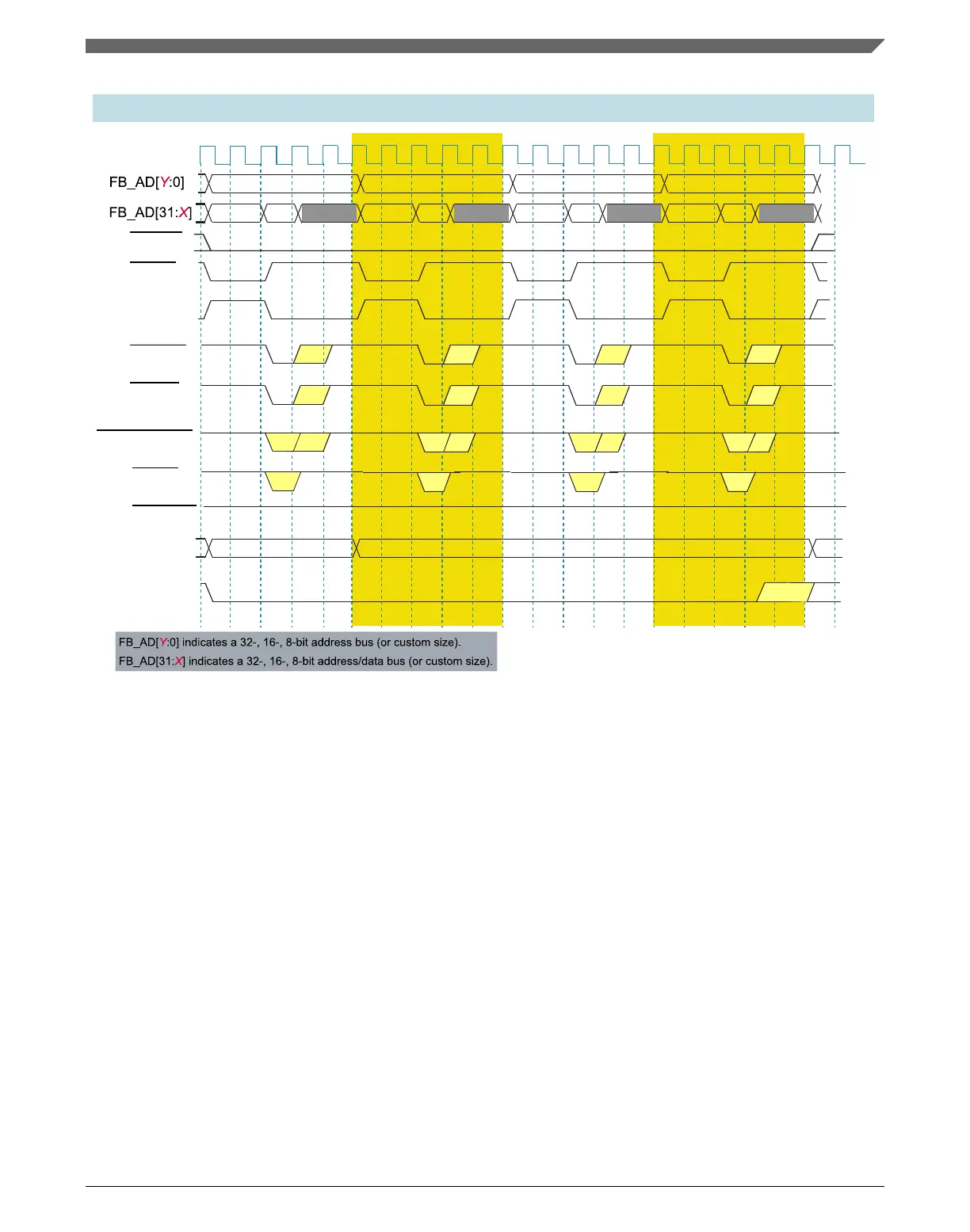

31.4.12.7

32-bit-read burst from 8-bit port 3-2-2-2 (one wait state)

The following figure illustrates another read burst transfer, but in this case a wait state is

added between individual beats.

Note

CSCRn[WS] determines the number of wait states in the first

beat. However, for subsequent beats, the CSCRn[WS] (or

CSCRn[SWS] if CSCRn[SWSEN] = 1b) determines the

number of wait states.

Chapter 31 External Bus Interface (FlexBus)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 733

Loading...

Loading...