Unused bits in R n are cleared in unsigned right-aligned modes and carry the sign bit

(MSB) in sign-extended 2's complement modes. For example, when configured for 10-bit

single-ended mode, D[15:10] are cleared. When configured for 11-bit differential mode,

D[15:10] carry the sign bit, that is, bit 10 extended through bit 15.

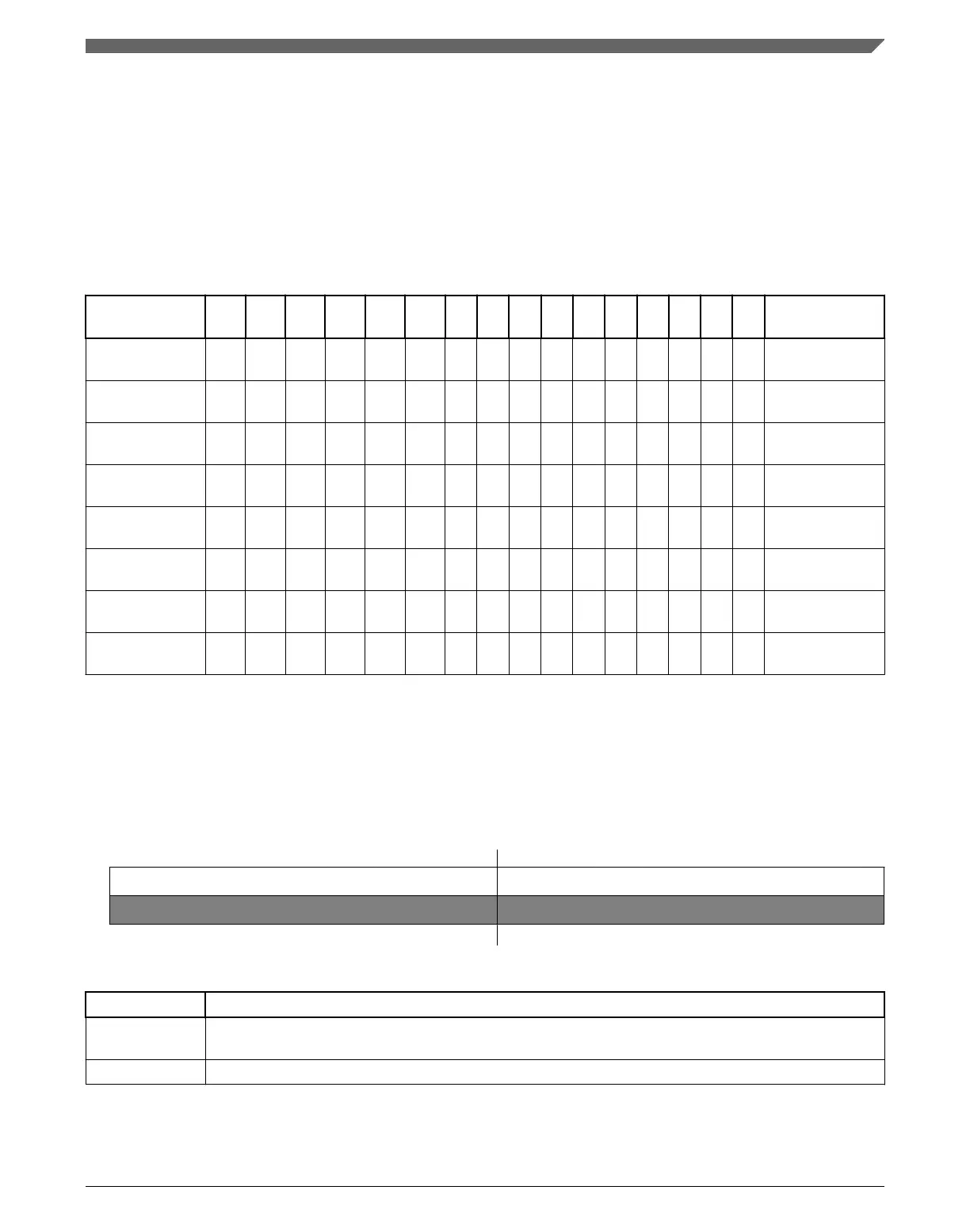

The following table describes the behavior of the data result registers in the different

modes of operation.

Table 34-2. Data result register description

Conversion

mode

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Format

16-bit differential S D D D D D D D D D D D D D D D Signed 2's

complement

16-bit single-

ended

D D D D D D D D D D D D D D D D Unsigned right

justified

13-bit differential S S S S D D D D D D D D D D D D Sign-extended

2's complement

12-bit single-

ended

0 0 0 0 D D D D D D D D D D D D Unsigned right-

justified

11-bit differential S S S S S S D D D D D D D D D D Sign-extended

2's complement

10-bit single-

ended

0 0 0 0 0 0 D D D D D D D D D D Unsigned right-

justified

9-bit differential S S S S S S S S D D D D D D D D Sign-extended

2's complement

8-bit single-

ended

0 0 0 0 0 0 0 0 D D D D D D D D Unsigned right-

justified

NOTE

S: Sign bit or sign bit extension;

D: Data, which is 2's complement data if indicated

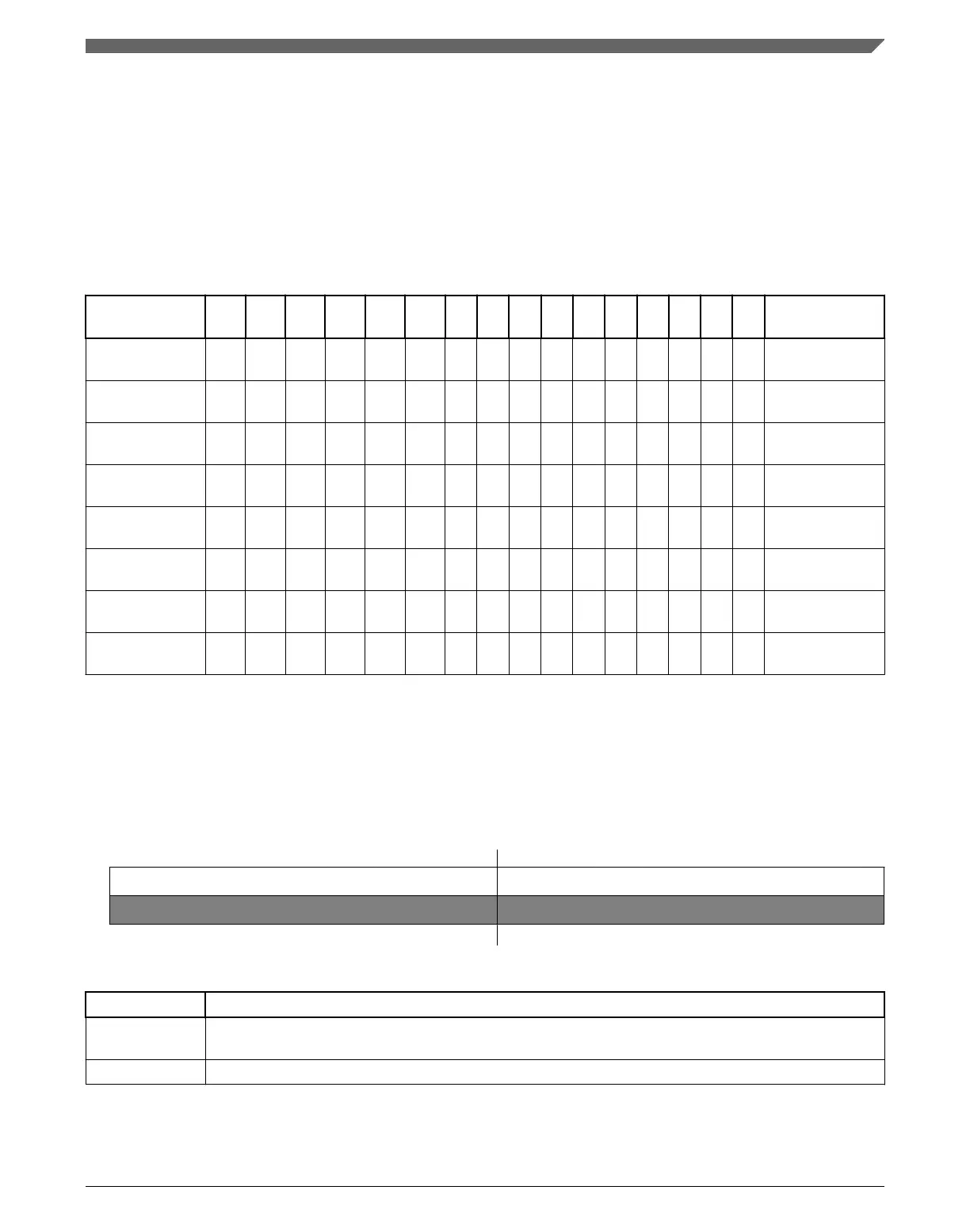

Address:

Base address + 10h offset + (4d × i), where i=0d to 1d

Bit 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

R

0 D

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

ADCx_Rn field descriptions

Field Description

31–16

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

D Data result

Chapter 34 Analog-to-Digital Converter (ADC)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 775

Loading...

Loading...