UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 152 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

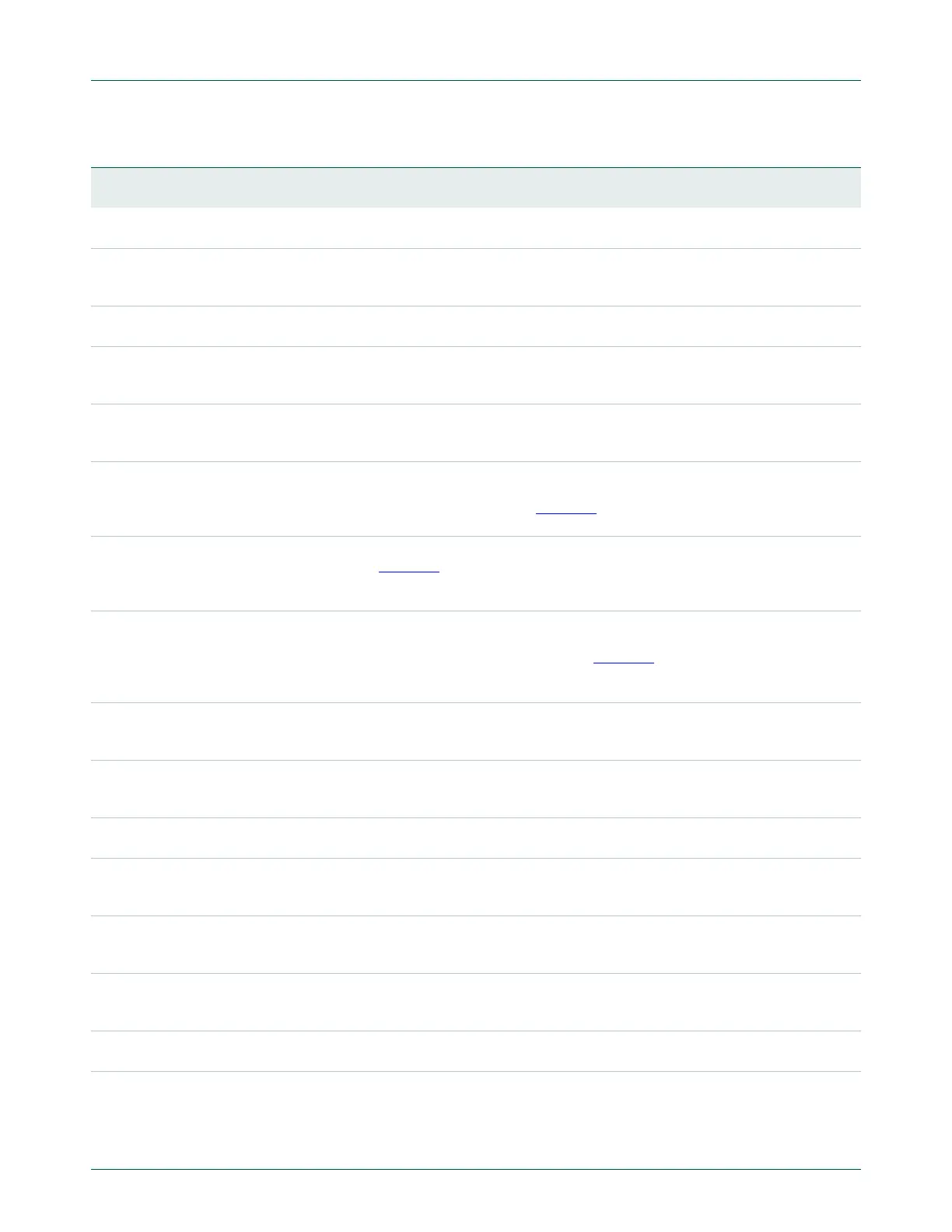

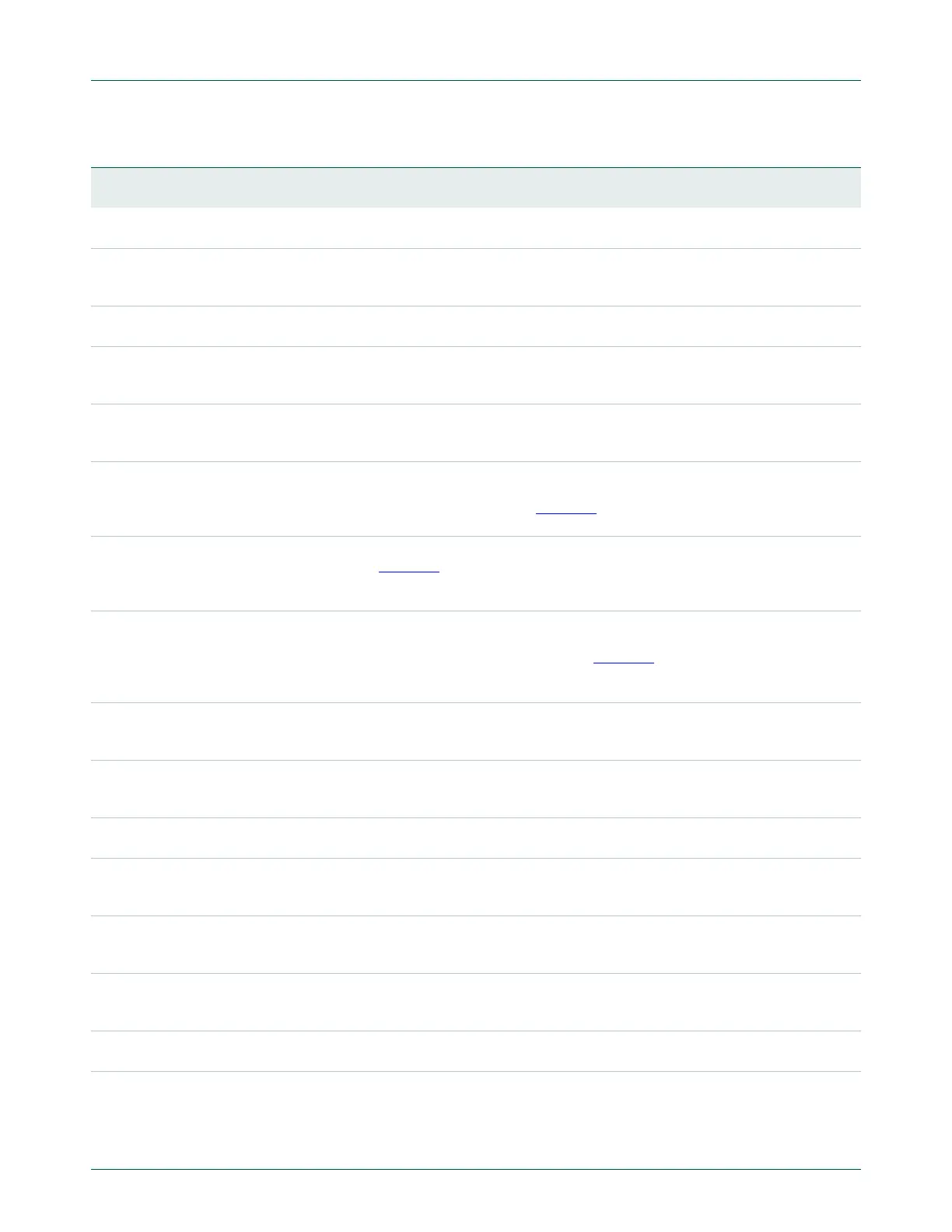

Table 130. MAC Configuration register 2 (MAC2 - address 0x5000 0004) bit description

Bit Symbol Function Reset

value

0 FULL-DUPLEX When enabled (set to ’1’), the MAC operates in Full-Duplex mode. When disabled,

the MAC operates in Half-Duplex mode.

0

1FRAME LENGTH

CHECKING

When enabled (set to ’1’), both transmit and receive frame lengths are compared to

the Length/Type field. If the Length/Type field represents a length then the check is

performed. Mismatches are reported in the StatusInfo word for each received frame.

0

2 HUGE FRAME

ENABLE

When enabled (set to ’1’), frames of any length are transmitted and received. 0

3 DELAYED CRC This bit determines the number of bytes, if any, of proprietary header information

that exist on the front of IEEE 802.3 frames. When 1, four bytes of header (ignored

by the CRC function) are added. When 0, there is no proprietary header.

0

4 CRC ENABLE Set this bit to append a CRC to every frame whether padding was required or not.

Must be set if PAD/CRC ENABLE is set. Clear this bit if frames presented to the

MAC contain a CRC.

0

5 PAD / CRC ENABLE Set this bit to have the MAC pad all short frames. Clear this bit if frames presented

to the MAC have a valid length. This bit is used in conjunction with AUTO PAD

ENABLE and VLAN PAD ENABLE. See Table 132

- Pad Operation for details on the

pad function.

0

6 VLAN PAD ENABLE Set this bit to cause the MAC to pad all short frames to 64 bytes and append a valid

CRC. Consult Table 132

- Pad Operation for more information on the various

padding features.

Note: This bit is ignored if PAD / CRC ENABLE is cleared.

0

7 AUTO DETECT PAD

ENABLE

Set this bit to cause the MAC to automatically detect the type of frame, either tagged

or un-tagged, by comparing the two octets following the source address with

0x8100 (VLAN Protocol ID) and pad accordingly. Table 132

- Pad Operation

provides a description of the pad function based on the configuration of this register.

Note: This bit is ignored if PAD / CRC ENABLE is cleared.

0

8 PURE PREAMBLE

ENFORCEMENT

When enabled (set to ’1’), the MAC will verify the content of the preamble to ensure

it contains 0x55 and is error-free. A packet with an incorrect preamble is discarded.

When disabled, no preamble checking is performed.

0

9 LONG PREAMBLE

ENFORCEMENT

When enabled (set to ’1’), the MAC only allows receive packets which contain

preamble fields less than 12 bytes in length. When disabled, the MAC allows any

length preamble as per the Standard.

0

11:10 - Reserved. User software should not write ones to reserved bits. The value read

from a reserved bit is not defined.

0x0

12 NO BACKOFF When enabled (set to ’1’), the MAC will immediately retransmit following a collision

rather than using the Binary Exponential Backoff algorithm as specified in the

Standard.

0

13 BACK PRESSURE /

NO BACKOFF

When enabled (set to ’1’), after the MAC incidentally causes a collision during back

pressure, it will immediately retransmit without backoff, reducing the chance of

further collisions and ensuring transmit packets get sent.

0

14 EXCESS DEFER When enabled (set to ’1’) the MAC will defer to carrier indefinitely as per the

Standard. When disabled, the MAC will abort when the excessive deferral limit is

reached.

0

31:15 - Reserved. User software should not write ones to reserved bits. The value read

from a reserved bit is not defined.

0x0

Loading...

Loading...