UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 204 of 841

NXP Semiconductors

UM10360

Chapter 10: LPC176x/5x Ethernet

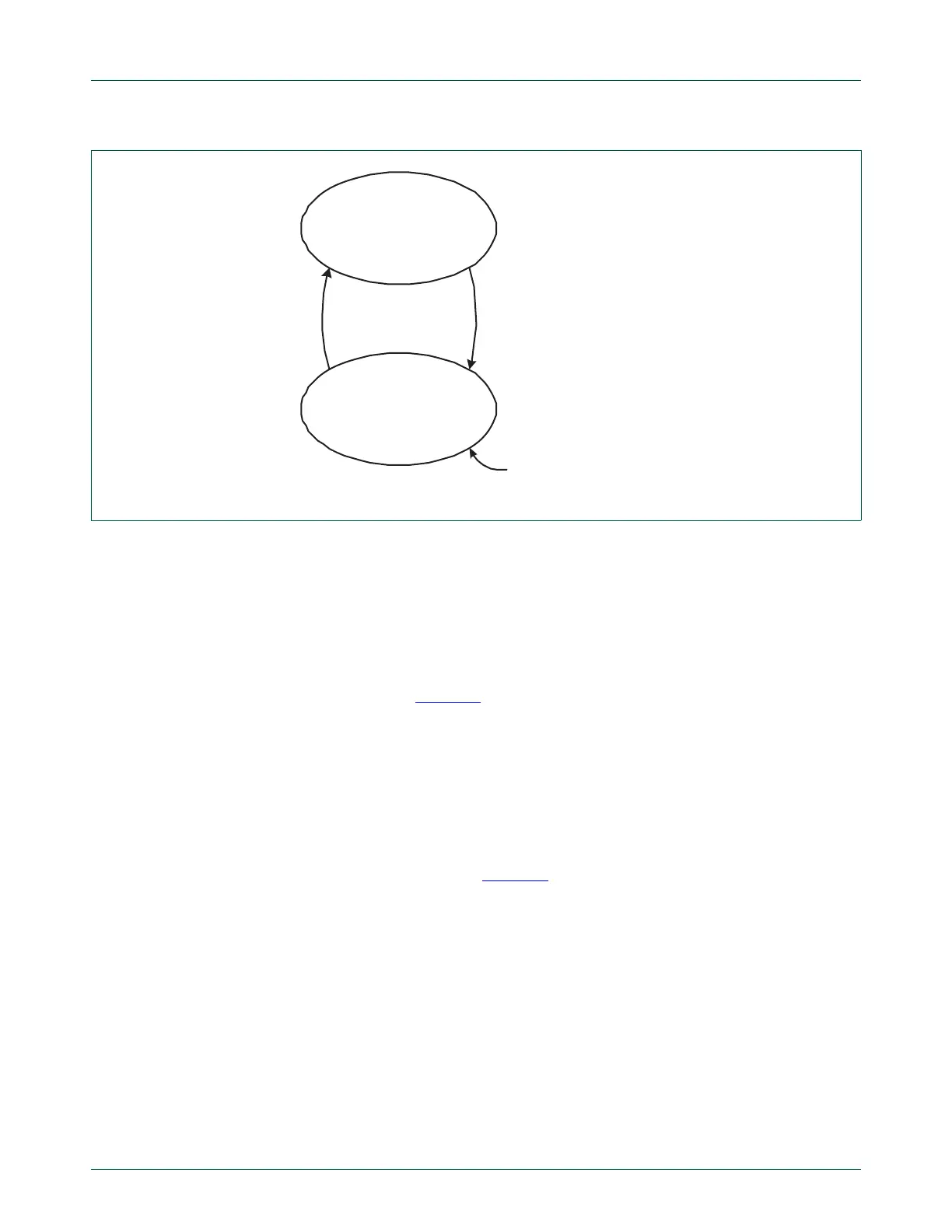

After a reset, the state machine is in the INACTIVE state. As soon as the RxEnable bit is

set in the Command register, the state machine transitions to the ACTIVE state. As soon

as the RxEnable bit is cleared, the state machine returns to the INACTIVE state. If the

receive data path is busy receiving a packet while the receive data path gets disabled, the

packet will be received completely, stored to memory along with its status before returning

to the INACTIVE state. Also if the Receive descriptor array is full, the state machine will

return to the INACTIVE state.

For the state machine in Figure 25

, a soft reset is like a hardware reset assertion, i.e. after

a soft reset the receive data path is inactive until the data path is re-enabled.

Enabling and disabling transmission

After reset, the transmit function of the Ethernet block is disabled. The Tx transmit data

path can be enabled by the device driver setting the TxEnable bit in the Command

register to 1.

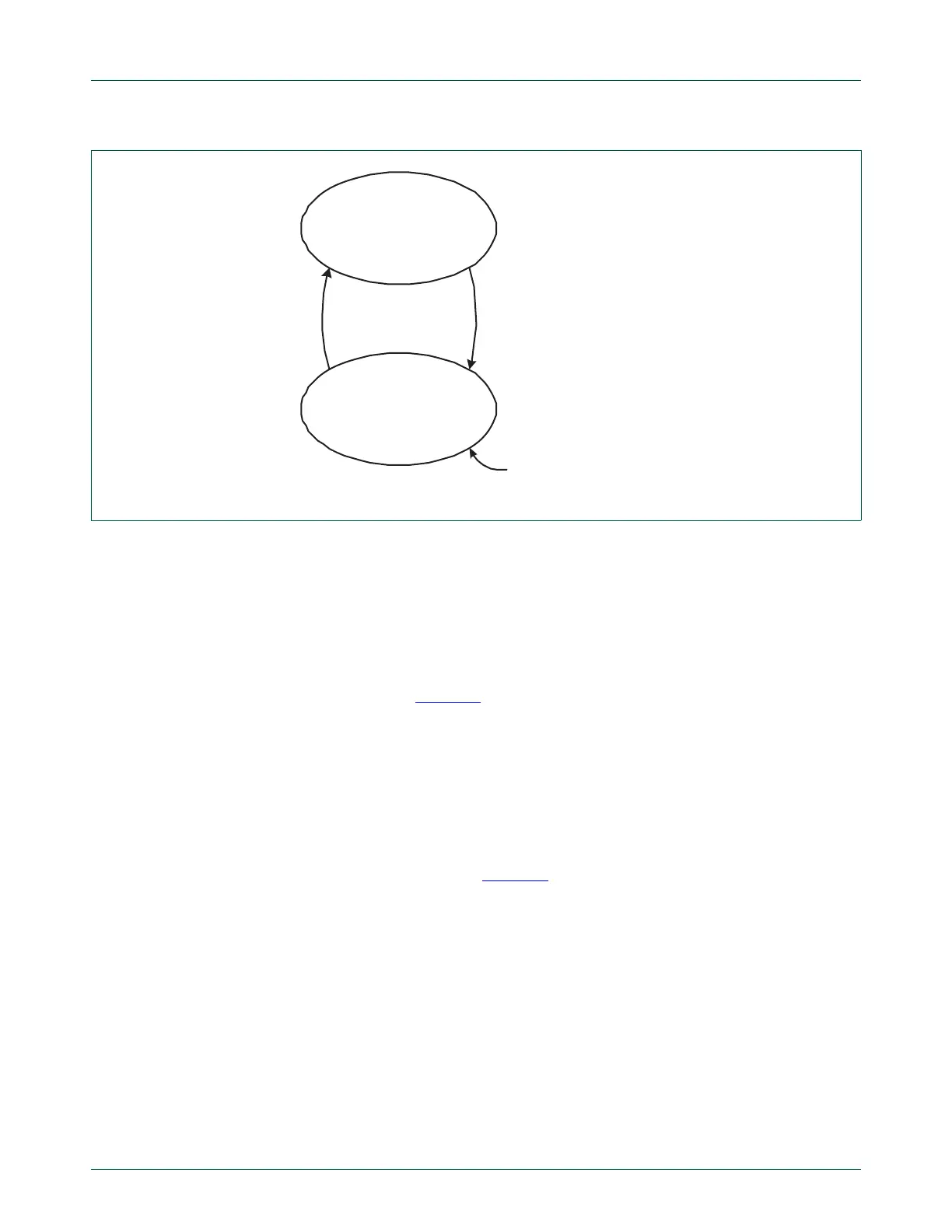

The status of the transmit data paths can be monitored by the device driver reading the

TxStatus bit of the Status register. Figure 26

illustrates the state machine for the

generation of the TxStatus bit.

Fig 25. Receive Active/Inactive state machine

ACTIVE

RxStatus = 1

INACTIVE

RxStatus = 0

RxEnable = 1

RxEnable = 0 and not busy receiving

OR

RxProduceIndex = RxConsumeIndex - 1

reset

xxxxxxxxxxxxxxxxxx

Loading...

Loading...