UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2013. All rights reserved.

User manual Rev. 3 — 19 December 2013 504 of 841

NXP Semiconductors

UM10360

Chapter 22: LPC176x/5x Repetitive Interrupt Timer (RIT)

Counting can be halted in software by writing a ‘0’ to the Enable_Timer bit - RICTRL(3).

Counting will also be halted when the processor is halted for debugging provided the

Enable_Break bit – RICTRL(2) is set. Both the Enable_Timer and Enable_Break bits are

set on reset.

The interrupt flag can be cleared in software by writing a ‘1’ to the Interrupt bit –

RICTRL(0).

Software can load the counter to any value at any time by writing to RICOUNTER.

The counter (RICOUNTER), RICOMPVAL register, RIMASK register and RICTRL register

can all be read by software at any time.

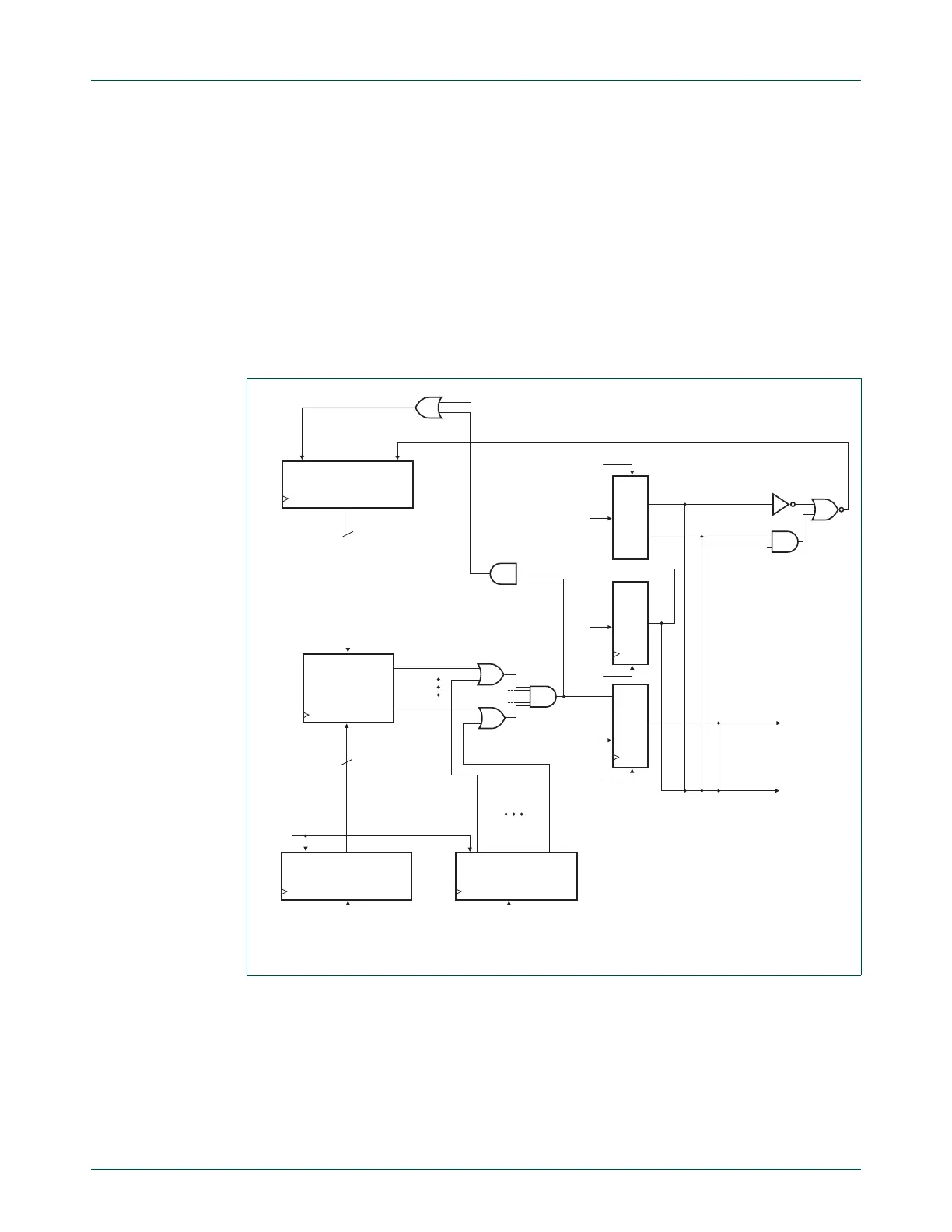

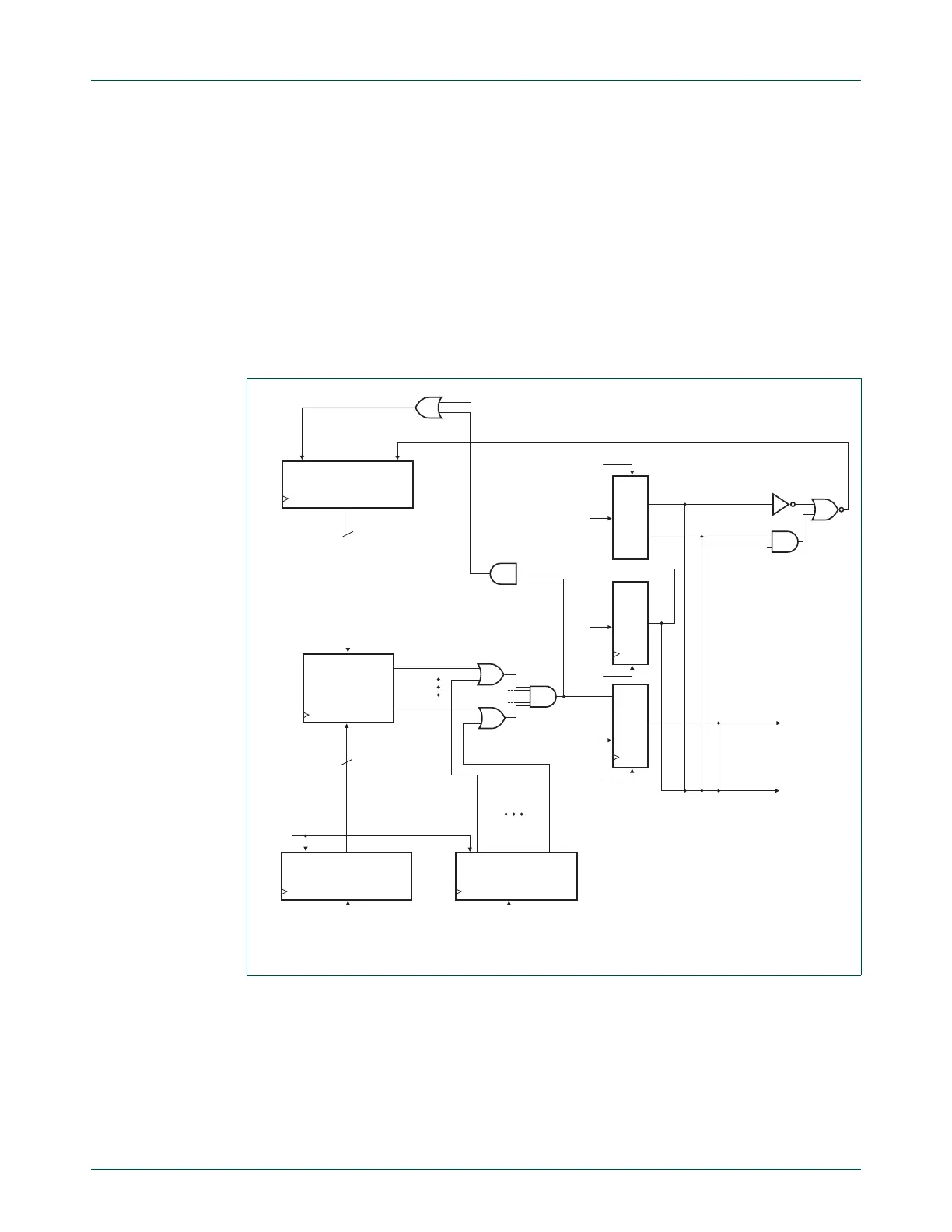

Fig 117. RI timer block diagram

32-bit COUNTER

CLR

ENA

COMPARATOR

SET

SET

3

2

S

C

CLR

EQ

EQ

0

ENABLE_TIMER

ENABLE_BREAK

BREAK

INTR

PBUS

PBUS

PBUS

RESET

RESET

RESET

SET_INT

32

32

PBUS

write '1' to

clear

PBUS

PBUS

CLR

RESET

CNT_ENA

CTRL

register

CLR

RESET

ENABLE_CLK

COMPARE

register

MASK

register

bit 0

(MASK)

bit 31

(MASK)

32 X

32 Xbit 0

compare

bit 32

compare

.

.

.

Loading...

Loading...