RM0444 Rev 5 1255/1390

RM0444 FD controller area network (FDCAN)

1261

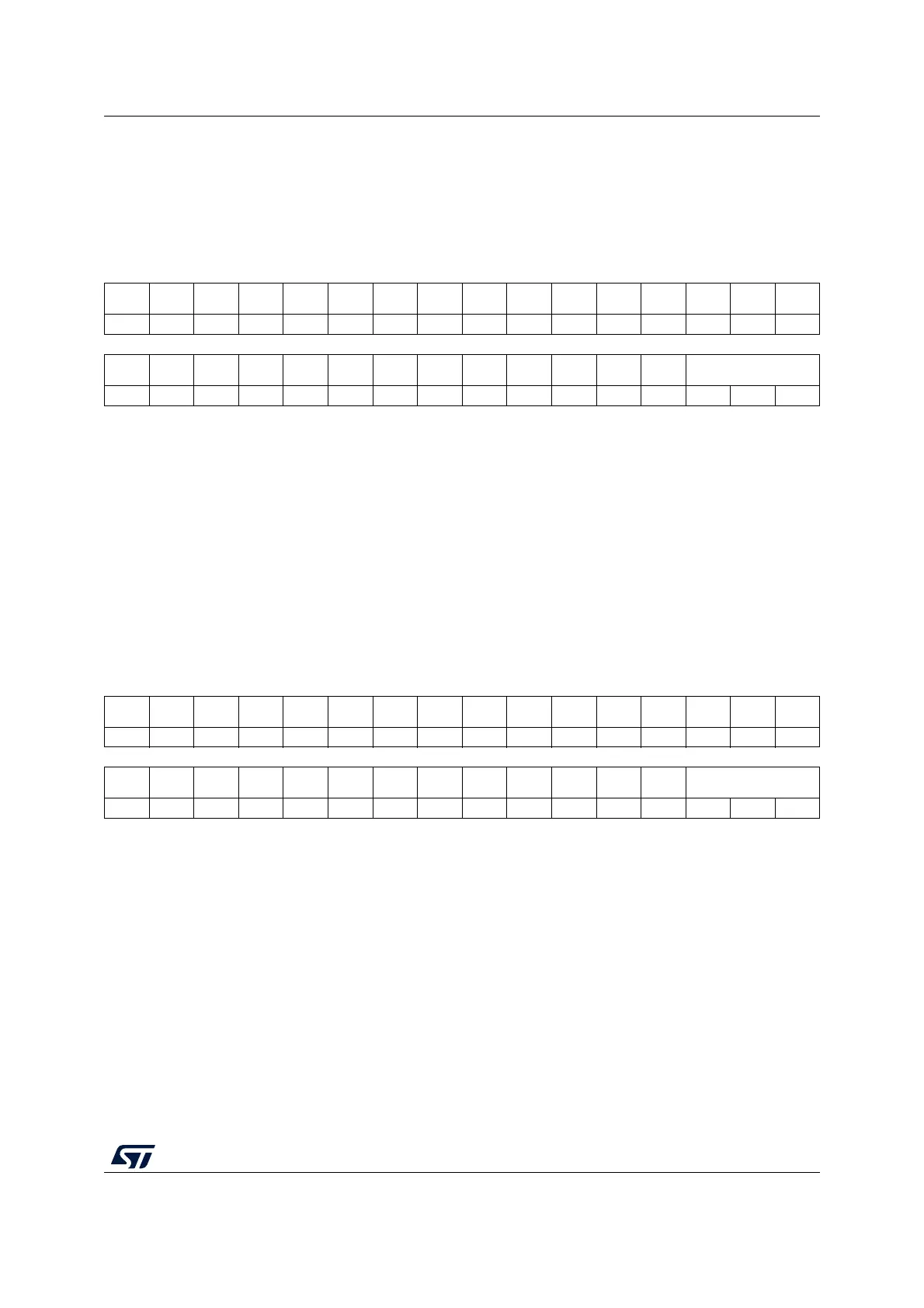

36.4.33 FDCAN Tx buffer transmission interrupt enable register

(FDCAN_TXBTIE)

Address offset: 0x00DC

Reset value: 0x0000 0000

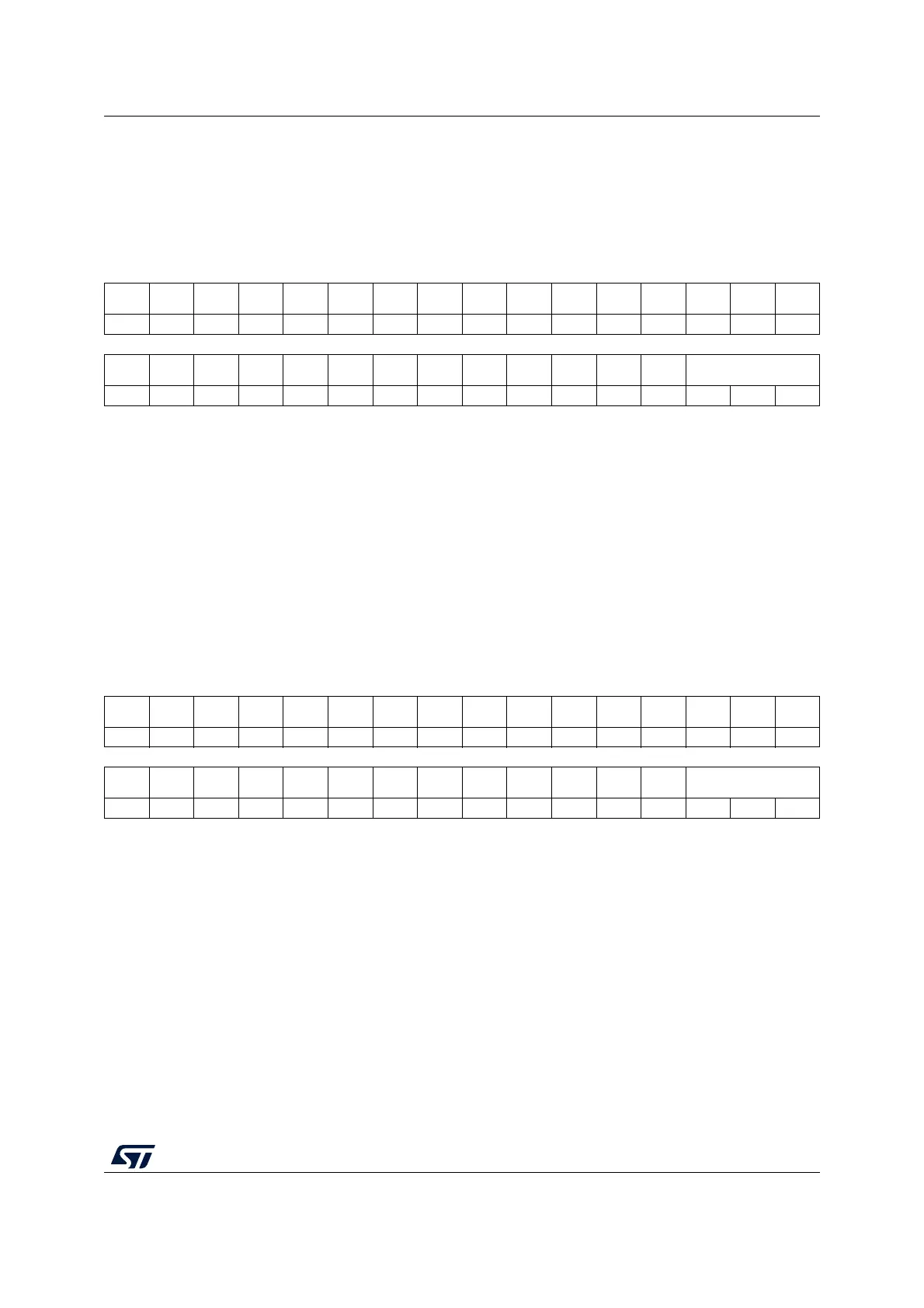

36.4.34 FDCAN Tx buffer cancellation finished interrupt enable register

(FDCAN_ TXBCIE)

Address offset: 0x00E0

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TIE[2:0]

rw rw rw

Bits 31:3 Reserved, must be kept at reset value.

Bits 2:0 TIE[2:0]: Transmission interrupt enable

Each Tx buffer has its own TIE bit.

0: Transmission interrupt disabled

1: Transmission interrupt enable

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. CFIE[2:0]

rw rw rw

Bits 31:3 Reserved, must be kept at reset value.

Bits 2:0 CFIE[2:0]: Cancellation finished interrupt enable.

Each Tx buffer has its own CFIE bit.

0: Cancellation finished interrupt disabled

1: Cancellation finished interrupt enabled

Loading...

Loading...