RM0444 Rev 5 147/1390

RM0444 Power control (PWR)

159

4.4.4 Power control register 4 (PWR_CR4)

Address offset: 0x0C

Reset value: 0x0000 0000. This register is not reset when exiting Standby modes and with

the PWRRST bit in the APB peripheral reset register 1 (RCC_APBRSTR1).

Access: Additional APB cycles are needed to access this register vs. a standard APB

access (3 for a write and 2 for a read).

Bit 4 EWUP5: Enable WKUP5 wakeup pin

When this bit is set, the WKUP5 external wakeup pin is enabled and triggers a wakeup from

Standby or Shutdown mode when a rising or a falling edge occurs.The active edge is

configured via the WP5 bit in the PWR_CR4 register.

Bit 3 EWUP4: Enable WKUP4 wakeup pin

When this bit is set, the WKUP4 external wakeup pin is enabled and triggers a wakeup from

Standby or Shutdown mode when a rising or a falling edge occurs. The active edge is

configured via the WP4 bit in the PWR_CR4 register.

Bit 2 EWUP3: Enable WKUP3 wakeup pin

When this bit is set, the WKUP3 external wakeup pin is enabled and triggers a wakeup from

Standby or Shutdown mode when a rising or a falling edge occurs. The active edge is

configured via the WP3 bit of the PWR_CR4 register.

Bit 1 EWUP2: Enable WKUP2 wakeup pin

When this bit is set, the WKUP2 external wakeup pin is enabled and triggers a wakeup from

Standby or Shutdown mode when a rising or a falling edge occurs. The active edge is

configured via the WP2 bit of the PWR_CR4 register.

Bit 0 EWUP1: Enable WKUP1 wakeup pin

When this bit is set, the WKUP1 external wakeup pin is enabled and triggers a wakeup from

Standby or Shutdown mode when a rising or a falling edge occurs. The active edge is

configured via the WP1 bit of the PWR_CR4 register.

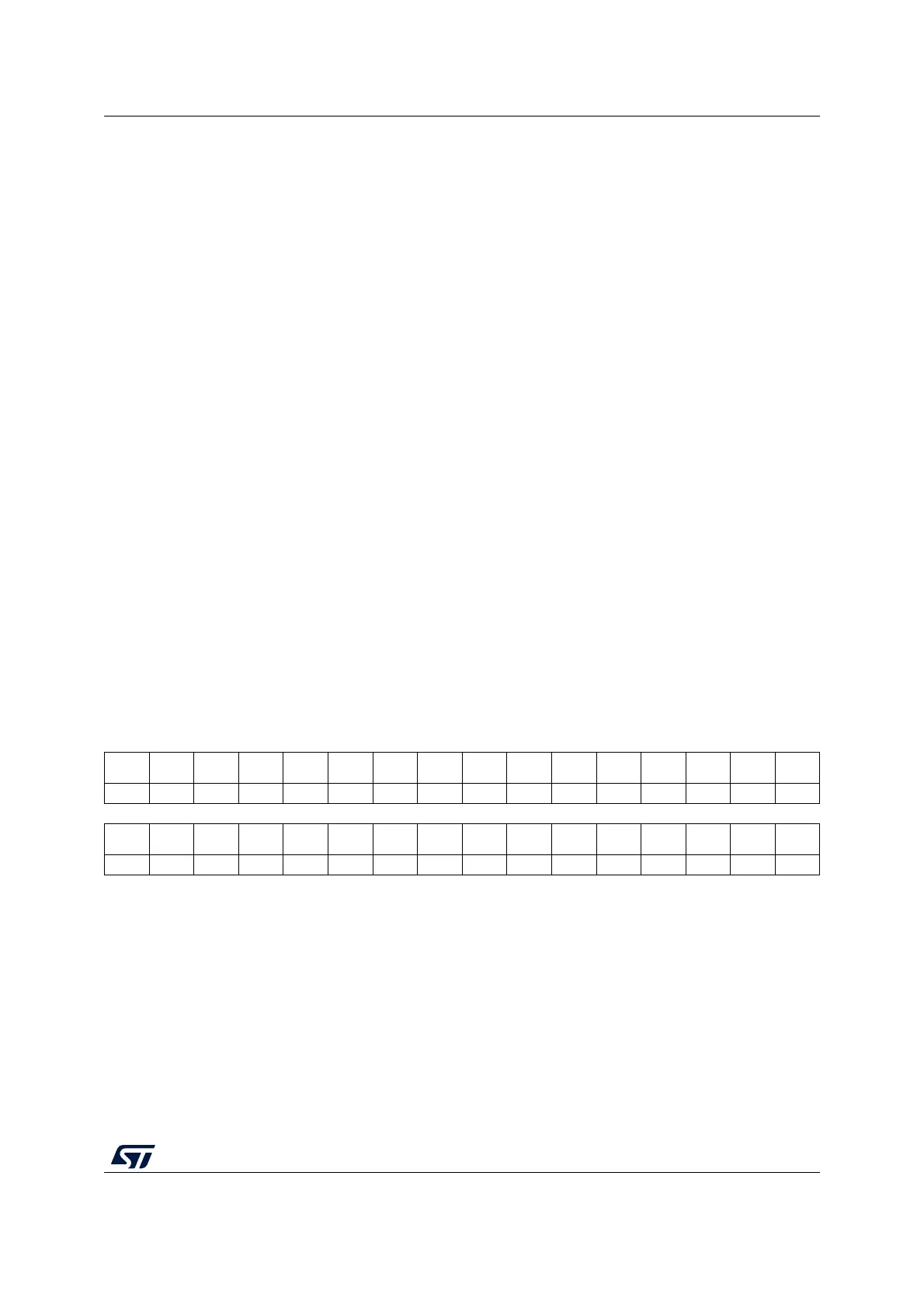

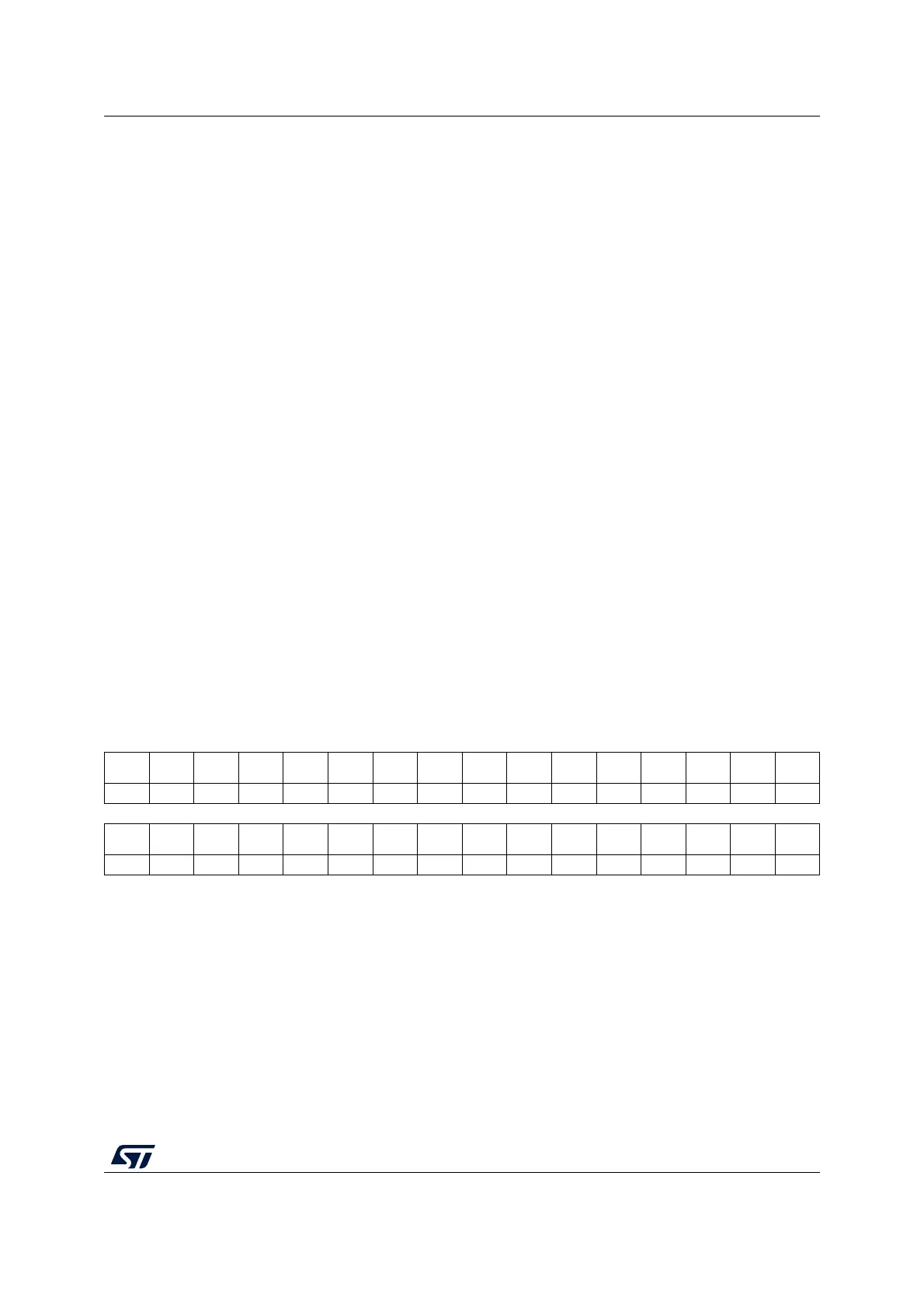

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. VBRS VBE Res. Res. WP6 WP5 WP4 WP3 WP2 WP1

rw rw rw rw rw rw rw rw

Bits 31:10 Reserved, must be kept at reset value.

Bit 9 VBRS: V

BAT

battery charging resistor selection

0: 5 kΩ

1: 1.5 kΩ

Bit 8 VBE: V

BAT

battery charging enable

0: Disable

1: Enable

Bits 7:6 Reserved, must be kept at reset value.

Loading...

Loading...