HDMI-CEC controller (CEC) RM0444

1360/1390 RM0444 Rev 5

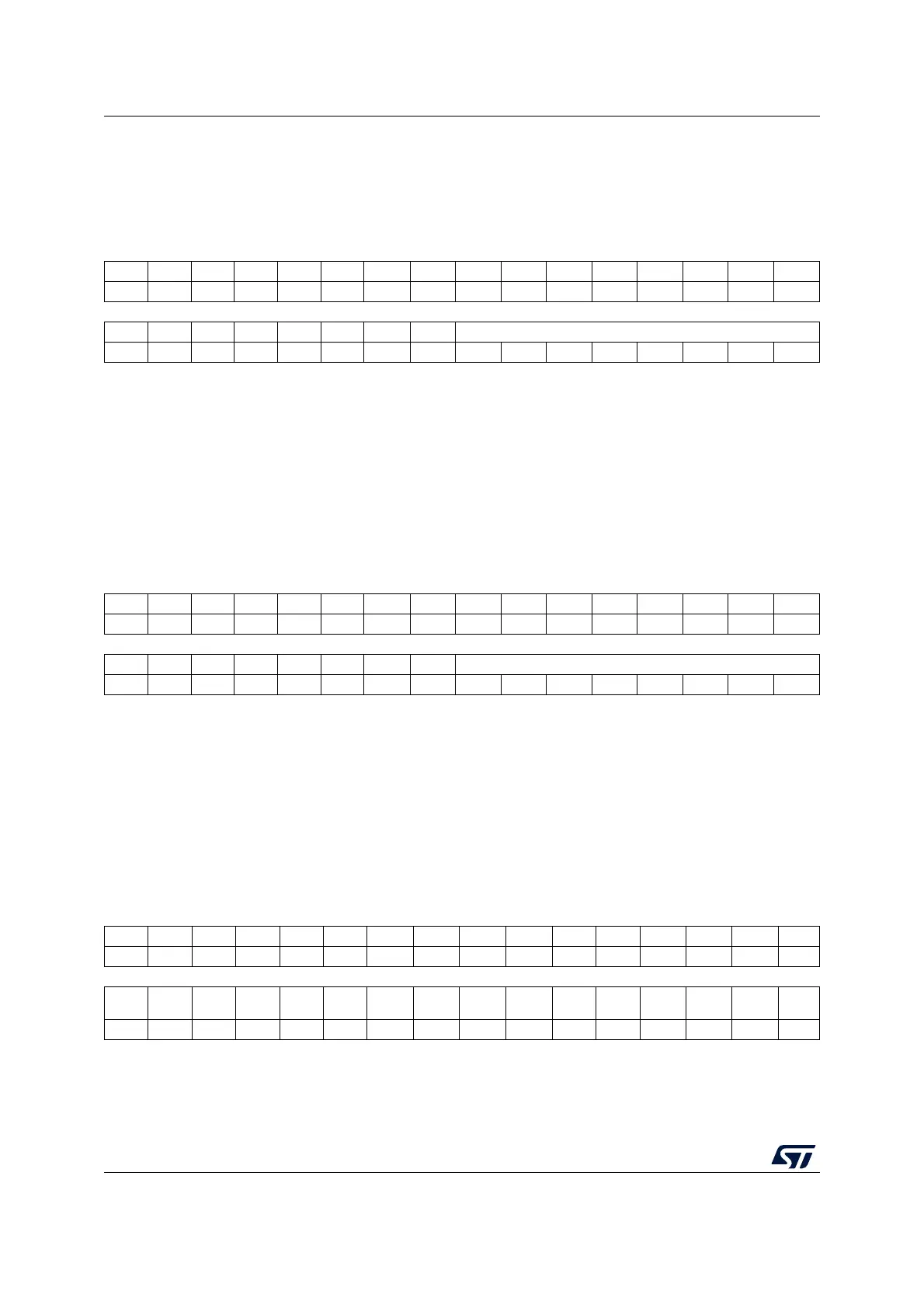

39.7.3 CEC Tx data register (CEC_TXDR)

Address offset: 0x8

Reset value: 0x0000 0000

39.7.4 CEC Rx data register (CEC_RXDR)

Address offset: 0xC

Reset value: 0x0000 0000

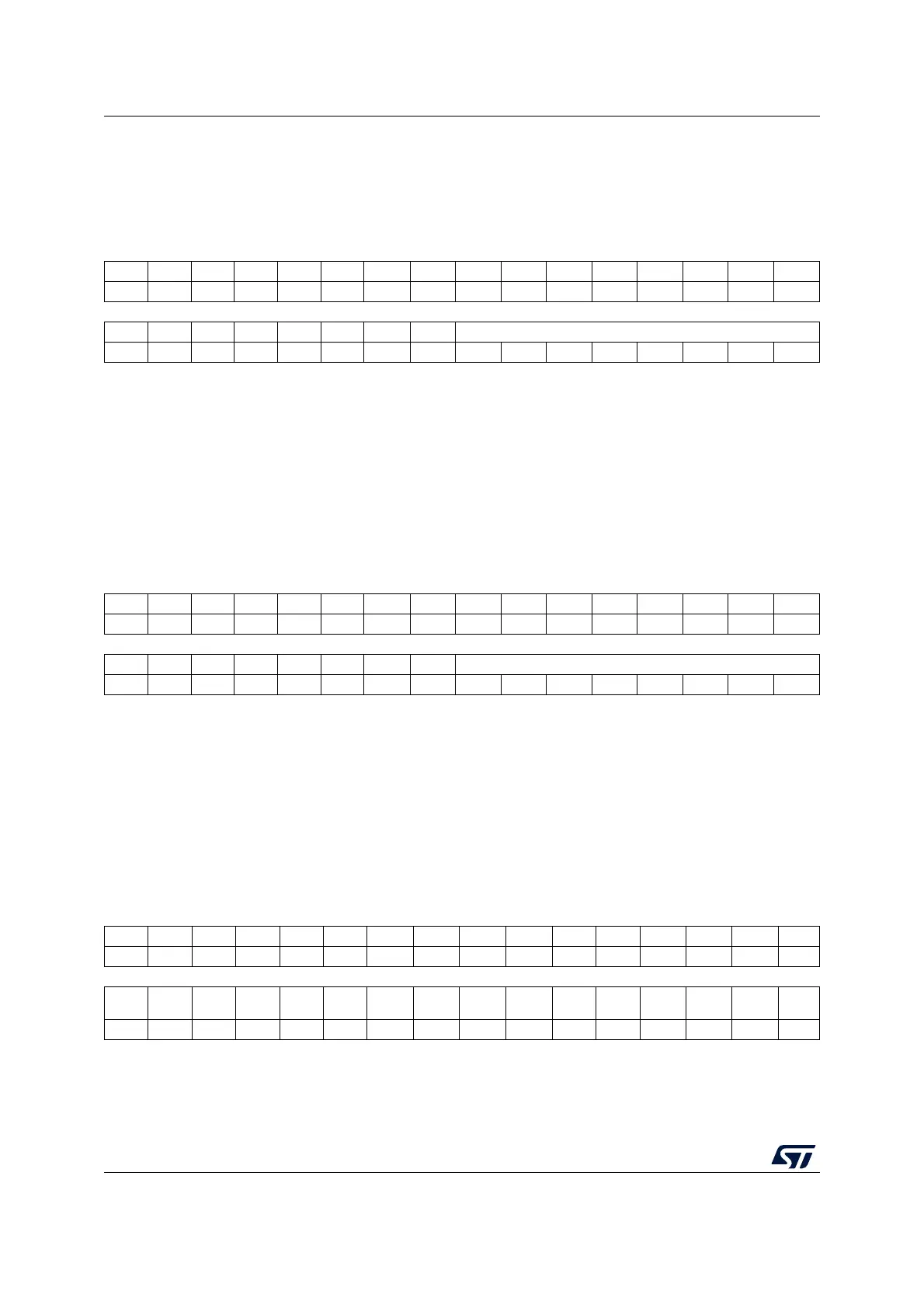

39.7.5 CEC interrupt and status register (CEC_ISR)

Address offset: 0x10

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. TXD[7:0]

wwwwwwww

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 TXD[7:0]: Tx data

TXD is a write-only register containing the data byte to be transmitted.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. RXD[7:0]

rrrrrrrr

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 RXD[7:0]: Rx data

RXD is read-only and contains the last data byte that has been received from the CEC line.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res.

TX

ACKE

TX

ERR

TX

UDR

TX

END

TXBR

ARB

LST

RX

ACKE

LBPE SBPE BRE

RX

OVR

RX

END

RXBR

rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1 rc_w1

Loading...

Loading...