HDMI-CEC controller (CEC) RM0444

1354/1390 RM0444 Rev 5

39.5.6 Transmission error detection (TXERR)

The CEC initiator sets the TXERR flag if detecting low impedance on the CEC line when it is

transmitting high impedance and is not expecting a follower asserted bit. TXERR flag also

generates a CEC interrupt if the TXERRIE = 1.

TXERR assertion stops the message transmission. Application is in charge to retry the

failed transmission up to five times.

TXERR checks are performed differently depending on the different states of the CEC line

and on the RX tolerance configuration.

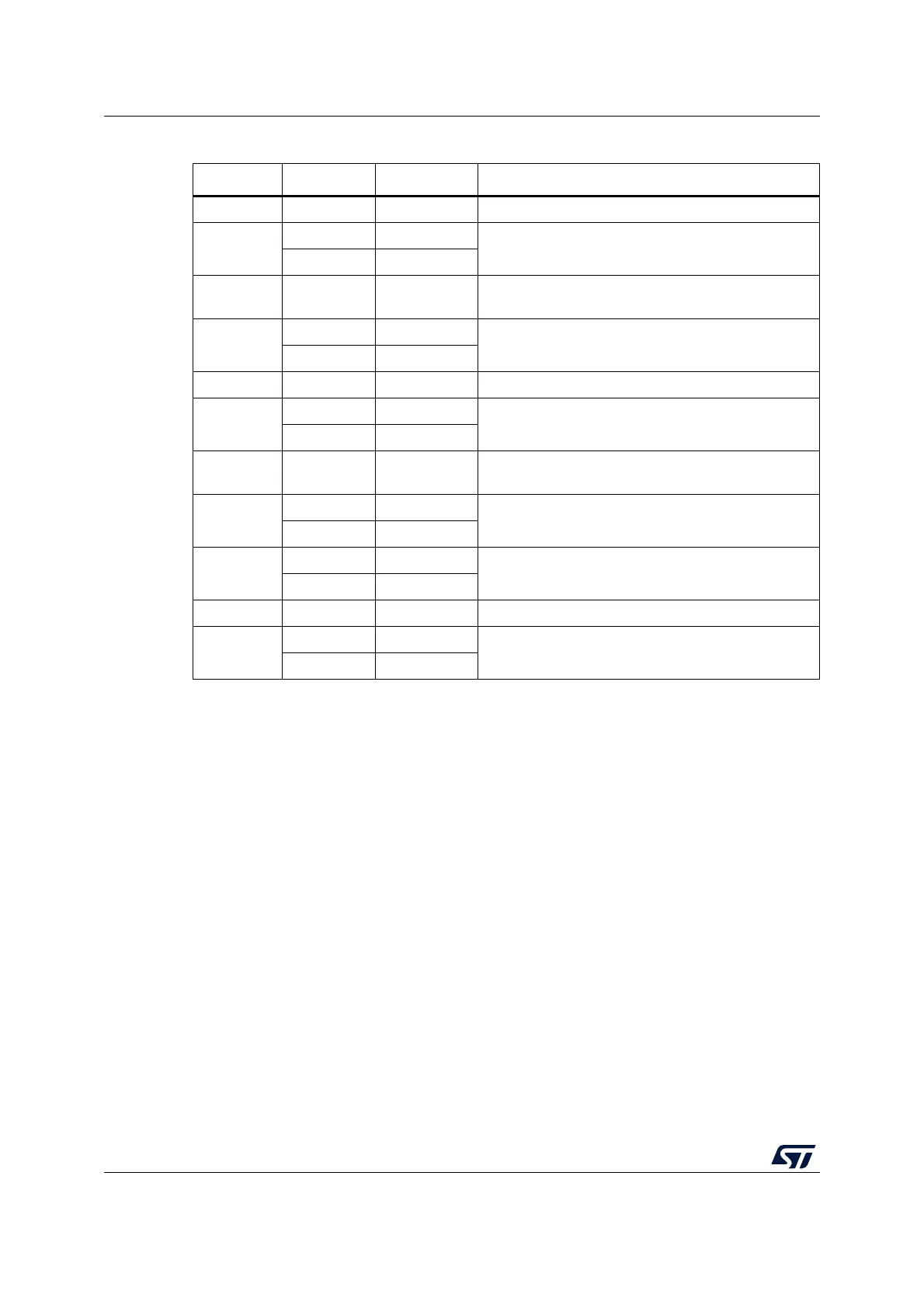

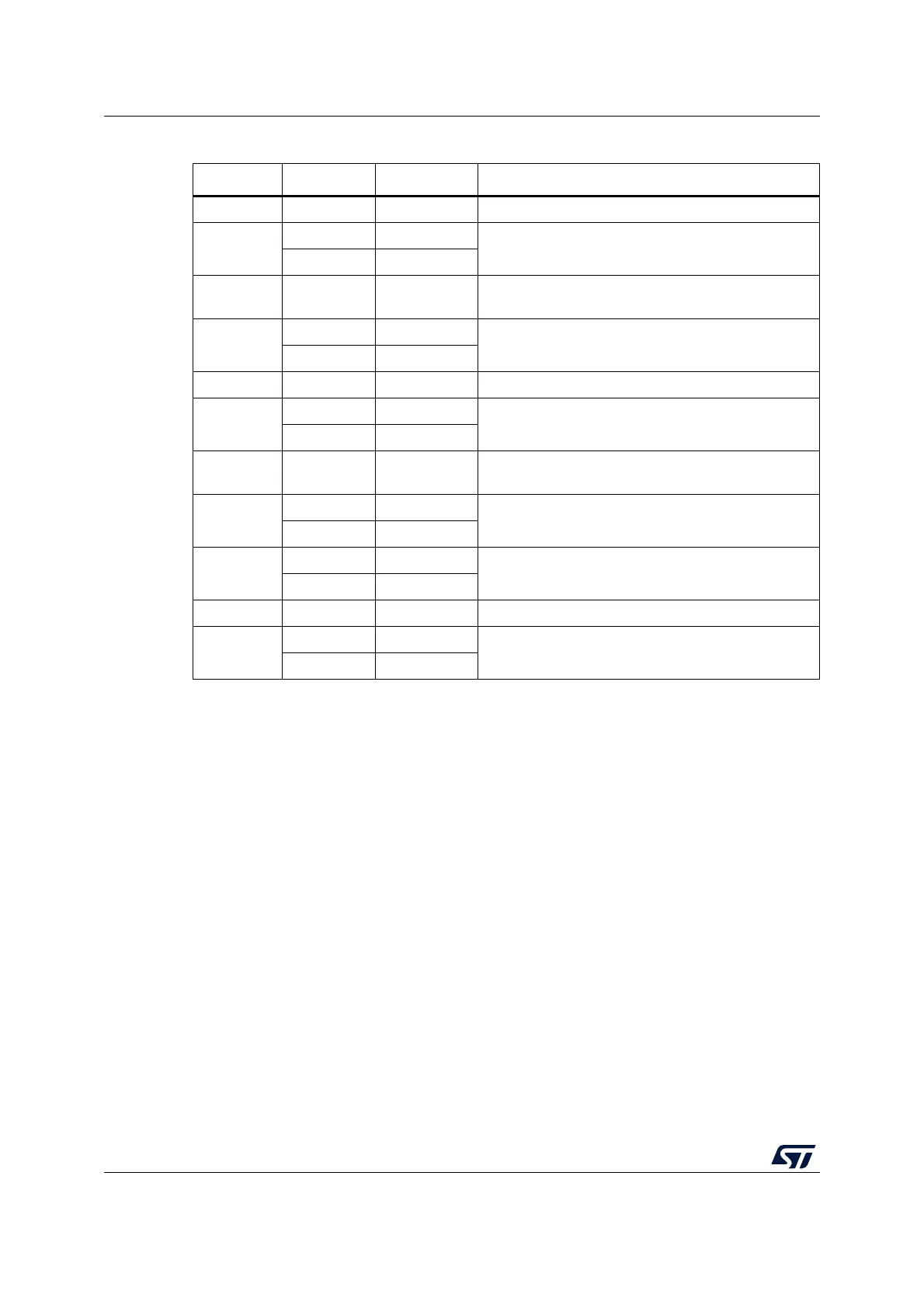

Table 243. Error handling timing parameters

Time RXTOL ms Description

T

s

x 0 Bit start event.

T

1

10.3

The earliest time for a low - high transition when

indicating a logical 1.

00.4

T

n1

x0.6

The nominal time for a low - high transition when

indicating a logical 1.

T

2

00.8

The latest time for a low - high transition when

indicating a logical 1.

10.9

T

ns

x 1.05 Nominal sampling time.

T

3

11.2

The earliest time a device is permitted return to a high

impedance state (logical 0).

01.3

T

n0

x1.5

The nominal time a device is permitted return to a

high impedance state (logical 0).

T

4

01.7

The latest time a device is permitted return to a high

impedance state (logical 0).

11.8

T

5

11.85

The earliest time for the start of a following bit.

02.05

T

nf

x 2.4 The nominal data bit period.

T

6

02.75

The latest time for the start of a following bit.

12.95

Loading...

Loading...