General-purpose timers (TIM2/TIM3/TIM4) RM0444

696/1390 RM0444 Rev 5

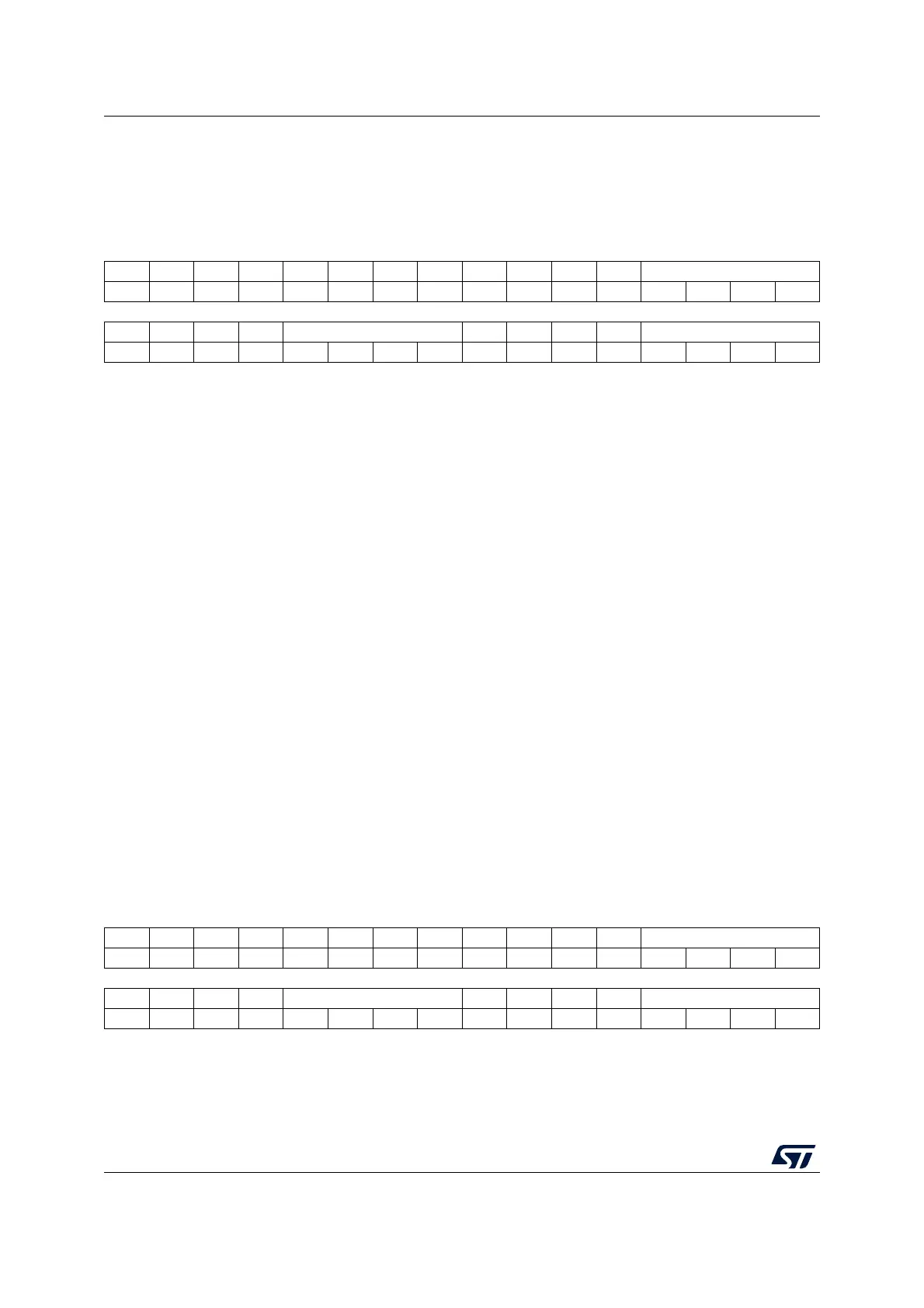

22.4.28 TIM2 timer input selection register (TIM2_TISEL)

Address offset: 0x68

Reset value: 0x0000 0000

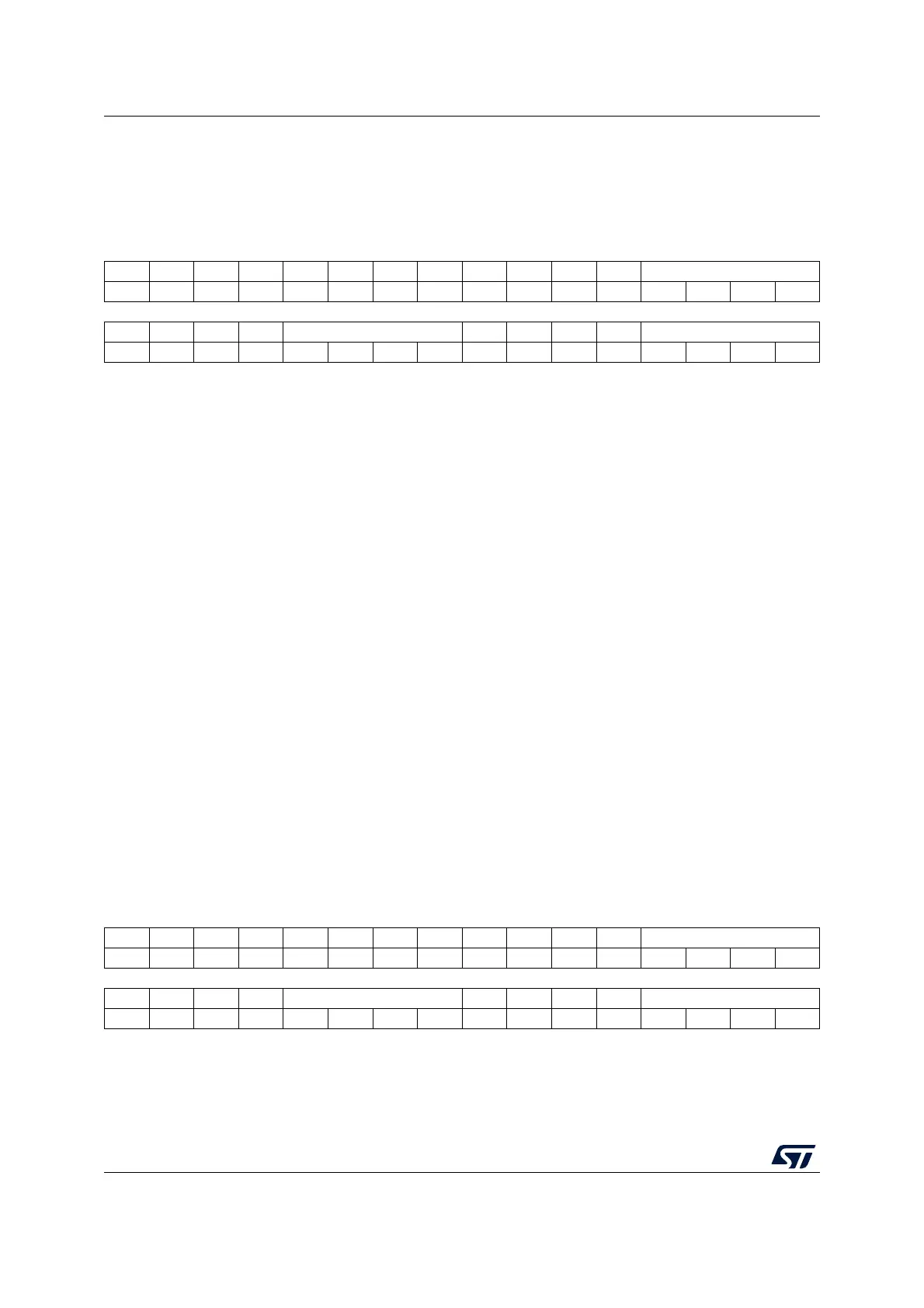

22.4.29 TIM3 timer input selection register (TIM3_TISEL)

Address offset: 0x68

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TI3SEL[3:0]

rw rw rw rw

1514131211109876543210

Res. Res. Res. Res. TI2SEL[3:0] Res. Res. Res. Res. TI1SEL[3:0]

rw rw rw rw rw rw rw rw

Bits 31:20 Reserved, must be kept at reset value.

Bits 19:16 TI3SEL[3:0]: TI3[0] to TI3[15] input selection

These bits select the TI3[0] to TI3[15] input source.

0000: TIM2_CH3 input

0001: COMP3 output

Others: Reserved

Note: Available on STM32G0B1xx and STM32G0C1xx salestypes only, otherwise reserved.

Bits 15:12 Reserved, must be kept at reset value.

Bits 11:8 TI2SEL[3:0]: TI2[0] to TI2[15] input selection

These bits select the TI2[0] to TI2[15] input source.

0000: TIM2_CH2 input

0001: COMP2 output

Others: Reserved

Bits 7:4 Reserved, must be kept at reset value.

Bits 3:0 TI1SEL[3:0]: TI1[0] to TI1[15] input selection

These bits select the TI1[0] to TI1[15] input source.

0000: TIM2_CH1 input

0001: COMP1 output

Others: Reserved

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. TI3SEL[3:0]

rw rw rw rw

1514131211109876543210

Res. Res. Res. Res. TI2SEL[3:0] Res. Res. Res. Res. TI1SEL[3:0]

rw rw rw rw rw rw rw rw

Loading...

Loading...