RM0444 Rev 5 197/1390

RM0444 Reset and clock control (RCC)

220

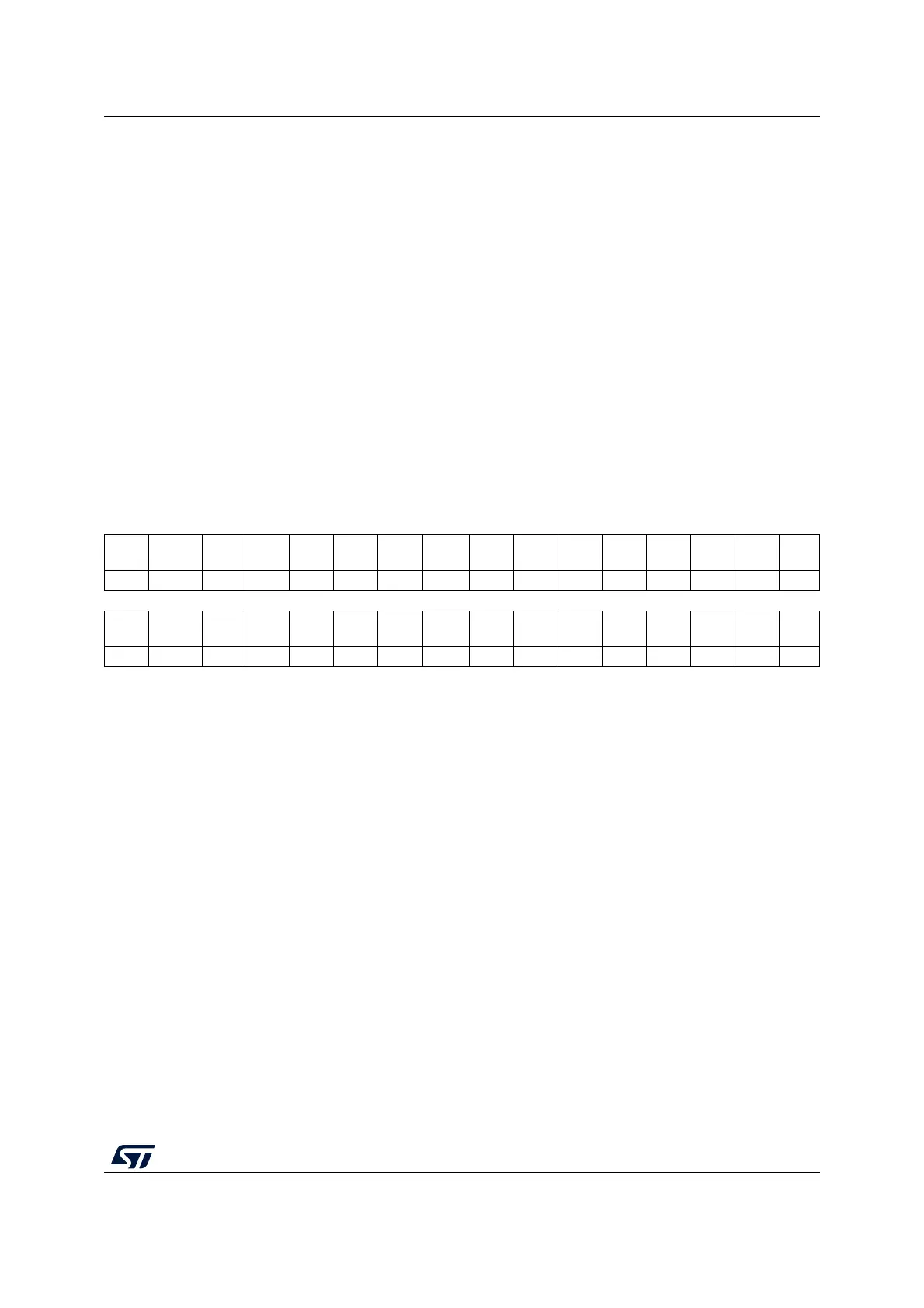

5.4.14 AHB peripheral clock enable register (RCC_AHBENR)

Address offset: 0x38

Reset value: 0x00000 0100

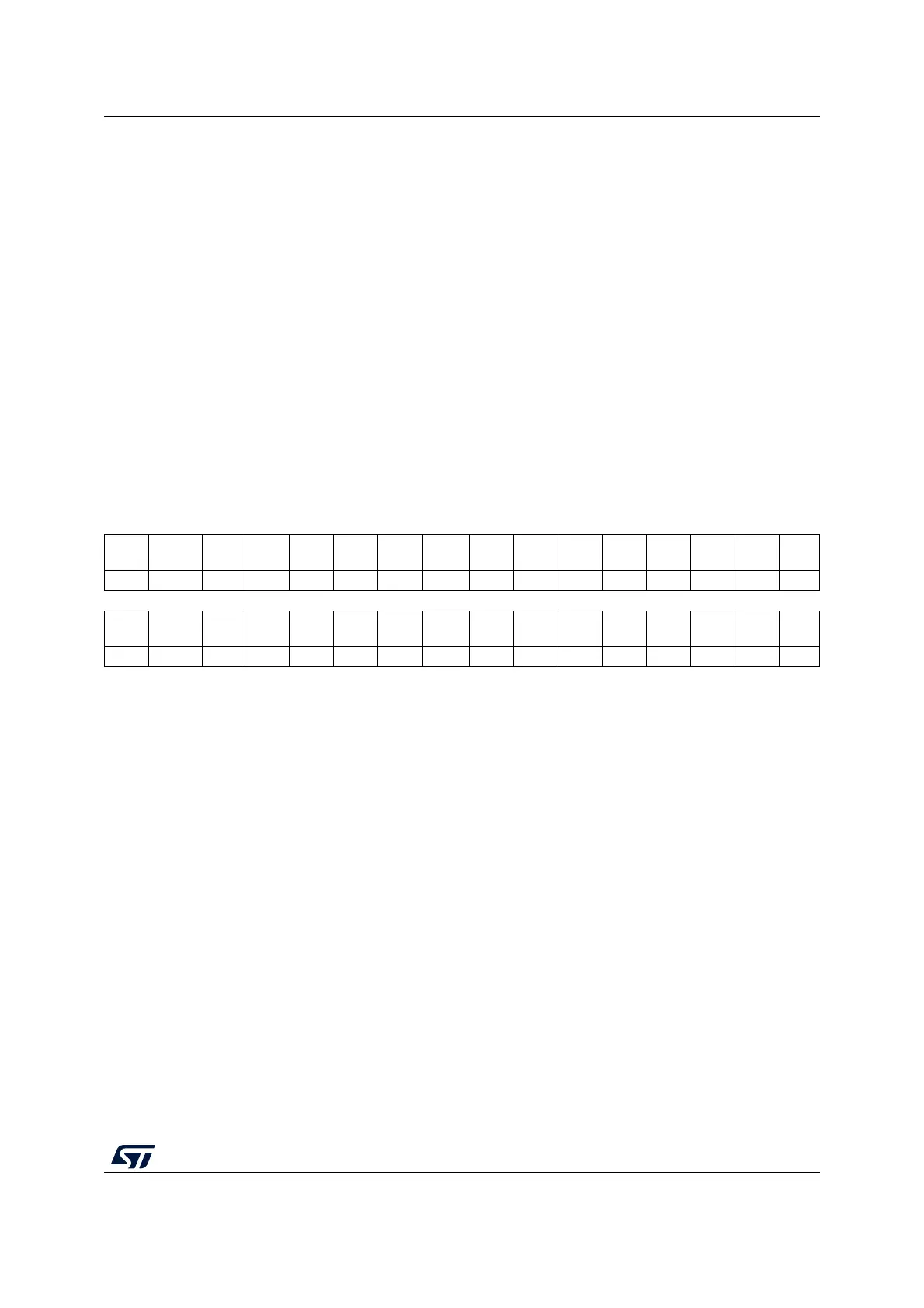

Bit 2 GPIOCEN: I/O port C clock enable

This bit is set and cleared by software.

0: Disable

1: Enable

Bit 1 GPIOBEN: I/O port B clock enable

This bit is set and cleared by software.

0: Disable

1: Enable

Bit 0 GPIOAEN: I/O port A clock enable

This bit is set and cleared by software.

0: Disable

1: Enable

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

RNG

EN

(1)

Res.

AES

EN

(1)

rw rw

1514131211109 8 76543210

Res. Res. Res.

CRC

EN

Res. Res. Res.

FLASH

EN

Res. Res. Res. Res. Res. Res.

DMA2

EN

(1)

DMA1

EN

rw rw rw rw

1. Only significant on devices integrating the corresponding peripheral, otherwise reserved. Refer to Section 1.4: Availability

of peripherals.

Bits 31:19 Reserved, must be kept at reset value.

Bit 18 RNGEN: Random number generator clock enable

(1)

Set and cleared by software.

0: Disable

1: Enable

Bit 17 Reserved, must be kept at reset value.

Bit 16 AESEN: AES hardware accelerator

(1)

Set and cleared by software.

0: Disable

1: Enable

Bits 15:13 Reserved, must be kept at reset value.

Bit 12 CRCEN: CRC clock enable

Set and cleared by software.

0: Disable

1: Enable

Bits 11:9 Reserved, must be kept at reset value.

Loading...

Loading...