Reset and clock control (RCC) RM0444

198/1390 RM0444 Rev 5

5.4.15 APB peripheral clock enable register 1 (RCC_APBENR1)

Address offset: 0x3C

Reset value: 0x0000 0000

Bit 8 FLASHEN: Flash memory interface clock enable

Set and cleared by software.

0: Disable

1: Enable

This bit can only be cleared when the Flash memory is in power down mode.

Bits 7:2 Reserved, must be kept at reset value.

Bit 1 DMA2EN: DMA2 and DMAMUX clock enable

(1)

Set and cleared by software.

0: Disable

1: Enable

DMAMUX is enabled as long as at least one DMA peripheral is enabled.

Bit 0 DMA1EN: DMA1 and DMAMUX clock enable

Set and cleared by software.

0: Disable

1: Enable

DMAMUX is enabled as long as at least one DMA peripheral is enabled.

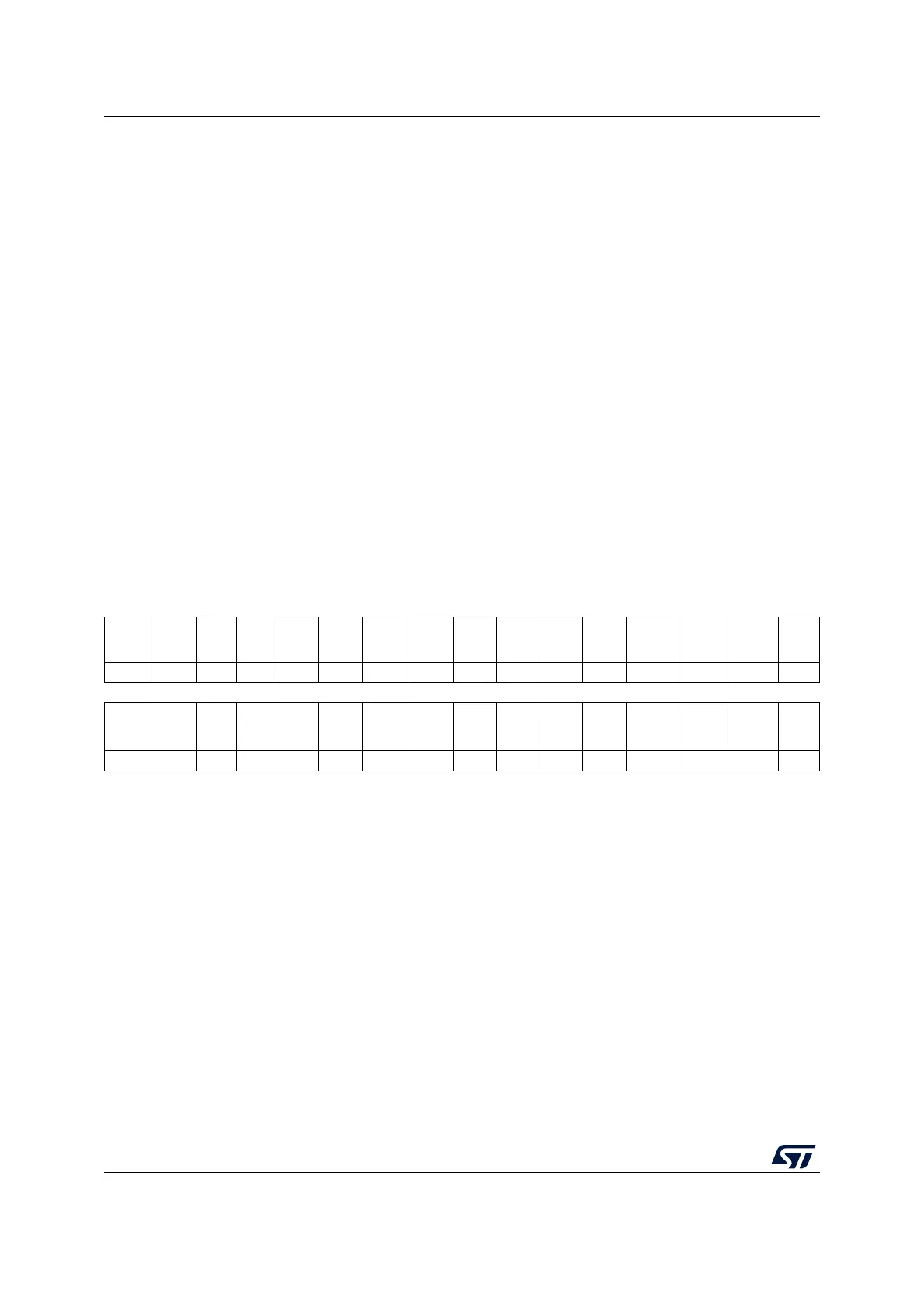

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

LPTIM1

EN

LPTIM2

EN

DAC1

EN

PWR

EN

DBG

EN

UCPD2

EN

UCPD1

EN

CEC

EN

I2C3

EN

(1)

I2C2

EN

I2C1

EN

LP

UART1

EN

USART4

EN

(1)

USART3

EN

(1)

USART2

EN

CRSE

N

(1)

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

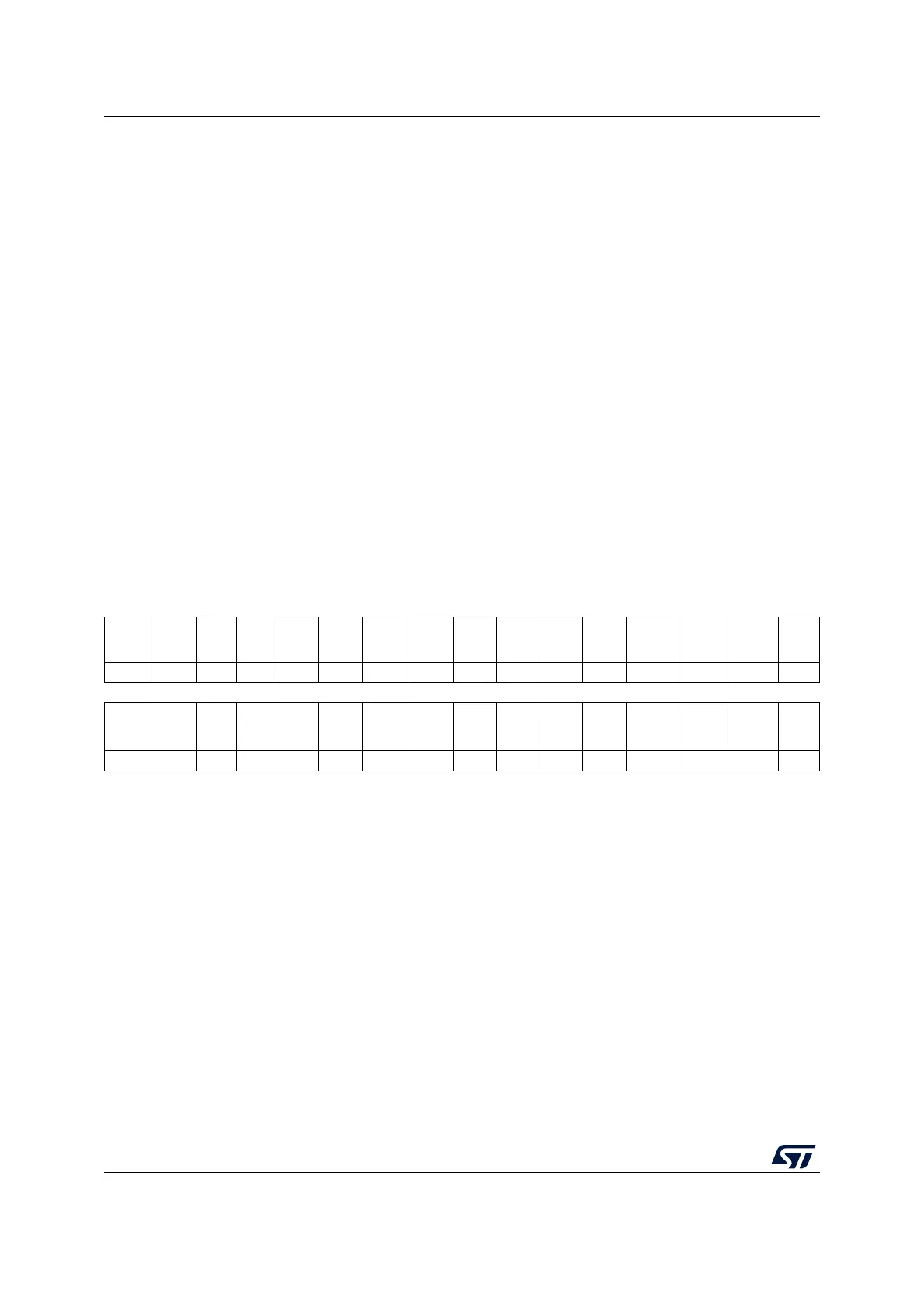

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SPI3

EN

(1)

SPI2

EN

USB

EN

(1)

FDCA

N

EN

(1)

WWDG

EN

RTC

APB

EN

USART

6

EN

(1)

USART

5

EN

(1)

LP

UART2

EN

(1)

Res.

TIM7

EN

(1)

TIM6

EN

(1)

Res.

TIM4

EN

(1)

TIM3

EN

TIM2

EN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1. Only significant on devices integrating the corresponding peripheral, otherwise reserved. Refer to Section 1.4: Availability

of peripherals.

Bit 31 LPTIM1EN: LPTIM1 clock enable

Set and cleared by software.

0: Disable

1: Enable

Bit 30 LPTIM2EN: LPTIM2 clock enable

Set and cleared by software.

0: Disable

1: Enable

Bit 29 DAC1EN: DAC1 interface clock enable

Set and cleared by software.

0: Disable

1: Enable

Loading...

Loading...