Extended interrupt and event controller (EXTI) RM0444

332/1390 RM0444 Rev 5

13.5.12 EXTI CPU wakeup with interrupt mask register (EXTI_IMR1)

Address offset: 0x080 (EXTI_IMR1)

Reset value: 0xFFF8 0000

Contains register bits for configurable events and direct events.

The reset value is set such as to, by default, enable interrupt from direct lines, and disable

interrupt from configurable lines.

13.5.13 EXTI CPU wakeup with event mask register (EXTI_EMR1)

Address offset: 0x084 (EXTI_EMR1)

Reset value: 0x0000 0000

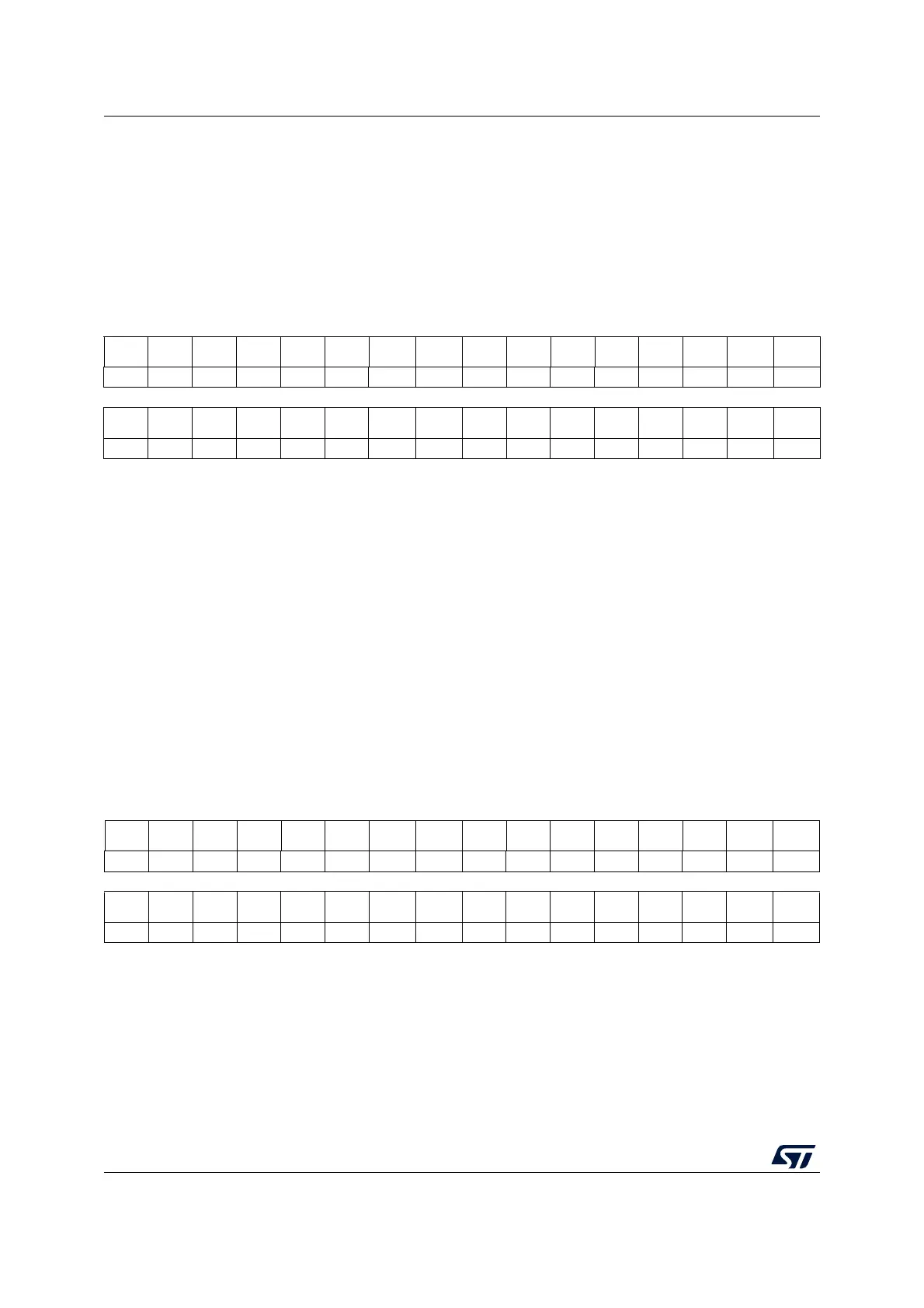

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

IM31 IM30 IM29 IM28 IM27 IM26 IM25 IM24 IM23 IM22 IM21 IM20 IM19 IM18 IM17 IM16

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109 8 7654321 0

IM15 IM14 IM13 IM12 IM11 IM10 IM9 IM8 IM7 IM6 IM5 IM4 IM3 IM2 IM1 IM0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 IMx: CPU wakeup with interrupt mask on line x (x = 31 to 0)

Setting/clearing each bit unmasks/masks the CPU wakeup with interrupt, by an event on the

corresponding line.

0: wakeup with interrupt masked

1: wakeup with interrupt unasked

The IM24, IM22 and IM20 bits are only available in STM32G0B1xx and STM32G0C1xx.

They are reserved in STM32G031xx and STM32G041xx as well as STM32G051xx and

STM32G061xx as well as STM32G071xx and STM32G081xx.

The IM27, IM18 and IM17 bits are only available in STM32G071xx and STM32G081xx as

well as STM32G0B1xx and STM32G0C1xx. They are reserved in STM32G031xx and

STM32G041xx as well as STM32G051xx and STM32G061xx.

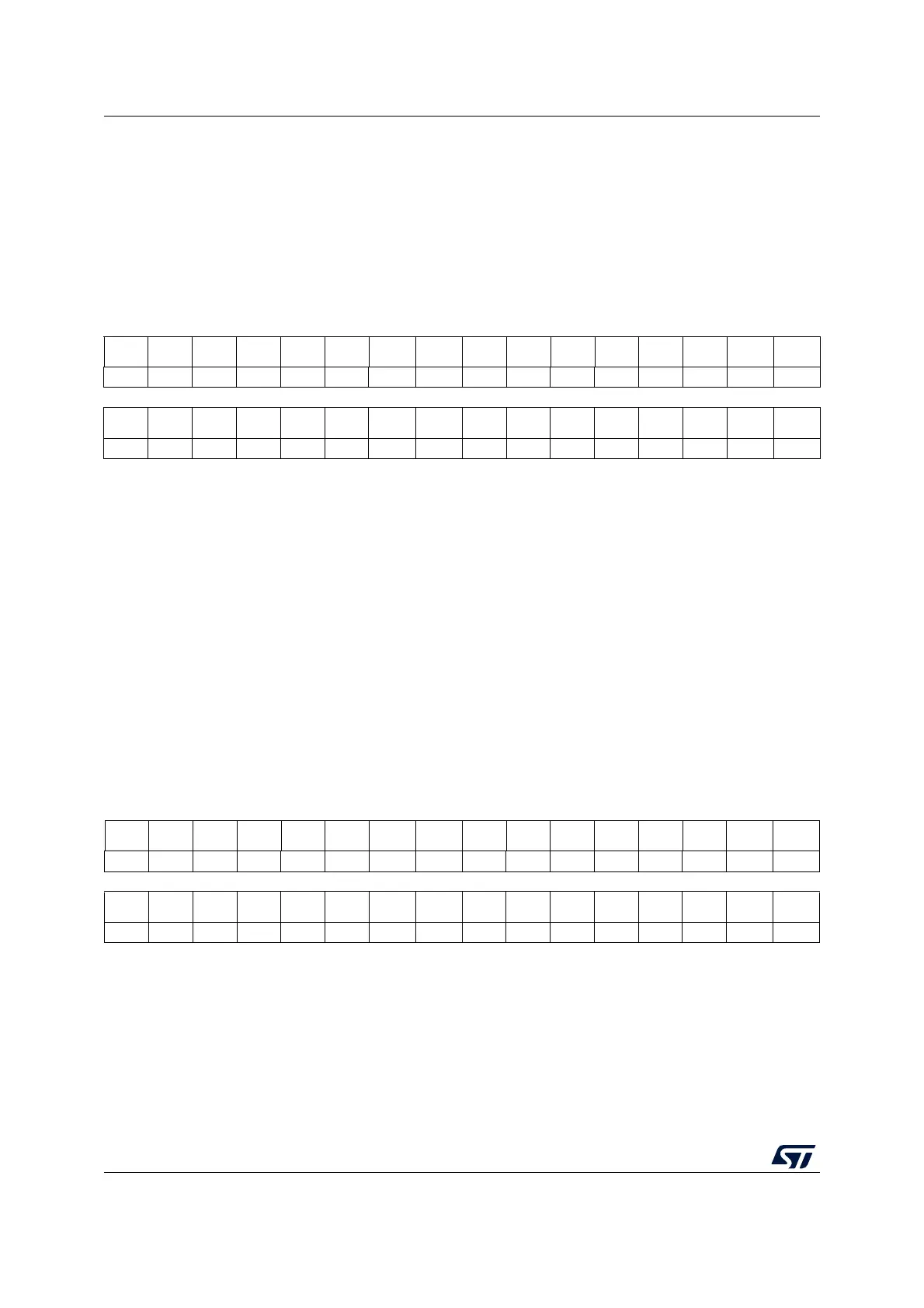

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

EM31 EM30 EM29 EM28 EM27 EM26 EM25 EM24 EM23 EM22 EM21 EM20 EM19 EM18 EM17 EM16

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

EM15 EM14 EM13 EM12 EM11 EM10 EM9 EM8 EM7 EM6 EM5 EM4 EM3 EM2 EM1 EM0

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 EMx: CPU wakeup with event generation mask on line x (x = 31 to 0)

Setting/clearing each bit unmasks/masks the CPU wakeup with event generation on the

corresponding line.

0: wakeup with event generation masked

1: wakeup with event generation unmasked

The EM24, EM22 and EM20 bits are only available in STM32G0B1xx and STM32G0C1xx.

They are reserved in STM32G031xx and STM32G041xx as well as STM32G051xx and

STM32G061xx as well as STM32G071xx and STM32G081xx.

Loading...

Loading...